CMOS反相器

cmos反相器信号再生

CMOS反相器信号再生概述CMOS反相器信号再生是一种利用CMOS反相器来恢复信号完整性的技术。

CMOS反相器是一种基本的数字电路,它由两个互补的金属氧化物半导体(CMOS)晶体管组成。

当输入信号为高电平时,上拉晶体管导通,下拉晶体管截止,输出信号为低电平。

当输入信号为低电平时,上拉晶体管截止,下拉晶体管导通,输出信号为高电平。

原理CMOS反相器信号再生的原理是利用CMOS反相器的非线性特性。

当输入信号的幅度低于CMOS反相器的阈值电压时,CMOS反相器不导通,输出信号为零。

当输入信号的幅度高于CMOS反相器的阈值电压时,CMOS反相器导通,输出信号为电源电压。

这种非线性特性可以用来恢复信号的完整性。

应用CMOS反相器信号再生技术广泛应用于数字电路中,例如:时钟信号再生:CMOS反相器可以用来再生时钟信号。

时钟信号是数字电路中非常重要的信号,它用于同步电路的运行。

由于时钟信号在传输过程中可能会受到噪声和干扰的影响,导致信号失真。

CMOS反相器可以用来恢复时钟信号的完整性,确保电路的正常运行。

数据信号再生:CMOS反相器可以用来再生数据信号。

数据信号是数字电路中传输信息的信号。

由于数据信号在传输过程中可能会受到噪声和干扰的影响,导致信号失真。

CMOS反相器可以用来恢复数据信号的完整性,确保信息的正确传输。

模拟信号再生:CMOS反相器可以用来再生模拟信号。

模拟信号是连续变化的信号,它可以表示各种物理量。

由于模拟信号在传输过程中可能会受到噪声和干扰的影响,导致信号失真。

CMOS反相器可以用来恢复模拟信号的完整性,确保信息的正确传输。

优点CMOS反相器信号再生技术具有以下优点:简单:CMOS反相器信号再生电路非常简单,只需要几个晶体管就可以实现。

低功耗:CMOS反相器信号再生电路的功耗非常低,非常适合于电池供电的设备。

高速度:CMOS反相器信号再生电路的速度非常快,可以用于高速数字电路。

抗噪声能力强:CMOS反相器信号再生电路具有很强的抗噪声能力,可以有效地抑制噪声和干扰的影响。

cmos反相器工作原理

cmos反相器工作原理CMOS反相器是一种常用的数字逻辑门电路,由一对互补MOSFET(MOS 场效应晶体管)组成。

它的核心组成部件是P型MOS和N型MOS管,具体工作原理如下:1.P型MOS管(PMOS):PMOS管是一种具有P型沟道的器件。

它的沟道是由N型衬底掺入的P型材料构成的。

当PMOS上的栅极电压低于临界值时,沟道形成,并且电流可以流过沟道。

当PMOS上的栅极电压高于临界值时,沟道被截断,电流无法流过。

2.N型MOS管(NMOS):NMOS管是一种具有N型沟道的器件。

它的沟道是由P型衬底掺入的N型材料构成的。

当NMOS上的栅极电压高于临界值时,沟道形成,并且电流可以流过沟道。

当NMOS上的栅极电压低于临界值时,沟道被截断,电流无法流过。

在CMOS反相器中,一个PMOS管和一个NMOS管被连接在一起,形成一个互补对。

它们的栅极由同一个输入控制,且互补对电源共享。

工作原理如下:1.输入为高电平时:当输入为高电平(逻辑1)时,输入端的电压被传递到NMOS管的栅极。

其结果是NMOS管导通,沟道形成。

同时,输入端的高电平也被送到PMOS管的栅极,但由于PMOS管的特性,栅极电压为高电平时导致PMOS管截断,沟道断开。

因此,在输入为高电平时,NMOS导通,PMOS截断,输出为低电平(逻辑0)。

2.输入为低电平时:当输入为低电平(逻辑0)时,NMOS的栅极电压为低电平,导致NMOS截断,沟道断开。

与此同时,输入低电平也传递到PMOS的栅极。

由于PMOS的特性,低电平导致PMOS导通,沟道形成。

因此,在输入为低电平时,NMOS截断,PMOS导通,输出为高电平(逻辑1)。

通过这种方式,输入的逻辑电平被反转,从而实现了反相器的功能。

CMOS反相器的优点之一是功耗较低。

因为在输入为逻辑1时只有一个NMOS导通,输入为逻辑0时只有一个PMOS导通,其他管子都是截断的,消耗的功率非常小。

此外,CMOS反相器还具有高噪声抑制能力和较高的输入阻抗。

COMS反相器原理

Y

VDD

B

图3-5-14 带缓冲级的与非门

A

上述电路虽然简单;但存在一些严重缺点: 1 输出电阻受输入端状态的影响; 2 当输入端数目增多时;输出低电平也随着相应提高;使低电平噪声容限降低

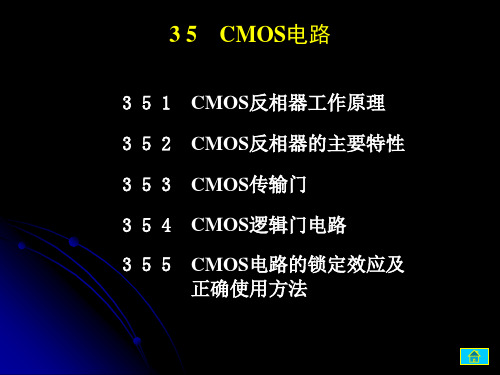

3 5 CMOS电路

3 5 1 CMOS反相器工作原理

3 5 2 CMOS反相器的主要特性

3 5 3 CMOS传输门

3 5 4 CMOS逻辑门电路

3 5 5 CMOS电路的锁定效应及 正确使用方法

图351 CMOS反相器

D

G

S

S

G

D

vO

VDD

TL

T0

vI

3 5 1 CMOS反相器工作原理

CMOS反相器由一个P沟道增强型MOS管和一个N沟道增强型MOS管串联组成 通常P沟道管作为负载管;N沟道管作为输入管

第一种形式: 在反相器基础上增加一对P沟道T'P和N沟道T'N MOS管 当控制端为1时;T'P和T'N同时截止;输出呈高阻态;当控制端为0时;T'P和T'N同时导通;反相器正常工作 该电路为低电平有效的三态输出门

EN

图3516 三态输出CMOS门结构之二

A

Y

VDD

≥1

TN

TP

A

Y

&

TN

当输入vI为高电平时;负载管截止;输入管导通;负载电流IOL灌入输入管;如图356 所示 灌入的电流就是N沟道管的iDS;输出特性曲线如图357 所示 输出电阻的大小与vGSNvI有关;vI越大;输出电阻越小;反相器带负载能力越强

cmos反相器的工作原理

cmos反相器的工作原理

CMOS反相器的工作原理是基于CMOS(互补金属氧化物半导体)技术的电路。

CMOS反相器是一种用于取反输入信号的数字电路。

它由一对互补型MOSFET

(金属氧化物半导体场效应晶体管)组成,包括一个P型MOSFET和一个N型MOSFET。

CMOS反相器的输入端连接到P型MOSFET的栅极,同时也连接到N型MOSFET的栅极。

而输出端则连接到两个MOSFET的源极之间。

其中,P型MOSFET的源极连接到正电源(VDD),而N型MOSFET的源极连接到地。

当输入端的电压为高电平(逻辑1)时,P型MOSFET的栅极电压低于P型MOSFET的阈值电压,导致P型MOSFET处于关闭状态,不导通。

与此同时,N

型MOSFET的栅极电压高于N型MOSFET的阈值电压,导致N型MOSFET处于

导通状态。

当输入端的电压为低电平(逻辑0)时,P型MOSFET的栅极电压高于P型MOSFET的阈值电压,导致P型MOSFET处于导通状态。

与此同时,N型MOSFET的栅极电压低于N型MOSFET的阈值电压,导致N型MOSFET处于关

闭状态,不导通。

根据上述工作原理,当输入端为高电平时,输出端会产生低电平(逻辑0)的

信号;当输入端为低电平时,输出端会产生高电平(逻辑1)的信号。

因此,CMOS反相器能够将输入信号取反输出。

CMOS反相器具有低功耗、高噪声容忍度和良好的抗干扰能力等优点,因此被

广泛应用于数字逻辑电路和微处理器中。

它在现代电路设计中起着重要的作用,帮助实现数字电路中的信号处理和逻辑功能。

CMOS反相器的分析与设计

CMOS反相器的分析与设计CMOS反相器由一对互补金属氧化物半导体场效应晶体管(n型MOSFET和p型MOSFET)组成。

n型MOSFET和p型MOSFET分别由n型沟道和p型沟道构成。

它们的沟道接在一起,形成一个共用的沟道。

根据输入电压的高低,CMOS反相器能够在输出端产生相反的电平。

CMOS反相器的工作原理是利用MOSFET的负阈值特性,即当输入电压高于一些阈值电压时,MOSFET处于关断状态;当输入电压低于阈值电压时,MOSFET处于导通状态。

CMOS反相器由这两个互补的MOSFET构成,保证了输入电压上升时一个MOSFET关闭,另一个MOSFET打开,输出电压下降;输入电压下降时,一个MOSFET打开,另一个MOSFET关闭,输出电压上升。

这样就实现了电平的反转。

1.确定输入输出电平:根据电路的需求,确定输入输出电平的高低电压范围,并根据具体电路的工作电压确定电源电压。

2.选择适当的MOSFET:根据设计要求,选择合适的n型MOSFET和p 型MOSFET,以满足工作电流和电压要求。

3.确定电阻参数:根据MOSFET的特性,选择合适的电阻参数来限制输入电流和确定电路的放大倍数。

4.确定电容参数:根据电路的带宽要求,确定输入和输出端的负载电容。

5.确定工作频率:根据电路的工作频率要求,确定MOSFET的开启和关闭时间。

6.进行电路仿真:通过电路仿真软件,验证设计的正确性和性能。

CMOS反相器的设计可以通过电路仿真软件如LTSpice来实现。

首先,根据设计要求选择适当的MOSFET,并确定电源电压和电阻电容参数。

然后,通过电路仿真软件搭建CMOS反相器电路,并进行仿真分析。

通过观察输入电压和输出电压的波形曲线,验证电路的正确性和性能。

如果需要进一步优化电路性能,可以通过调整各个元器件的参数来实现。

总结起来,CMOS反相器是一种常见的数字逻辑门电路,利用MOSFET的特性来实现输入输出电平的反转。

CMOS反相器的概述

CMOS反相器的概述CMOS反相器是一种非常常用的逻辑门,可以进行数字信号的反相操作。

CMOS反相器由CMOS技术制造而成,具有低功耗、高可靠性和低噪声的特点。

在数字电路中,CMOS反相器被广泛应用于时序电路、计数器、存储器等模块。

CMOS反相器的基本结构包括一个N型MOS管和一个P型MOS管,N型管和P型管的栅极通过逻辑信号控制,当输入信号为高电平时,N型管导通,P型管截断;当输入信号为低电平时,N型管截断,P型管导通。

这样,输出信号就与输入信号相反,实现了信号的反相操作。

CMOS反相器的输入和输出特性非常重要。

在CMOS反相器中,输入和输出电平可以区分为三个状态:高电平、低电平和开路状态。

当输入电平为高电平时,即逻辑1时,N型管导通,输出电平为低电平,即逻辑0;当输入电平为低电平时,即逻辑0时,P型管导通,输出电平为高电平,即逻辑1;当输入电平为开路状态时,即逻辑Z,输出电平保持上一个状态。

CMOS反相器的优点在于其低功耗和高可靠性。

由于CMOS技术将N型和P型管结合在一起,只有当输入信号改变时才会有电流流动。

在不改变输入信号时,CMOS反相器几乎不消耗功耗。

此外,由于N型和P型管分别负责导通和截断,CMOS反相器对噪声和电压干扰的抵抗能力较强,能够提供稳定的输出信号。

另外,CMOS反相器还具有较高的噪声容限和抗串扰能力。

在数字电路中,信号的传输会产生一定的噪声和串扰,这会导致信号的失真和误差。

CMOS反相器在设计上减小了管子之间的互感和电路之间的耦合,使其能够在抗噪声和抗串扰方面有较好的性能。

这使得CMOS反相器能够适应较严苛的工作环境,提供可靠的信号处理能力。

尽管CMOS反相器具有许多优点,但它也存在一些问题。

首先,由于CMOS反相器采用两个互补型MOS管连接而成,因此在制造过程中需要精心控制各项参数,如电流、阈值电压等,这使得制造过程复杂,成本较高。

此外,CMOS反相器在频率较高的应用中,存在一定的延迟和功耗问题,因此在高速和高频率应用中需要进行相应的优化和补偿。

反相器

PMOS sat

1.5

NMOS res

1

PMOS sat

NMOS res

PMOS off

0.5

0.5

1

1.5

2

2.5

V in

图5.5 由图5.4(VDD=2.5V)推导出的CMOS反相器的VTC

CMOS反相器. 10

2021年4月8日10时59分

CMOS 反相器:动态特性的开关模型

门的响应时间是由通过电阻Rp充电电容CL(电阻Rn放电 电容CL)所需要的时间决定的

IDp

IDn

VDSp

Vin = 0 Vin = 1.5

VDSp

IDn

Vin = 0 Vin = 1.5

VGSp = -1 VGSp = -2.5

对X轴求镜面

Vin = VDD + VGSp IDn = -IDp

Vout

平移 VDD Vout = VDD + VDSp

图5.3 将PMOS I-V特性转换至公共坐标系(假设VDD=2.5V)

Vin = 0.5 Vin = 0

Vout

图5.4 静态CMOS反相器中NMOS和PMOS管的负载曲线(VDD=2.5V)

CMOS反相器. 9

2021年4月8日10时59分

CMOS 反相器的 VTC

NMOS off PMOS res Vout

2.5

NMOS sat PMOS res

2

NMOS sat

VDD

VDD

Rp

Vout

CL

Rn

Vout CL

Vin = 0

Vin = V DD

CMOS反相器. 11

图5.6 静态CMOS反相器动态特性的开关模型

cmos反相器多级噪声抑制原理

CMOS反相器多级噪声抑制原理一、概述CMOS反相器是数字电路中常见的基本元件,它由N型MOS和P型MOS场效应晶体管组成。

在数字系统中,CMOS反相器被广泛用于信号的放大、传输和逻辑运算等方面。

然而,由于环境中存在各种形式的噪声,噪声会对CMOS反相器的正常工作产生不利影响。

为了提高CMOS反相器的性能,多级噪声抑制原理被引入其中。

二、多级噪声抑制原理1. 噪声来源在CMOS反相器中,噪声主要来源于以下几个方面:- 热噪声:由于晶体管内部载流子的热运动引起的随机涨落现象导致的噪声;- 断电噪声:由于晶体管内部的空载电流引起的噪声;- 电源噪声:由于电源波动引起的噪声;- 输入信号噪声:来自输入信号的噪声。

2. 多级噪声抑制原理的基本思想多级噪声抑制原理的基本思想是通过多级放大器和滤波器的结合,降低噪声对CMOS反相器的影响,提高系统的信噪比。

在CMOS反相器中,通常采用分级放大器和信号处理器来完成多级噪声抑制。

3. 分级放大器的作用分级放大器主要用于信号的放大和噪声的抑制。

这是因为在放大器中,信号的增益和噪声的增益是不同的,可以通过适当设计放大器的结构和参数,使得信号得到增益,而噪声得到抑制。

4. 信号处理器的作用在CMOS反相器中,信号处理器主要用于对信号进行滤波和去噪,进一步提高系统的信噪比。

信号处理器可以采用数字滤波器、模拟滤波器等方式,根据具体的应用需求和系统性能要求进行选择和设计。

5. 多级噪声抑制原理的实现多级噪声抑制原理的实现需要综合考虑系统的性能指标、电路结构、工艺制程等多个方面的因素。

在设计中需要注意以下几点:- 合理选择放大器和滤波器的结构和参数,以实现信号的增益和噪声的抑制;- 优化电路的布局和布线,以降低电路的噪声敏感度和互相干扰;- 采用先进的工艺制程和技术,以提高电路的性能和可靠性。

6. 多级噪声抑制原理的优势多级噪声抑制原理的优势主要体现在以下几个方面:- 可以有效抑制噪声,提高系统的信噪比;- 可以提高系统的抗干扰能力,提高系统的稳定性和可靠性;- 可以适应不同的应用场景和性能要求,具有灵活性和可扩展性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

N阱形成的主要步骤是:

1、外延层;2、原氧化生长;3、第一层掩膜(N阱注 入);4、N阱注入(高能);5、退火,如下图。外延层 与衬底有完全相同的晶格结构,只是纯度更高晶格缺陷更 少。氧化层的主要 作用是:1、保护表面的外延层免受沾 污;2、阻止在注入过程中对硅片过度损伤;3、作为氧化 屏蔽层,有助于控制注入过程中杂质的注入深度。光刻胶 图形覆盖了硅片上的特定区域,将起保护起来免于离子注 入。离子注入机离化杂质原子,使其加速获得高能,选出 最恰当的元素注入,并聚焦离子成为极窄的一束,最后扫 描使硅片不受光刻胶保护的区域得到均匀掺杂。杂质离子 穿透硅的晶格结构,对其共价原子结构造成损伤,这种损 伤在以后的扩散以及退火步骤中得到修复。

Vdd

p

1 10 0

n管截止,p管导通,输出为“1”

n

0 01 1

CL

n p管同时导通,输出从 “1”“0” p管截止, n管导通,输出为“0”

CMOS反相器工作在两种状态

静止状态 电荷转移状态 (动态)

CMOS反相器的功耗

Vdd

V VDD

1

CL

0

1.当输入信号为0时: 2.当输入信号为VDD时:

一位全加器电路功能设计

A 0 0 1 1 B 0 1 0 1 S 0 1 1 0 C 表达式 0 0 0 1 C=AB 半加器逻辑图及其逻辑符号:

半加器:实现两个一位二进制数加法运算的电路称为半加器。若将A、B分别作为一位 二进制数,S表示A、B相加的“和”,C是相加产生的“进位”,半加器的真值表如表所

源/漏(S/D)注入工艺 为了完成倒掺杂技术,用中等剂量的掺杂稍稍超过LDD的结 深,但是比最初的双阱掺杂的结深浅,上一步形成的侧墙阻止 了注入杂质侵入狭窄的沟道。N+S/D注入的主要步骤是:1、第 七层掩膜(N+S/D注入);2、 N+S/D注入(中等能量)P+S/D 注入的步骤:1、第八层( P+S/D 注入);2、 P+S/D(中等能 量)。在n+S/D注入和P+S/D注入后,硅片在快速退火装置中退 火。快速退火装置能够迅速达到1000℃左右的高温,并在设定 温度保持数秒,这种状态对于阻止结构的扩展以及控制S/D区杂 质的扩散都非常重要。

磷注入

光刻胶

氧化硅

N阱 P+外延层 P+硅衬底

N阱的形成

退火产生4个结果:1、裸露的硅 片表面生长了一层新的阻挡氧化 层;2、高温使得杂质向硅中移动 (扩散);3、注入引起的损伤得 到修复;4杂质原子与硅原子间的 共价键被激活,使得杂质原子成 为晶格结构中的一部分。

浅槽隔离(STI)工艺

浅槽隔离是在衬底上制作晶体管有源区之间隔离区的一种可选工艺,这 一方法在制作亚0.25um器件时尤其有效。主要分为3个步骤:槽刻蚀、氧化 物填充和氧化物平坦化。其中槽刻蚀分为4个步骤:1、隔离氧化层;2、氮 化物淀积;3、第三层掩膜(浅槽隔离);4、STI槽刻蚀,如图。氮化物的作 用有:其一,它是一层坚固的掩膜材料,有助于STI氧化物淀积过程中保护有 源区;其二,它可以在化学机械抛光(CMP)中充当抛光阻挡层。没有光刻 胶保护的区域被离子和强腐蚀性的化学物质刻蚀掉氮化硅、氧化硅以及硅。

考虑扩散区与衬底之间的反向漏电流后,存在较小反向漏电流

随着特征尺寸的减小,漏电流功耗变得不可 忽视,减小漏电流功耗是目前的研究热点之 一。

CMOS 反相器版图

N Well VDD 2l

VDD

PMOS

PMOS In Out

In

Contacts

Out Metal 1

NMOS

Polysilicon

NMOS GND

0

静态功耗

t

输出保持1不变,没有电荷转移 输出保持0不变,没有电荷转移

3.当输入信号从0->1(发生跳变)时:

输出从“1”转变为“0”, 有电荷 转移

动态功耗

CMOS反相器的功耗

静态功耗 PS

输入

Vin Vout

输出

输入

输出

在输入为0或1(VDD)时,两个MOS管中总是一个截止 一个导通,因此没有从VDD到VSS的直流通路,也没有电 流流入栅极,因此其静态电流和功耗几乎为0。

接触(孔)的形成

局部互连(LI)工艺 局部互连是在晶体管以及其他钛硅化物接触之间布金属连接 线。首先要求淀积一层介质薄膜,然后是化学机械抛光、光刻 和钨金属淀积,最后以金属层抛光结束。LI工艺分为LI氧化硅介 质的形成和LI金属的形成。其中制作LI金属的主要步骤是;1、钛 淀积,2、氮化钛淀积;3、钨淀积;4、磨抛钨,如图。

在输入为0或1(VDD)时,两个MOS管中总是一 个截止一个导通,因此没有从VDD到VSS的直流 通路,也没有电流流入栅极,因此其静态电流 和功耗几乎为0。这是CMOS电路低功耗的主要 原因。CMOS电路的最大特点之一是低功耗。

CMOS电路的优点

(1)微功耗。 CMOS电路静态电流很小,约为纳安数量级。 (2)抗干扰能力很强。 输入噪声容限可达到VDD/2。 (3)电源电压范围宽。 多数CMOS电路可在3~18V的电源电压范围 内正常工作。 (4)输入阻抗高。 (5)负载能力强。 CMOS电路可以带50个同类门以上。 (6)逻辑摆幅大。(低电平0V,高电平VDD )

AБайду номын сангаас

=1 B S A a so S

&

C

B

b

co

C

全加器:对两个一位二进制数及来自低位的 “进位”进行相加,产生本位“和”及向高位” 进位“的逻辑电路称为全加器。由此可知,全 加器有三个输入端,两个输出端。

CIN 半加器2 A 半加器1 B

SUM

≥1

COUT

---用RTL描述的一位半加器 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY HADDER IS PORT (A,B:IN STD_LOGIC; SO,CO:OUT STD_LOGIC); END ENTITY HADDER; ARCHITECTURE FH1 OF HADDER IS BEGIN SO<=A XOR B; CO<=A AND B; END ARCHITECTURE FH1; ---或门的逻辑描述 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY MYOR2 IS; PORT(A,B:IN STD_LOGIC; C: OUT STD_LOGIC ); END ENTITY MYOR2; ARCHITECTURE FU1 OF MYOR2 IS BEIGN C<=A OR B; END ARCHITECTURE FU1

互补静态CMOS组合逻辑电路 变换思路:在不减慢进位产生速度的前提下,让“和” 与“进位”产生的子电路之间共享某些逻辑来减少晶体 管数目

CO AB BCi ACi

S A B Ci ABC i ABC i A BCi ABCi

S ABCi C O ( A B Ci )

接触(孔)的形成 接触形成工艺的目的是在所有硅的有源区形成金属接触,这层金属接触可以 使硅和随后淀积的导电材料更加紧密地结合起来。故钛是做金属接触的理想材 料,也是可行的选择。钛的电阻很低,同时能够与硅发生充分反应,并且与二 氧化硅不发生反应,当温度大于700℃时,钛和硅发生反应生成钛的硅化物。钛 和硅不发生反应,因此这两种物质不会发生化学的键合或者物理的聚集,因此 钛能轻易地从二氧化硅表面除去,而不需要额外掩膜。钛的硅化物在所有有源 硅的表面保留下来。钛金属接触的主要步骤是:1、钛淀积;2、退火;3、刻蚀 钛,如图。

CMOS反相器设计制造

CMOS反相 器

Vin Vout

由PMOS和NMOS 所组成的互补型电 路叫做 CMOS

CMOS反相器工作原理

当输入电压Vin为高电平时, PMOS截止,NMOS导通,Vout=0

VOL=0

Vin Vout

当输入电压Vin为低电平时, PMOS导通,NMOS截止, Vout=VDD VOH=VDD

---一位全加器的顶层文件(结构描述) LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY FADDER IS PORT(A,B,CIN:IN STD_LOGIC; SUM,COUT:OUT STD_LOGIC); END ENTITY FADDER; ARCHITECTURE FD1 OF FADDER IS COMPONENT HADDER PORT(A,B:IN STD_LOGIC; S0,C0:OUT STD_LOGIC); END COMPONENT COMPONENT MYOR2 PORT(A,B:IN STD_LOGIC; C:OUT STD_LOGIC); END COMPONENT; SICNAL D E F:STD_LOGIC; BEGIN U1:HADDER PORT MAP(A,B,C0=>D,S0=>E); U2:HADDER PORT MAP(A=>CIN,B=>E,C0=>F,S0=>SUM); U3:MYORR2 PORT MAP(A=>F,B=>D,C=>COUT); END ARCHITECTURE FD1;

MOS反相器的设计

对CMOS反相器: 1.根据VM确定尺寸

VM

VDD VTP VTN K R 1 KR

2.根据上升下降时间相等原则 设计(WP/WN≈2:1)

三态CMOS反相器

S

Vin

Vout

Vin

S

Vout

S

S

符号 电路图

低电平,高阻

用于多个电路模块共 享一条数据总线的情 形