电流镜负载的差分放大器设计

电流镜在ic设计中的应用

电流镜在ic设计中的应用电流镜在IC设计中的应用引言:电流镜是一种重要的电路结构,在集成电路设计中有广泛的应用。

它通过控制电流的大小和方向,实现了电流的放大、比较和稳定等功能。

本文将详细介绍电流镜在IC设计中的应用。

一、电流镜的基本原理电流镜是由两个晶体管组成的电路结构,通常是由一个驱动晶体管和一个负载晶体管构成。

驱动晶体管负责控制电流的大小和方向,而负载晶体管则提供了稳定的电流源。

电流镜的基本原理是通过控制驱动晶体管的输入电压或电流,来控制负载晶体管中的电流。

当驱动晶体管的电流变化时,负载晶体管的电流也会相应变化,从而实现对电流的放大、比较和稳定等功能。

二、电流镜在放大器中的应用电流镜在放大器中常用于输出级或差分放大器中,用来提供稳定的电流源。

在输出级放大器中,电流镜可以将输入信号的电流放大,并通过负载电阻将电流转化为电压输出。

在差分放大器中,电流镜用来控制两个输入信号的电流大小,从而实现差分放大的功能。

电流镜的应用可以提高放大器的增益和线性度,使其在实际应用中更加稳定和可靠。

三、电流镜在比较器中的应用电流镜在比较器中常用于比较两个输入信号的大小,从而判断它们的相对大小关系。

比较器是一种重要的电路结构,常用于模拟信号的转换和数字信号的处理。

电流镜在比较器中的应用可以实现对输入信号的快速比较,并输出相应的比较结果。

通过合理设计电流镜的参数,可以提高比较器的速度和精度,满足不同应用场景的需求。

四、电流镜在稳压器中的应用电流镜在稳压器中常用于提供稳定的电流源,用来保持电路中其他元件的工作电流恒定。

稳压器是一种重要的电路结构,用来实现电源的稳定输出。

电流镜在稳压器中的应用可以提供稳定的工作电流,使稳压器能够在不同负载条件下保持输出电压的稳定性。

通过合理选择电流镜的参数,可以实现高效、高精度的稳压器设计。

结论:电流镜作为一种重要的电路结构,在IC设计中有着广泛的应用。

它通过控制电流的大小和方向,实现了电流的放大、比较和稳定等功能。

差分放大器版图设计

一.绪论1.1差分放大器的概述差分放大器(Differential amplifier),是能把两个输入电压的差值加以放大的电路,也称差动放大器。

这是一种零点漂移很小的直接耦合放大器,常用于直流放大。

它可以是平衡(术语“平衡”意味着差分)输入和输出,也可以是单端(非平衡)输入和输出,常用来实现平衡与不平衡电路的相互转换,是各种集成电路的一种基本单元。

由两个参数特性相同的晶体管用直接耦合方式构成的放大器。

若两个输入端上分别输入大小相同且相位相同的信号时,输出为零,从而克服零点漂移。

适于作直流放大器。

差分放大器是一种将两个输入端电压的差以一固定增益放大的电子放大器,有时简称为“差放”。

差分放大器通常被用作功率放大器(简称“功放”)和发射极耦合逻辑电路(ECL, Emitter Coupled Logic) 的输入级。

差分放大器是普通的单端输入放大器的一种推广,只要将差放的一个输入端接地,即可得到单端输入的放大器。

很多系统在差分放大器的一个输入端输入信号,另一个输入端输入反馈信号,从而实现负反馈。

常用于电机或者伺服电机控制,以及信号放大。

在离散电子学中,实现差分放大器的一个常用手段是差动放大,见于多数运算放大器集成电路中的差分电路。

差分放大器可以用晶体三极管(晶体管)或电子管作为它的有源器件。

输出电压u0=u01-u02,是晶体管T1和T2集电极输出电压u01和u02之差。

当T1和T2的输入电压幅度相等但极性相反,即us1=-us2 时,差分放大器的增益Kd(称差模增益)和单管放大器的增益相等,即Kd≈Rc/re,式中Rc=Rc1=Rc2,re是晶体管的射极电阻。

通常re很小,因而Kd较大。

当us1=us2 ,即两输入电压的幅度与极性均相等时,放大器的输出u0应等于零,增益也等于零。

实际放大电路不可能完全对称,因而这时还有一定的增益。

这种增益称为共模增益,记为Kc。

在实际应用中,温度变化和电源电压不稳等因素对放大作用的影响,等效于每个晶体管的输入端产生了一个漂移电压。

全差分运算放大器设计说明

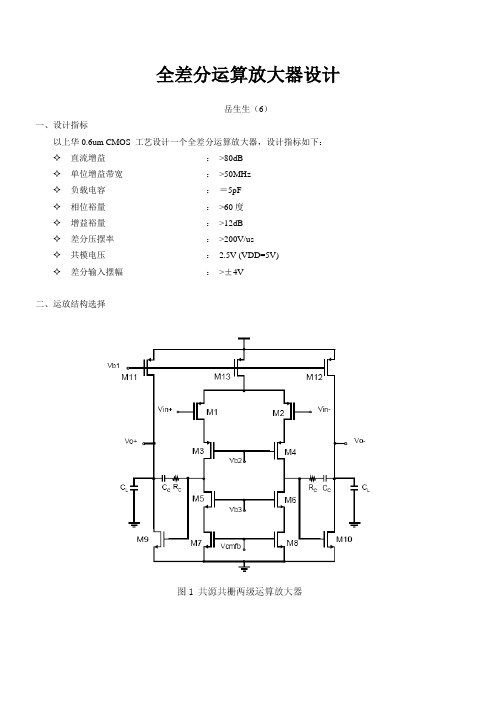

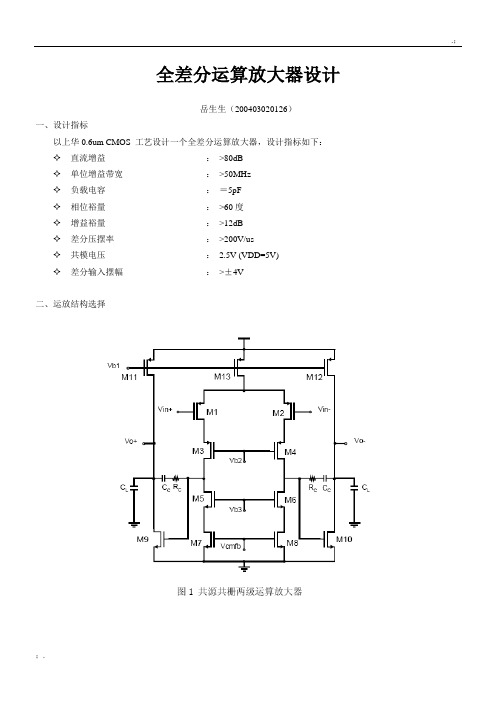

全差分运算放大器设计岳生生(6)一、设计指标以上华0.6um CMOS 工艺设计一个全差分运算放大器,设计指标如下:✧直流增益:>80dB✧单位增益带宽:>50MHz✧负载电容:=5pF✧相位裕量:>60度✧增益裕量:>12dB✧差分压摆率:>200V/us✧共模电压:2.5V (VDD=5V)✧差分输入摆幅:>±4V二、运放结构选择运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。

如图2所示;(b )折叠共源共栅,folded-cascode 。

如图3所示;(c )共源共栅,telescopic 。

如图1的前级所示。

本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的,DSAT NV之和小于0.5V ,输出端的所有PMOS管的,DSAT PV之和也必须小于0.5V 。

对于单级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该要求,因此我们采用两级运算放大器结构。

另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。

考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。

两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。

三、性能指标分析1、 差分直流增益 (Adm>80db)该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12) 第一级增益1351113571135135753()m m m o o o o o m m m m o o o o m m g g gg ggG A R r r r r g g r r r r=-=-=-+P第二级增益92291129911()m o o o m m o o gg G AR r r gg=-=-=-+P整个运算放大器的增益:4135912135753911(80)10m m m m overallo o o o m m o o dB g g g gAA A g g g gr r r r ==≥++2、 差分压摆率 (>200V/us )转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。

差分放大器的设计

差分放大器的设计沈航北方科技学院课程设计说明书课程名称模拟电子技术课程设计教学部工学一部专业测控技术与仪器班级B841401学号B84140117学生姓名刘佳指导教师徐锦丽2010年6月沈航北方科技学院课程设计任务书教学部工学一部专业测控技术与仪器课程设计题目差分放大器的设计班级B841401 学号B84140117 姓名刘佳课程设计时间: 2010 年 6 月21日至2010 年7 月11日课程设计的内容及要求:(一)主要内容设计一个具有恒流源的单端输入-单端输出差分放大器。

要求如下1. 负载电阻R L=20kΩ,输入差模输入电压u id=20mV;2. 差模电压放大倍数A ud>50,输入电阻R id>10kΩ,共模抑制比K CMR>60 dB。

(二)基本要求1. 根据技术指标制定实验方案;在选择器件时,应考虑成本。

2. 根据技术指标通过分析计算确定电路形式和元器件参数;进行实验数据处理和分析。

3. 画出电路原理图(元器件标准化,电路图规范化);验证所设计的电路。

4. 用仿真软件仿真。

5. 按照要求撰写课程设计报告(三)主要参考书1. 童诗白,华成英主编.模拟电子技术基础.[M]北京:高等教育出版社,2006年2. 戴伏生主编.基础电子电路设计与实践.[M]北京:国防工业出版社,2002年3. 谭博学主编.集成电路原理与应用.[M]北京:电子工业出版社,2003年4. 陈光明等主编.电子技术课程设计与综合实训.[M]北京:北京航空航天大学出版社,2007年5. 谢自美主编.电子线路设计·实验·测试.[M]武汉:华中科技大学出版社,2006年6. 华满清主编.电子技术实验与课程设计.[M]北京:机械工业出版社,2005年(四)评语(五)成绩指导教师年月日负责教师年月日摘要:本电路为差分放大电路,主要功能是将输入端输入的差模信号放大后在输出端输出。

本电路主要由两个2n1711(分别为T1、T2)三极管构成对称链接的放大电路,其中两R c1、R c2为等值电阻,R l 为负载电阻,起到一定保护电路的作用。

差分放大器版图设计

一.绪论1.1差分放大器的概述差分放大器(Differ entia l amplif ier),是能把两个输入电压的差值加以放大的电路,也称差动放大器。

这是一种零点漂移很小的直接耦合放大器,常用于直流放大。

它可以是平衡(术语“平衡”意味着差分)输入和输出,也可以是单端(非平衡)输入和输出,常用来实现平衡与不平衡电路的相互转换,是各种集成电路的一种基本单元。

由两个参数特性相同的晶体管用直接耦合方式构成的放大器。

若两个输入端上分别输入大小相同且相位相同的信号时,输出为零,从而克服零点漂移。

适于作直流放大器。

差分放大器是一种将两个输入端电压的差以一固定增益放大的电子放大器,有时简称为“差放”。

差分放大器通常被用作功率放大器(简称“功放”)和发射极耦合逻辑电路(ECL, Emitte r Couple d Logic)的输入级。

差分放大器是普通的单端输入放大器的一种推广,只要将差放的一个输入端接地,即可得到单端输入的放大器。

很多系统在差分放大器的一个输入端输入信号,另一个输入端输入反馈信号,从而实现负反馈。

常用于电机或者伺服电机控制,以及信号放大。

在离散电子学中,实现差分放大器的一个常用手段是差动放大,见于多数运算放大器集成电路中的差分电路。

差分放大器可以用晶体三极管(晶体管)或电子管作为它的有源器件。

输出电压u0=u01-u02,是晶体管T1和T2集电极输出电压u01和u02之差。

当T1和T2的输入电压幅度相等但极性相反,即us1=-us2 时,差分放大器的增益Kd(称差模增益)和单管放大器的增益相等,即Kd≈Rc/re,式中Rc=Rc1=Rc2,re是晶体管的射极电阻。

通常re很小,因而Kd较大。

当us1=us2 ,即两输入电压的幅度与极性均相等时,放大器的输出u0应等于零,增益也等于零。

全差分运算放大器设计

全差分运算放大器设计岳生生(200403020126)一、设计指标以上华0.6um CMOS 工艺设计一个全差分运算放大器,设计指标如下:✧直流增益:>80dB✧单位增益带宽:>50MHz✧负载电容:=5pF✧相位裕量:>60度✧增益裕量:>12dB✧差分压摆率:>200V/us✧共模电压:2.5V (VDD=5V)✧差分输入摆幅:>±4V二、运放结构选择运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。

如图2所示;(b )折叠共源共栅,folded-cascode 。

如图3所示;(c )共源共栅,telescopic 。

如图1的前级所示。

本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的,DSAT NV之和小于0.5V ,输出端的所有PMOS管的,DSAT PV之和也必须小于0.5V 。

对于单级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该要求,因此我们采用两级运算放大器结构。

另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。

考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。

两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。

三、性能指标分析1、 差分直流增益 (Adm>80db)该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12) 第一级增益1351113571135135753()m m m o o o o o m m m m o o o o m m g g gg gg G A R r rr r g g r r r r=-=-=-+第二级增益92291129911()m o o o m m o o gg G AR r rgg=-=-=-+整个运算放大器的增益:4135912135753911(80)10m m m m overallo o o o m m o o dB g g g gAA A g g g gr r r r ==≥++2、 差分压摆率 (>200V/us )转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。

全差分CMOS运算放大器的设计

全差分CMOS运算放大器的设计全差分CMOS运算放大器(Fully Differential CMOS Operational Amplifier)是一种常用于模拟、混合信号和通信电路中的放大器。

全差分运算放大器结合了差分放大器和普通运算放大器的优点,具有更好的共模抑制、抗干扰能力和更高的增益。

1.设计差动放大器:差动放大器是全差分CMOS运算放大器的核心部分,其一般由两个输入差分对和一个负载电阻组成。

在设计差动放大器时,首先需要确定放大器的增益、带宽和功耗等要求。

然后,选择适当的晶体管尺寸和偏置电流来满足这些要求。

2.设计电流镜:电流镜主要用于稳定差动放大器的工作点。

常用的电流镜电路有P型电流镜和N型电流镜。

在设计电流镜时,需要考虑放大器的输入阻抗、输出阻抗和功耗。

3.设计共模反馈电路:共模反馈电路主要用于提高全差分CMOS运算放大器的共模抑制比。

在设计共模反馈电路时,需要确定合适的电压分压比例和电容值,以及选择合适的晶体管尺寸和偏置电流。

4.偏置电流源设计:5.电源设计:6.输入和输出接口设计:7.稳定性分析和优化:在设计全差分CMOS运算放大器时,还需要进行稳定性分析和优化。

常用的稳定性分析技术有迭代法、校正法和频率响应法。

稳定性优化技术有补偿电容法、极点分布法和增益调整法。

8.仿真和验证:最后,设计完成的全差分CMOS运算放大器需要进行仿真和验证。

常用的仿真和验证工具有SPICE软件、电路仿真器和实验测量仪器。

通过仿真和验证,可以评估放大器的性能和电路的可靠性。

最后,需要注意的是,在进行全差分CMOS运算放大器的设计时,应遵循设计规范和标准,如功耗规范、电压规范和噪声规范,以确保设计的可靠性和一致性。

同时,应密切关注工艺制程、温度变化等因素对电路性能的影响,并进行相应的校准和补偿。

全差分放大器设计

对于全差分放大器,一般可以得到更大的swing (由于差分信号),同时可以实现对共模干扰、噪声以及偶数阶的非线性的抑制;但其需要有两个匹配的反馈网络,以及共模反馈电路顺便提一下,对于全差分的折叠共源共栅(folded cascode)放大器,需要注意转换速率(正向与负向)对输入对差分对的尾电流源和cascode电流源的考虑非主极点的位置–输入对管的drain节点(注意全差分没有镜像极点的问题..),如果考虑PMOS输入的结构,将会折叠到n管的cascode,从而减小此节点阻抗,提高此非主极点的频率;但是P输入结构亦有其问题,如直流增益和cmfb电路的速度(考虑cmfb控制的为cascode的pmos电流源)关于共模反馈CMFB从反馈环路来看,共模的稳定问题来源于闭环的共模增益:由于输入差分对的尾电流源的local-feedback,通常共模增益较小,导致运放无法控制其输出共模点;通过CMFB共模反馈电路,可以提高共模反馈环路的增益,以稳定共模信号。

设计CMFB需考虑补偿以减小环路的稳定时间(settling time)和提高稳定性。

从性能上,我们希望共模反馈的单位增益带宽足够大,但由于cmfb的环路相较于差模通路可能有更多高频极点,故此在一定的功耗要求下其UGB一般比较难做的高,有书中提到可以将其设计为差模UGB 的1/3一般共模反馈的方法是控制放大器的电流源,这里如果是folded-cascode的结构,可以考虑用cmfb控制cascode的电流源而不是输入差分对的电流源—-因其在共模环路中有较少的节点–>更容易补偿等..(另一种考虑是控制尾电流源可能导致共模增益的问题)另外,对于cmfb控制的尾电流源,常见将尾电流源分为两半,其中之一由cmfb控制,另一半接恒定偏置电流;这种结构的具体分析可见Gray书12.4.2节的内容,简单来说,single-stage的opamp中控制尾电流源的cmfb结构,其UGB主要为gmt/CL, 其中gmt为尾电流源的跨导,这里拆分尾电流源来减半cmc共模控制的部分,这样UGB减小,即缩减带宽来提升共模反馈环路的相位裕度,当然cmfb的增益相应也减小了;另外恒定偏置部分也可帮助共模电压的初始建立,减小cmfb大的扰动。

差分放大器

差分放大器华侨大学电子工程系IC 工艺及版图设计课程实验(六)模拟电路单元版图布局(2)差分放大器华侨大学厦门专用集成电路系统重点实验室 -2010-IC 工艺及版图设计课程实验七模拟电路单元版图布局-差分放大器一、实验目的1.掌握使用 Cadence Virtuoso XL 版图编辑软件进行模拟 IC 版图布局设计2.掌握两级差分放大器电路版图布局3.通过实验掌握低等精度度匹配(以下简称低度匹配)MOSFET 的布局方法二、实验软件:Cadence IC 5141 Virtuoso Layout XL三、实验要求:实验前请做好预习工作,实验后请做好练习,较熟练地使用Virtuoso 软件对版图进行布局设计,通过实验逐渐掌握低度匹配MOSFET 的布局方法。

IC 工艺及版图设计课程实验六教学任务模拟电路单元版图布局①基准电流源学时 2 专业能力:教学目标 1.熟练掌握版图编辑软件的使用 2.掌握低度匹配 MOSFET 的布局方法 3.掌握两级差分放大器电路的布局教学内容重点难点 1. 低度匹配 MOSFET 布局 2. 两级差分放大器版图布局低度匹配 MOSFET 版图布局低度匹配MOSFET 版图布局华侨大学电子工程系(The Department of Electronic Engineering Huaqiao University)1 华侨大学厦门专用集成电路系统重点实验室第一部分实验演示部分集成电路版图设计是一门技术,它需要设计者具有电路系统原理与工艺制造方面的基础知识。

但是它更需要设计者的创造性、空间想象力和耐性,需要设计者长期工作的经验和知识的积累。

然而集成电路版图设计不仅仅是一门技术,还是一门艺术。

设计出一套符合设计规则的“正确”版图也许并不困难,但是要设计出最大程度体现高性能、低功耗、低成本、性能可靠的芯片版图却不是一朝一夕就能学会的事情。

在设计 CMOS 芯片时,主要的目标是优化芯片尺寸和提高密集度。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

. . . . w. . .v 电流镜负载的差分放大器设计

摘 要 在对单极放大器与差动放大器的电路中,电流源起一个大电阻的作用,但不消耗过多的电压余度。而且,工作在饱和区的MOS器件可以当作一个电流源。 在模拟电路中,电流源的设计是基于对基准电流的“复制”,前提是已经存在一个精确的电流源可以利用。但是,这一方法可能引起一个无休止的循环。一个相对比较复杂的电路被用来产生一个稳定的基准电流,这个基准电流再被复制,从而得到系统中很多电流源。而电流镜的作用就是精确地复制电流而不受工艺和温度的影响。在典型的电流镜中差动对的尾电流源通过一个NMOS镜像来偏置,负载电流源通过一个PMOS镜像来偏置。电流镜中的所有晶体管通常都采用相同的栅长,以减小由于边缘扩散所产生的误差。而且,短沟器件的阈值电压对沟道长度有一定的依赖性。因此,电流值之比只能通过调节晶体管的宽度来实现。而本题就是利用这一原理来实现的。 . . . .

w. . .v 一、设计目标(题目) ............................................................................... 3 二、相关背景知识 .................................................................................... 4 1、单个MOSTFET的主要参数包括: ......................................................... 4 三、设计过程 .......................................................................................... 5 1、电路结构 ...................................................................................... 5 2、主要电路参数的手工推导 .................................................................. 6 3、参数验证(手工推导) ..................................................................... 7 四、电路仿真 .......................................................................................... 7 1、NMOS特性仿真及参数推导 ................................................................ 7 2、PMOS特性仿真及参数推导 ............................................................... 10 3、最小共模输入电压仿真 ................................................................... 13 4、电流镜负载的差分放大器特性仿真及参数推导 ........................................ 15 五、性能指标对比 .................................................................................. 18 六、心得 ............................................................................................. 18 . . . .

w. . .v 一、设计目标(题目)

电流镜负载的差分放大器 设计一款差分放大器,要求满足性能指标: 负载电容pFCL1

VVDD5 对管的m取4的倍数 低频开环增益>100 GBW(增益带宽积)>30MHz 输入共模范围>3V 功耗、面积尽量小 参考电路图如下图所示

设计步骤: 1、 仿真单个MOS的特性,得到某W/L下的MOS管的小信号输出电阻和跨导。 2、 根据上述仿真得到的器件特性,推导上述电路中的器件参数。 3、 手工推导上述尺寸下的差分级放大器的直流工作点、小信号增益、带宽、输入共模范围。 . . . . w. . .v 4、 如果增益和带宽不符合题目要求,则修改器件参数,并重复上述计算过程。 5、 一旦计算结果达到题目要求,用Hspice仿真验证上述指标。 如果仿真得到的增益和带宽不符合要求,则返回步骤2,直至符合要求

二、相关背景知识 传统运算放大器的输入级一般都采用电流镜负载的差分对。如下图所示。

1、单个MOSTFET的主要参数包括: 1.直流参数:

开启电压Vt,即当Vds为某一固定值使Id等于一微小电流时,栅源间的电压。 2.交流小信号参数:

PMOS、NMOS的栅跨导 g m : g m 越大,说明器件的放大能力越强,可以通过设计宽长比大的图形结构来提高跨导。 小信号电阻 r0 : r0 说明了Vds对Id的影响,是输出特性在某一点上切线斜率的倒数。 3.相关公式: 电流公式: . . . . w. . .v 2DnOXGSTH

1IC()VV12DSW

VL

MOS管等效电阻公式: 22221odsDrrI 44441odsDrrI

(饱和区)

Gds=λnID

电压增益: 2(2||4)vdmdsdsAgrr 增益带宽积:

2mLgGBWC

三、设计过程 1、电路结构

整体电路如上图。 . . . .

w. . .v 2、主要电路参数的手工推导

根据题目要求: 负载电容pFCL1

低频开环增益>100 GBW(增益带宽积)>30MHz 因以上公式不考虑沟道长度调制效应和体效应,所以理论计算和实际值会有一定误差,因此在此将增益带宽积提升为40MHz。

由2mLgGBWC

,得;

2mLgC>40610 得;

mg>2.51

-4

10

又有 m

g=2222mDgKI (

2

2x22ox

WuC

k

L

)

从工艺库得到:

model nvn nmos: +tox= '1.17e-08+toxn' 、+u0= 3.8300000e-02

得:2xoxuC=6.1839-410 后经仿真计算得到的 2xox

uC

=7.8600-410

选取ID2=15U 得:

2WL>3.396 ,考虑到存在一定误差,2WL

选择10.

要使MN2和MN4同时饱和,最小Vin.CM=Vdsat2+Vth4。仿真得Vdsat2=0.552V。Vth4=0.780V. 得最小输入共模电压Vin.CM=1.332V. 仿真得Vin.CM=4.5V时,增益为45db,增益带宽积为53MHz. 仍满足要求。 得输入共模范围大于:4.5-1.332=3.168V>3V 事实上当MN2和MN4没有同时饱和也能达到增益和带宽要求,输入共模电压Vin.CM=1.1V时,ID4=16.6u,增益为58.3db,增益带宽积为32.1MHz。 . . . . w. . .v 3、参数验证(手工推导)

根据上节的电路器件尺寸,通过手工推导出电路要求设计的各项指标。 并将计算出来的指标与要求进行对比。如果实际电路未能达到设计要求,则还需返回上一节的计算和推动过程,直至所设计电路符合题目要求。 为了减小面积并增大增益,PMOS的宽长比选取为1.

仿真得2WL=10的NMOS的λn=0.03581. 2

W

L

=1的PMOS的λp=0.01791

2222mDgKI=4.307

-4

10.

故增益带宽积为2mLgGBWC

=68.548MHz>30MHz,满足题目要求。

Ro2||Ro4=22441+DDII=1.241106 故2(2||4)vdmdsdsAgrr

=534.5>100. 满足要求。

四、电路仿真 1、NMOS特性仿真及参数推导 单个NMOS管以二极管形式连接,如图,其中电流I=15u,W=20U,L=2U,VDD=5V.