From the world of radio in the world to a single chip

有关芯片英语作文

有关芯片英语作文In the heart of modern technology lies the microchip, a tiny yet powerful component that has revolutionized the way we live, work, and communicate. The journey of the chip from its inception to its current state is a testament to human ingenuity and the relentless pursuit of innovation.The Dawn of the Chip EraThe microchip's story begins in the mid-20th century with the invention of the integrated circuit by Jack Kilby and Robert Noyce. This breakthrough allowed multiple electronic components to be etched onto a single silicon wafer, paving the way for smaller, more efficient devices.The Semiconductor RevolutionThe 1970s and 1980s saw the rise of the semiconductor industry, with companies like Intel and Texas Instruments at the forefront. The development of the microprocessor, the brain of the computer, was a pivotal moment. It enabled the creation of personal computers, which became increasingly accessible and affordable.The Age of MiniaturizationAs we entered the new millennium, the focus shifted towards miniaturization. Chips became smaller and more powerful, allowing for the development of smartphones, tablets, and wearable technology. The concept of Moore's Law, which predicted the doubling of transistors on a chip every twoyears, seemed to hold true.Current Trends and InnovationsToday, chip technology is at the forefront of advancements in artificial intelligence, machine learning, and quantum computing. Companies are pushing the boundaries of what is possible, with chips that can process vast amounts of data at incredible speeds.Challenges and the FutureDespite the rapid progress, challenges such as heat dissipation, power consumption, and the physical limits of silicon are being faced. Researchers are exploring new materials and architectures, such as graphene and 3D chip stacking, to overcome these hurdles.ConclusionThe microchip has come a long way since its early days. It is the unsung hero of our digital age, driving innovation across various sectors. As we look to the future, the potential for chip technology to shape our world is as limitless as our imagination. The ongoing evolution of the chip will undoubtedly continue to amaze and transform our lives in ways we are yet to fully comprehend.。

RDA1846

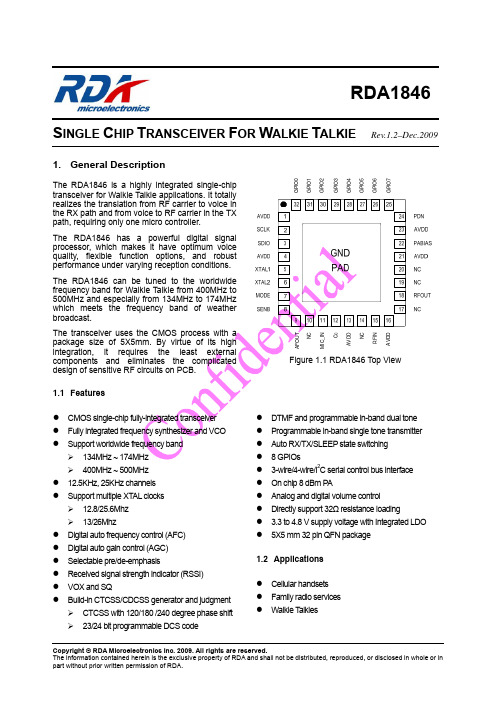

RDA1846S INGLE C HIP T RANSCEIVER F OR W ALKIE T ALKIE Rev.1.2–Dec.20091. General DescriptionThe RDA1846 is a highly integrated single-chip transceiver for Walkie Talkie applications. It totally realizes the translation from RF carrier to voice in the RX path and from voice to RF carrier in the TX path, requiring only one micro controller.The RDA1846 has a powerful digital signal processor, which makes it have optimum voice quality, flexible function options, and robust performance under varying reception conditions. The RDA1846 can be tuned to the worldwide frequency band for Walkie Talkie from 400MHz to 500MHz and especially from 134MHz to 174MHz which meets the frequency band of weather broadcast.The transceiver uses the CMOS process with a package size of 5X5mm. By virtue of its high integration, it requires the least external components and eliminates the complicated design of sensitive RF circuits on PCB.1.1 Features● CMOS single-chip fully-integrated transceiver ● Fully integrated frequency synthesizer and VCO ● Support worldwide frequency band134MHz ~ 174MHz 400MHz ~ 500MHz ● 12.5KHz, 25KHz channels ● Support multiple XTAL clocks12.8/25.6Mhz 13/26Mhz● Digital auto frequency control (AFC) ● Digital auto gain control (AGC) ● Selectable pre/de-emphasis ● Received signal strength indicator (RSSI) ● VOX and SQ● Build-in CTCSS/CDCSS generator and judgmentCTCSS with 120/180 /240 degree phase shift 23/24 bit programmable DCS code● DTMF and programmable in-band dual tone ● Programmable in-band single tone transmitter ● Auto RX/TX/SLEEP state switching ● 8 GPIOs● 3-wire/4-wire/I 2C serial control bus interface ● On chip 8 dBm P A● Analog and digital volume control ● Directly support 32Ω resistance loading ● 3.3 to 4.8 V supply voltage with Integrated LDO ● 5X5 mm 32 pin QFN package 1.2 Applications ● Cellularhandsets ● Family radio services ● Walkie T alkiesA F O U TN CM I C _I NA V D DN CR F I NA V DDC cG P I O 0G P I O 1G P I O 2G P I O 3G P I O 4G P I O 5G P I O 6G P I O 7Figure 1.1 RDA1846 Top View2. Table of Contents1.General Description (1)1.1Features (1)1.2Applications (1)2.Table of Contents (2)3.Functional Description (3)3.1RF input and output (3)3.2Voice input and output (4)3.3Synthesizer (4)3.4XTAL Clock (4)3.5DSP functions (4)3.6Integrated LDO (4)3.7Serial Control Interface (4)4.Electrical Characteristics (5)5.Receiver/Transmitter Characteristics (6)6.Control Interface Characteristics (7)7.Pins Description (8)8.Application Diagram (11)9.Package Outline (12)10.Solder Mounting Condition (13)11.Change List (16)12.Contact Information (16)3. Functional Description…Figure 3.1 RDA1846 Block DiagramThe RDA1846 transceiver features very low solution cost and reduced complexity. As shown in Fig.3.1, to totally complete the translation from RF carrier to voice in the RX path and from voice to RF carrier in the TX path, the chip integrates nearly all the functional blocks including RF and base band analog blocks and digital signal processor. It requires only one micro controller and a few external components to realize a walkie-talkie.A powerful integrated DSP accomplishes both the demodulation and modulation of the FM signal. Besides, standard walkie-talkie features such as CTS, CDS, VOX and SQ etc. are provided through the 8 GPIOs of the chip. Especially, by virtue of the state-of-the-art CMOS technology advanced algorithms such as AFC, AGC, RSSI and SNR calculations are realized in the DSP, which guarantees the high receiving and transmitting quality while still consumes a low power. Flexible RX/TX/SLEEP auto switching function from the DSP further reduces the average power consumptions.LDOs are also integrated in the chip which further reduces the BOMs.All interface pins of the chip will be shortly explained below. For details, refer to the ‘RDA 1846 programming guide’.3.1 RF input and outputThe chip can receive and transmit RF signals from 400 to 500MHz and from 134 to 174MHz which cover most of the walkie-talkie frequency bands around the world and the weather broadcast band. For the RF input, a direct-in connection from the antenna to the LNA input pin through a switch is suggested which means no input impedance matching is needed for the receive band. For the RF out, a pa diver can deliver no more than 8 dBm power to PA. PA bias voltage from 1.5V~2.8V for the power amplifier can be supplied from the PABIAS pin.3.2 Voice input and outputIn the RX path, the voice signal after demodulation is sent to the internal DAC which can directly drive a 32Ω resistance loading through AC coupling. In the TX path, microphone signal can be sent into the chip through AC coupling capacitors.3.3 SynthesizerThe frequency synthesizer generates the local oscillator signal. All building blocks are fully integrated without any external components. LO frequency can be programmed through the serial interface by the MCU. (How to select frequency band and program LO frequency, refer to the programming guide)3.4 XTAL ClockThe RDA1846 supports XT AL clocks such as 12.8 MHz, 13 MHz, 25.6 MHz and 26 MHz. The internal XTAL oscillator can also be bypassed thus TCXO clock with appropriate amplitude can be sent into the chip directly. (How to configure the internal XTAL oscillator, refer to the programming guide)3.5 DSP functionsThe DSP accomplishes the demodulation and modulation of the FM signal. Standard walkie-talkie features such as CTS, CDS, VOX and SQ etc. are provided through the 8 GPIOs. (How to configure theGPIOs, refer to the programming guide)3.6 Integrated LDOLDOs are integrated on chip which eliminates using one LDO chip on the PCB. Supply voltage for the chip is suggested to be within 3.3V~4.8V. A common share of the supply voltage for RDA1846 and other chips or on board circuits are not appropriate and thus not recommended.3.7 Serial Control InterfaceA 3-wire/4-wire/I2C serial interface is provided for host IC to read and write RDA1846 control registers. (For details of the serial control interface, refer to the programming guide).4. Electrical CharacteristicsTable 4-1 DC Electrical Specification (Recommended Operation Conditions): SYMBOL DESCRIPTION MIN TYP MAX UNITAVDD Supply Voltage from battery or LDO 3.3 3.3 4.8 VT amb Ambient Temperature -25 27 +85 ℃V L CMOS Low Level Input/output Voltage 0 0.3 VV H CMOS High Level Input/output Voltage 2.7 3 VV TH CMOSVoltage 1.5 V ThresholdTable 4-2 DC Electrical Specification (Absolute Maximum Ratings):SYMBOL DESCRIPTION MIN TYP MAX UNITT amb Ambient Temperature -40 +90 °CI IN Input Current-10 +10 mAV IN Input Voltage -0.3 3.3 VV lna LNA Input Level +10 dBmTable 4-3 Power consumption specification(AVDD = 3.3 V, T A = -25 to 85℃, unless otherwise specified)STATE DESCRIPTION Condition TYP UNITIContinue Receive RXON=1,PDN=1 55 mAI Tx Continue Transmit TXON=1,PDN=1 50 mAI sleep Deep sleep PDN=0 40 A5. Receiver/Transmitter CharacteristicsTable 5-1 Receiver Characteristics(AVDD = 3.3 V, TA = -25 to 85 °C, unless otherwise specified)SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNIT General specificationsFin Input Frequency Range1 400 520 MHz Input Frequency Range2 134 174 MHzInput Frequency Range3 200 260 MHz NF Noise Figure Max RX Gain 3 dB IP3in Input IP3 Max RX Gain -10 -6 0 dBmSEN Sensitivity 12.5kHz channel,12dB SINAD-125 -124 -123 dBmACS Adjacent Channel Selectivity±12.5KHz 65 66 67 dBIR Image rejection 60 70 dBBlocker >1MHz 85 dB Voice distortion 1.5 %Table 5-2 Transmit Characteristics(AVDD = 3.3 V, TA = -25 to 85°C, unless otherwise specified)SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITGeneral specificationsFout Output Frequency Range1400 520 MHzOutput Frequency Range2134 174 MHzOutput Frequency Range3200 260 MHzPOUT Output Power -2 5 8 dBmSINAD/SNR 48/53dB ACP Adjacent channel power-67 dBcModulation sensitivity 1.5kHz frequency offset13 mVVoice distortion 0.5 %Modulation limitation 2.2 2.5 kHz6. Control Interface Characteristics Refer to the ‘RDA1846 programming guide’.7. Pins DescriptionFigure 7.1 RDA1846 Top ViewTable 7-1 RDA1846 Pins DescriptionSYMBOLPINDESCRIPTIONAVDD 1 Power supply SCLK 2 Clock input for serial control bus SDIO 3 Data input/output for serial control bus AVDD 4 Power supplyXTAL1 5 Oscillator pin 1 XTAL26Oscillator pin 2MODE 7 Control Interface selectWhen MODE = V L , I 2C Interface is selectWhen MODE = V H , SPI Interface is selectSENB 8 Latch enable (active low) input for serial control bus AFOUT9Audio signal output to speakerNC* 10 No connection MIC_IN 11 MIC input Cc12Compensation capacitor connection pinAVDD 13 Power supply NC* 14 No connection RFIN15RF signal inputAVDD 16 Power supply NC* 17 No connection RFOUT18RF signal outputNC* 19 No connection NC* 20 No connection AVDD 21 Power supply PABIAS 22 PA bias supply for PA AVDD 23 Power supply PDN24Chip enable, low activeGPIO7 25Gpio7 / vox (When Gpio7=V H , vox is active; else V L ) GPIO6 26Gpio6 / sq(When Gpio6=V H , sq is active; else V L ) GPIO5 27Gpio5 / txon(When Gpio5=V H , txon is active; else V L ) GPIO4 28Gpio4 / rxon(When Gpio4=V H , rxon is active; else V L )GPIO3 29 Gpio3 / sdo(Gpio3=V H or V L , it is the output register data in 4 wire controlinterface mode)GPIO2 30Gpio2 / int(When Gpio2=V H , int is active; else V L )GPIO1 31Gpio1 / code_in / code_out(Gpio1=V H or V L , it is the input/output code data)GPIO0 32Gpio0 / css_in / css_out(Gpio0=V H or V L , it is the input/output CTCSS/CDCSS signal)*Attention: all NC pins should be floating. Do not connect it to GND!8. Application DiagramFigure 8.1 RDA1846 Application DiagramNotes:RDA1846Chip;1 U1:2 AVDD: Power Supply for RDA1846 (3.3~4.8V);3 AVDD_PA: Power Supply for RF PA, its voltage depends on the actual PA design;4 C0~C11: AVDD decouple capacitance (1nF and 100nF in pairs), as close to AVDD pin as possible;5 CA1~CA2: Audio AC couple capacitance (~47uF);6 Cc: Compensation capacitance connected between pin Cc and GND (~47uF);7 Crf: RF AC couple capacitance (~150pF);8 CX1~CX2: XTAL oscillator load capacitance. Its value depends on the chosen XTAL (if using external TCXO, clkshould be sent into pin XTAL1 with Vpp about 1.5V, and pin XTAL2 should be connected to GND);9 R0~R1(optional): resistors for serial interface wire SDIO and SCLK (~10kΩ);10 Pins NC(10,14,17,19,20) should be floating;11 External vox detection circuit is optional;9. Package Outline32-Pin 5x5 Quad Flat No-Lead (QFN)10. Solder Mounting ConditionClassification Reflow ProfileTable 10-1 Classification Reflow ProfilesProfile Feature Sn-Pb Eutectic Assembly Pb-Free Assembly Average Ramp-Up Rate(T Smax to T p)3 o C/second max. 3 o C/second max.Preheat-Temperature Min (T smin)-Temperature Max (T smax)-Time (t smin to t smax)100 o C100 o C60-120 seconds150 o C200 o C60-180 seconds Time maintained above:-Temperature (T L)-Time (t L)183 o C60-150seconds217o C60-150 seconds Peak /ClassificationTemperature(T p)See Table-II See Table-IIITime within 5 o C of actualPeak Temperature (t p)10-30 seconds 20-40 seconds Ramp-Down Rate 6 o C/second max. 6 o C/seconds max.Time 25 o C to PeakTemperature6 minutes max. 8 minutes max.Table 10-2 SnPb Eutectic Process – Package Peak Reflow TemperaturesPackage Thickness Volume mm3<350Volume mm3≥350<2.5mm 240 + 0/-5 o C 225 + 0/-5 o C ≥2.5mm225 + 0/-5 o C225 + 0/-5 o CTable 10-3 Pb-free Process – Package Classification Reflow TemperaturesPackage Thickness Volume mm3<350Volume mm3350-2000Volume mm3>2000<1.6mm 260 + 0 o C * 260 + 0 o C *260 + 0 o C *1.6mm –2.5mm 260 + 0 o C *250 + 0 o C *245 + 0 o C *≥2.5mm250 + 0 o C *245 + 0 o C *245 + 0 o C * *Tolerance : The device manufacturer/supplier shall assure process compatibility up to and including the stated classification temperature(this mean Peak reflow temperature + 0 o C. Forexample 260+ 0 o C ) at the rated MSL Level.Note 1: All temperature refer topside of the package. Measured on the package body surface.Note 2: The profiling tolerance is + 0 o C, - X o C (based on machine variation capability)whatever is required to control the profile process but at no time will it exceed - 5 o C. The producer assures process compatibility at the peak reflow profile temperatures defined in Table –III. Note 3: Package volume excludes external terminals(balls, bumps, lands, leads) and/or non integral heat sinks.Note 4: The maximum component temperature reached during reflow depends on package the thickness and volume. The use of convection reflow processes reduces the thermal gradients between packages. However, thermal gradients due to differences in thermal mass of SMD package may sill exist.Note 5: Components intended for use in a “lead-free” assembly process shall be evaluated using the “lead free” classification temperatures and profiles defined in Table-I II III whether or not lead free.RoHS CompliantThe product does not contain lead, mercury, cadmium, hexavalent chromium, polybrominated biphenyls (PBB) or polybrominated diphenyl ethers (PBDE), and are therefore considered RoHS compliant.ESD SensitivityIntegrated circuits are ESD sensitive and can be damaged by static electricity. Proper ESD techniques should be used when handling these devices.11. Change ListREV DATE AUTHER CHANGE DESCRIPTION v1.0e 2009-06-24 Hao Shi Original draft.v1.1e 2009-10-10 Ge Liu V1.1 original draftv1.2e 2009-12-11 Ge Liu Add 200M~260MHz12. Contact InformationRDA Microelectronics (Shanghai), Inc.Suite 1108 Block A, e-Wing Center, 113 Zhichun Road Haidian District, BeijingTel: 86-10-62635360Fax: 86-10-82612663Postal Code: 100086。

I2C总线协议规范 v2.1

THE I2C-BUS SPECIFICATIONVERSION 2.1JANUARY 2000CONTENTS1PREFACE. . . . . . . . . . . . . . . . . . . . . . . . . . .3 1.1Version 1.0 - 1992. . . . . . . . . . . . . . . . . . . . 3 1.2Version 2.0 - 198. . . . . . . . . . . . . . . . . . . . . 3 1.3Version 2.1 - 1999. . . . . . . . . . . . . . . . . . . . 3 1.4Purchase of Philips I2C-bus components . . 3 2THE I2C-BUS BENEFITS DESIGNERSAND MANUFACTURERS. . . . . . . . . . . . . . .4 2.1Designer benefits . . . . . . . . . . . . . . . . . . . . 4 2.2Manufacturer benefits. . . . . . . . . . . . . . . . . 6 3INTRODUCTION TO THE I2C-BUSSPECIFICATION . . . . . . . . . . . . . . . . . . . . .6 4THE I2C-BUS CONCEPT . . . . . . . . . . . . . . .6 5GENERAL CHARACTERISTICS . . . . . . . . .8 6BIT TRANSFER . . . . . . . . . . . . . . . . . . . . . .8 6.1Data validity . . . . . . . . . . . . . . . . . . . . . . . . 8 6.2START and STOP conditions. . . . . . . . . . . 9 7TRANSFERRING DATA. . . . . . . . . . . . . . .10 7.1Byte format . . . . . . . . . . . . . . . . . . . . . . . . 10 7.2Acknowledge. . . . . . . . . . . . . . . . . . . . . . . 10 8ARBITRATION AND CLOCKGENERATION . . . . . . . . . . . . . . . . . . . . . .11 8.1Synchronization . . . . . . . . . . . . . . . . . . . . 11 8.2Arbitration . . . . . . . . . . . . . . . . . . . . . . . . . 12 8.3Use of the clock synchronizingmechanism as a handshake. . . . . . . . . . . 13 9FORMATS WITH 7-BIT ADDRESSES. . . .13 107-BIT ADDRESSING . . . . . . . . . . . . . . . . .15 10.1Definition of bits in the first byte . . . . . . . . 15 10.1.1General call address. . . . . . . . . . . . . . . . . 16 10.1.2START byte . . . . . . . . . . . . . . . . . . . . . . . 17 10.1.3CBUS compatibility. . . . . . . . . . . . . . . . . . 18 11EXTENSIONS TO THE STANDARD-MODE I2C-BUS SPECIFICATION . . . . . . .19 12FAST-MODE. . . . . . . . . . . . . . . . . . . . . . . .19 13Hs-MODE . . . . . . . . . . . . . . . . . . . . . . . . . .20 13.1High speed transfer. . . . . . . . . . . . . . . . . . 20 13.2Serial data transfer format in Hs-mode. . . 21 13.3Switching from F/S- to Hs-mode andback . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2313.4Hs-mode devices at lower speed modes. . 24 13.5Mixed speed modes on one serial bussystem. . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 13.5.1F/S-mode transfer in a mixed-speed bussystem. . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 13.5.2Hs-mode transfer in a mixed-speed bussystem. . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 13.5.3Timing requirements for the bridge in amixed-speed bus system. . . . . . . . . . . . . . 27 1410-BIT ADDRESSING. . . . . . . . . . . . . . . . 27 14.1Definition of bits in the first two bytes. . . . . 27 14.2Formats with 10-bit addresses. . . . . . . . . . 27 14.3General call address and start byte with10-bit addressing. . . . . . . . . . . . . . . . . . . . 30 15ELECTRICAL SPECIFICATIONSAND TIMING FOR I/O STAGESAND BUS LINES. . . . . . . . . . . . . . . . . . . . 30 15.1Standard- and Fast-mode devices. . . . . . . 30 15.2Hs-mode devices. . . . . . . . . . . . . . . . . . . . 34 16ELECTRICAL CONNECTIONS OFI2C-BUS DEVICES TO THE BUS LINES . 37 16.1Maximum and minimum values ofresistors R p and R s for Standard-modeI2C-bus devices . . . . . . . . . . . . . . . . . . . . . 39 17APPLICATION INFORMATION. . . . . . . . . 41 17.1Slope-controlled output stages ofFast-mode I2C-bus devices. . . . . . . . . . . . 41 17.2Switched pull-up circuit for Fast-modeI2C-bus devices . . . . . . . . . . . . . . . . . . . . . 41 17.3Wiring pattern of the bus lines. . . . . . . . . . 42 17.4Maximum and minimum values ofresistors R p and R s for Fast-modeI2C-bus devices . . . . . . . . . . . . . . . . . . . . . 42 17.5Maximum and minimum values ofresistors R p and R s for Hs-modeI2C-bus devices . . . . . . . . . . . . . . . . . . . . . 42 18BI-DIRECTIONAL LEVEL SHIFTERFOR F/S-MODE I2C-BUS SYSTEMS . . . . 42 18.1Connecting devices with differentlogic levels. . . . . . . . . . . . . . . . . . . . . . . . . 43 18.1.1Operation of the level shifter . . . . . . . . . . . 44 19DEVELOPMENT TOOLS AVAILABLEFROM PHILIPS. . . . . . . . . . . . . . . . . . . . . 45 20SUPPORT LITERATURE . . . . . . . . . . . . . 461PREFACE1.1Version 1.0 - 1992This version of the 1992 I2C-bus specification includes the following modifications:•Programming of a slave address by software has been omitted. The realization of this feature is rather complicated and has not been used.•The “low-speed mode” has been omitted. This mode is, in fact, a subset of the total I2C-bus specification and need not be specified explicitly.•The Fast-mode is added. This allows a fourfold increase of the bit rate up to 400kbit/s. Fast-mode devices are downwards compatible i.e. they can be used in a 0 to 100kbit/s I2C-bus system.•10-bit addressing is added. This allows 1024 additional slave addresses.•Slope control and input filtering for Fast-mode devices is specified to improve the EMC behaviour.NOTE: Neither the 100kbit/s I2C-bus system nor the 100kbit/s devices have been changed.1.2Version2.0 - 1998The I2C-bus has become a de facto world standard that is now implemented in over 1000 different ICs and licensed to more than 50 companies. Many of today’s applications, however, require higher bus speeds and lower supply voltages. This updated version of the I2C-bus specification meets those requirements and includes the following modifications:•The High-speed mode (Hs-mode) is added. This allows an increase in the bit rate up to 3.4Mbit/s. Hs-mode devices can be mixed with Fast- and Standard-mode devices on the one I2C-bus system with bit rates from 0 to 3.4Mbit/s.•The low output level and hysteresis of devices with a supply voltage of 2V and below has been adapted to meet the required noise margins and to remain compatible with higher supply voltage devices.•The 0.6V at 6mA requirement for the output stages of Fast-mode devices has been omitted.•The fixed input levels for new devices are replaced by bus voltage-related levels.•Application information for bi-directional level shifter is added.1.3Version2.1 - 2000Version 2.1 of the I2C-bus specification includes the following minor modifications:•After a repeated START condition in Hs-mode, it is possible to stretch the clock signal SCLH (see Section13.2 and Figs22, 25 and 32).•Some timing parameters in Hs-mode have been relaxed (see Tables6 and 7).1.4Purchase of Philips I2C-bus componentsPurchase of Philips I2C components conveys a license under the Philips’ I2C patent to use thecomponents in the I2C system provided the system conforms to the I2C specification defined byPhilips.2THE I2C-BUS BENEFITS DESIGNERS AND MANUFACTURERSIn consumer electronics, telecommunications and industrial electronics, there are often many similarities between seemingly unrelated designs. For example, nearly every system includes:•Some intelligent control, usually a single-chip microcontroller•General-purpose circuits like LCD drivers, remote I/O ports, RAM, EEPROM, or data converters•Application-oriented circuits such as digital tuning and signal processing circuits for radio and video systems, or DTMF generators for telephones with tone dialling.To exploit these similarities to the benefit of both systems designers and equipment manufacturers, as well as to maximize hardware efficiency and circuit simplicity, Philips developed a simple bi-directional 2-wire bus for efficient inter-IC control. This bus is called the Inter IC or I2C-bus. At present, Philips’ IC range includes more than 150 CMOS and bipolar I2C-bus compatible types for performing functions in all three of the previously mentioned categories. All I2C-bus compatible devices incorporate an on-chip interface which allows them to communicate directly with each other via the I2C-bus. This design concept solves the many interfacing problems encountered when designing digital control circuits.Here are some of the features of the I2C-bus:•Only two bus lines are required; a serial data line (SDA) and a serial clock line (SCL)•Each device connected to the bus is software addressable by a unique address and simplemaster/slave relationships exist at all times; masters can operate as master-transmitters or as master-receivers•It’s a true multi-master bus including collision detection and arbitration to prevent data corruption if two or more masters simultaneously initiate data transfer•Serial, 8-bit oriented, bi-directional data transfers can be made at up to 100kbit/s in the Standard-mode, up to 400kbit/s in the Fast-mode, or up to 3.4Mbit/s in the High-speed mode•On-chip filtering rejects spikes on the bus data line to preserve data integrity •The number of ICs that can be connected to the same bus is limited only by a maximum bus capacitance of 400pF.Figure1 shows two examples of I2C-bus applications. 2.1Designer benefitsI2C-bus compatible ICs allow a system design to rapidly progress directly from a functional block diagram to a prototype. Moreover, since they ‘clip’ directly onto theI2C-bus without any additional external interfacing, they allow a prototype system to be modified or upgraded simply by ‘clipping’ or ‘unclipping’ ICs to or from the bus. Here are some of the features of I2C-bus compatible ICs which are particularly attractive to designers:•Functional blocks on the block diagram correspond with the actual ICs; designs proceed rapidly from block diagram to final schematic.•No need to design bus interfaces because the I2C-bus interface is already integrated on-chip.•Integrated addressing and data-transfer protocol allow systems to be completely software-defined•The same IC types can often be used in many different applications•Design-time reduces as designers quickly become familiar with the frequently used functional blocks represented by I2C-bus compatible ICs•ICs can be added to or removed from a system without affecting any other circuits on the bus•Fault diagnosis and debugging are simple; malfunctions can be immediately traced•Software development time can be reduced by assembling a library of reusable software modules.In addition to these advantages, the CMOS ICs in theI2C-bus compatible range offer designers special features which are particularly attractive for portable equipment and battery-backed systems.They all have:•Extremely low current consumption•High noise immunity•Wide supply voltage range•Wide operating temperature range.Fig.1 Two examples of I 2C-bus applications: (a) a high performance highly-integrated TV set(b) DECT cordless phone base-station.handbook, full pagewidthSDA SCLMICRO-CONTROLLER PCB83C528PLLSYNTHESIZERTSA5512NON-VOLATILE MEMORY PCF8582ESTEREO / DUAL SOUND DECODER TDA9840HI-FI AUDIOPROCESSOR TDA9860SINGLE-CHIP TEXT SAA52XXM/S COLOUR DECODER TDA9160APICTURE SIGNALIMPROVEMENTTDA4670VIDEOPROCESSORTDA4685ON-SCREENDISPLAYPCA8510(a)MSB575SDASCLLINEINTERFACEPCA1070BURST MODE CONTROLLERPCD5042ADPCMPCD5032(b)DTMFGENERATOR PCD3311MICRO-CONTROLLER P80CLXXX2.2Manufacturer benefitsI2C-bus compatible ICs don’t only assist designers, they also give a wide range of benefits to equipment manufacturers because:•The simple 2-wire serial I2C-bus minimizes interconnections so ICs have fewer pins and there are not so many PCB tracks; result - smaller and less expensive PCBs•The completely integrated I2C-bus protocol eliminates the need for address decoders and other ‘glue logic’•The multi-master capability of the I2C-bus allows rapid testing and alignment of end-user equipment via external connections to an assembly-line•The availability of I2C-bus compatible ICs in SO (small outline), VSO (very small outline) as well as DIL packages reduces space requirements even more. These are just some of the benefits. In addition, I2C-bus compatible ICs increase system design flexibility by allowing simple construction of equipment variants and easy upgrading to keep designs up-to-date. In this way, an entire family of equipment can be developed around a basic model. Upgrades for new equipment, or enhanced-feature models (i.e. extended memory, remote control, etc.) can then be produced simply by clipping the appropriate ICs onto the bus. If a larger ROM is needed, it’s simply a matter of selecting a micro-controller with a larger ROM from our comprehensive range. As new ICs supersede older ones, it’s easy to add new features to equipment or to increase its performance by simply unclipping the outdated IC from the bus and clipping on its successor.3INTRODUCTION TO THE I2C-BUS SPECIFICATION For 8-bit oriented digital control applications, such as those requiring microcontrollers, certain design criteria can be established:•A complete system usually consists of at least one microcontroller and other peripheral devices such as memories and I/O expanders•The cost of connecting the various devices within the system must be minimized •A system that performs a control function doesn’t require high-speed data transfer•Overall efficiency depends on the devices chosen and the nature of the interconnecting bus structure.To produce a system to satisfy these criteria, a serial bus structure is needed. Although serial buses don’t have the throughput capability of parallel buses, they do require less wiring and fewer IC connecting pins. However, a bus is not merely an interconnecting wire, it embodies all the formats and procedures for communication within the system.Devices communicating with each other on a serial bus must have some form of protocol which avoids all possibilities of confusion, data loss and blockage of information. Fast devices must be able to communicate with slow devices. The system must not be dependent on the devices connected to it, otherwise modifications or improvements would be impossible. A procedure has also to be devised to decide which device will be in control of the bus and when. And, if different devices with different clock speeds are connected to the bus, the bus clock source must be defined. All these criteria are involved in the specification of the I2C-bus.4THE I2C-BUS CONCEPTThe I2C-bus supports any IC fabrication process (NMOS, CMOS, bipolar). Two wires, serial data (SDA) and serial clock (SCL), carry information between the devices connected to the bus. Each device is recognized by a unique address (whether it’s a microcontroller, LCD driver, memory or keyboard interface) and can operate as either a transmitter or receiver, depending on the function of the device. Obviously an LCD driver is only a receiver, whereas a memory can both receive and transmit data. In addition to transmitters and receivers, devices can also be considered as masters or slaves when performing data transfers (see Table 1). A master is the device which initiates a data transfer on the bus and generates the clock signals to permit that transfer. At that time, any device addressed is considered a slave.Table 1Definition of I 2C-bus terminologyThe I 2C-bus is a multi-master bus. This means that more than one device capable of controlling the bus can be connected to it. As masters are usually micro-controllers, let’s consider the case of a data transfer between two microcontrollers connected to the I 2C-bus (see Fig.2). This highlights the master-slave and receiver-transmitter relationships to be found on the I 2C-bus. It should be noted that these relationships are not permanent, but onlydepend on the direction of data transfer at that time. The transfer of data would proceed as follows:1) Suppose microcontroller A wants to send information to microcontroller B:•microcontroller A (master), addresses microcontroller B (slave)•microcontroller A (master-transmitter), sends data to microcontroller B (slave- receiver)•microcontroller A terminates the transfer2) If microcontroller A wants to receive information from microcontroller B:•microcontroller A (master) addresses microcontroller B (slave)•microcontroller A (master- receiver) receives data from microcontroller B (slave- transmitter)•microcontroller A terminates the transfer.Even in this case, the master (microcontroller A) generates the timing and terminates the transfer.The possibility of connecting more than onemicrocontroller to the I 2C-bus means that more than one master could try to initiate a data transfer at the same time. To avoid the chaos that might ensue from such an event - an arbitration procedure has been developed. Thisprocedure relies on the wired-AND connection of all I 2C interfaces to the I 2C-bus.If two or more masters try to put information onto the bus, the first to produce a ‘one’ when the other produces a ‘zero’ will lose the arbitration. The clock signals during arbitration are a synchronized combination of the clocks generated by the masters using the wired-AND connection to the SCL line (for more detailed information concerning arbitration see Section 8).TERM DESCRIPTIONT ransmitter The device which sends data to the busReceiver The device which receives data from the busMasterThe device which initiates a transfer, generates clock signals and terminates a transferSlave The device addressed by a master Multi-masterMore than one master can attempt to control the bus at the same time without corrupting the message ArbitrationProcedure to ensure that, if more than one master simultaneously tries to control the bus, only one is allowed to do so and the winning message is not corruptedSynchronizationProcedure to synchronize the clock signals of two or more devicesFig.2 Example of an I 2C-bus configuration using two microcontrollers.MBC645SDA SCLMICRO -CONTROLLER ASTATIC RAM OR EEPROMLCD DRIVERGATE ARRAYADCMICRO -CONTROLLER BGeneration of clock signals on the I 2C-bus is always the responsibility of master devices; each master generates its own clock signals when transferring data on the bus. Bus clock signals from a master can only be altered when they are stretched by a slow-slave device holding-down the clock line, or by another master when arbitration occurs.5GENERAL CHARACTERISTICSBoth SDA and SCL are bi-directional lines, connected to a positive supply voltage via a current-source or pull-up resistor (see Fig.3). When the bus is free, both lines are HIGH. The output stages of devices connected to the bus must have an open-drain or open-collector to perform the wired-AND function. Data on the I 2C-bus can be transferred at rates of up to 100kbit/s in theStandard-mode, up to 400kbit/s in the Fast-mode, or up to 3.4Mbit/s in the High-speed mode. The number ofinterfaces connected to the bus is solely dependent on the bus capacitance limit of 400pF. For information on High-speed mode master devices, see Section 13.6BIT TRANSFERDue to the variety of different technology devices (CMOS, NMOS, bipolar) which can be connected to the I 2C-bus, the levels of the logical ‘0’ (LOW) and ‘1’ (HIGH) are not fixed and depend on the associated level of V DD (see Section 15 for electrical specifications). One clock pulse is generated for each data bit transferred.6.1Data validityThe data on the SDA line must be stable during the HIGH period of the clock. The HIGH or LOW state of the data line can only change when the clock signal on the SCL line is LOW (see Fig.4).Fig.3 Connection of Standard- and Fast-mode devices to the I 2C-bus.MBC631SCLKN1OUT SCLK INSCLKDATAN1OUT DATA IN DEVICE 1SDA (Serial Data Line)SCL (Serial Clock Line)SCLKN2OUT SCLK INSCLK DATAN2OUT DATA IN DEVICE 2V DDR pR ppull-up resistorsFig.4 Bit transfer on the I 2C-bus.handbook, full pagewidthMBC621data line stable;data validchange of data allowedSDASCL6.2START and STOP conditionsWithin the procedure of the I 2C-bus, unique situations arise which are defined as START (S) and STOP (P) conditions (see Fig.5).A HIGH to LOW transition on the SDA line while SCL is HIGH is one such unique case. This situation indicates a START condition.A LOW to HIGH transition on the SDA line while SCL is HIGH defines a STOP condition.START and STOP conditions are always generated by the master. The bus is considered to be busy after the START condition. The bus is considered to be free again a certain time after the STOP condition. This bus free situation is specified in Section 15.The bus stays busy if a repeated START (Sr) is generated instead of a STOP condition. In this respect, the START (S) and repeated START (Sr) conditions are functionally identical (see Fig. 10). For the remainder of this document, therefore, the S symbol will be used as a generic term to represent both the START and repeated START conditions, unless Sr is particularly relevant.Detection of START and STOP conditions by devices connected to the bus is easy if they incorporate the necessary interfacing hardware. However,microcontrollers with no such interface have to sample the SDA line at least twice per clock period to sense the transition.Fig.5 START and STOP conditions.handbook, full pagewidthMBC622SDA SCLPSTOP conditionSDASCLSSTART condition7TRANSFERRING DATA 7.1Byte formatEvery byte put on the SDA line must be 8-bits long. The number of bytes that can be transmitted per transfer is unrestricted. Each byte has to be followed by an acknowledge bit. Data is transferred with the most significant bit (MSB) first (see Fig.6). If a slave can’t receive or transmit another complete byte of data until it has performed some other function, for example servicing an internal interrupt, it can hold the clock line SCL LOW to force the master into a wait state. Data transfer thencontinues when the slave is ready for another byte of data and releases clock line SCL.In some cases, it’s permitted to use a different format from the I 2C-bus format (for CBUS compatible devices for example). A message which starts with such an address can be terminated by generation of a STOP condition, even during the transmission of a byte. In this case, no acknowledge is generated (see Section 10.1.3).7.2AcknowledgeData transfer with acknowledge is obligatory. The acknowledge-related clock pulse is generated by the master. The transmitter releases the SDA line (HIGH) during the acknowledge clock pulse.The receiver must pull down the SDA line during the acknowledge clock pulse so that it remains stable LOWduring the HIGH period of this clock pulse (see Fig.7). Of course, set-up and hold times (specified in Section 15) must also be taken into account.Usually, a receiver which has been addressed is obliged to generate an acknowledge after each byte has been received, except when the message starts with a CBUS address (see Section 10.1.3).When a slave doesn’t acknowledge the slave address (for example, it’s unable to receive or transmit because it’s performing some real-time function), the data line must be left HIGH by the slave. The master can then generate either a STOP condition to abort the transfer, or a repeated START condition to start a new transfer.If a slave-receiver does acknowledge the slave address but, some time later in the transfer cannot receive any more data bytes, the master must again abort the transfer. This is indicated by the slave generating thenot-acknowledge on the first byte to follow. The slave leaves the data line HIGH and the master generates a STOP or a repeated START condition.If a master-receiver is involved in a transfer, it must signal the end of data to the slave- transmitter by not generating an acknowledge on the last byte that was clocked out of the slave. The slave-transmitter must release the data line to allow the master to generate a STOP or repeated START condition.Fig.6 Data transfer on the I 2C-bus.handbook, full pagewidthMSC608Sr or PSDASrPSCLSTOP or repeated STARTconditionS or SrSTART or repeated STARTcondition12 3 - 89ACK9ACK7812MSBacknowledgement signal from slavebyte complete,interrupt within slaveclock line held low while interrupts are servicedacknowledgement signal from receiverFig.7 Acknowledge on the I 2C-bus.handbook, full pagewidthMBC602S START condition9821clock pulse for acknowledgementnot acknowledgeacknowledgeDATA OUTPUT BY TRANSMITTERDATA OUTPUT BY RECEIVERSCL FROM MASTER8ARBITRATION AND CLOCK GENERATION 8.1SynchronizationAll masters generate their own clock on the SCL line to transfer messages on the I 2C-bus. Data is only valid during the HIGH period of the clock. A defined clock is therefore needed for the bit-by-bit arbitration procedure to take place.Clock synchronization is performed using the wired-AND connection of I 2C interfaces to the SCL line. This meansthat a HIGH to LOW transition on the SCL line will cause the devices concerned to start counting off their LOW period and, once a device clock has gone LOW, it will hold the SCL line in that state until the clock HIGH state is reached (see Fig.8). However, the LOW to HIGH transition of this clock may not change the state of the SCL line if another clock is still within its LOW period. The SCL line will therefore be held LOW by the device with the longest LOW period. Devices with shorter LOW periods enter a HIGH wait-state during this time.Fig.8 Clock synchronization during the arbitration procedure.CLK 1CLK 2SCLcounter resetwait statestart counting HIGH periodMBC632When all devices concerned have counted off their LOW period, the clock line will be released and go HIGH. There will then be no difference between the device clocks and the state of the SCL line, and all the devices will start counting their HIGH periods. The first device to complete its HIGH period will again pull the SCL line LOW.In this way, a synchronized SCL clock is generated with its LOW period determined by the device with the longest clock LOW period, and its HIGH period determined by the one with the shortest clock HIGH period.8.2ArbitrationA master may start a transfer only if the bus is free. Two or more masters may generate a START condition within the minimum hold time (t HD;STA ) of the START condition which results in a defined START condition to the bus.Arbitration takes place on the SDA line, while the SCL line is at the HIGH level, in such a way that the master which transmits a HIGH level, while another master istransmitting a LOW level will switch off its DATA output stage because the level on the bus doesn’t correspond to its own level.Arbitration can continue for many bits. Its first stage is comparison of the address bits (addressing information is given in Sections 10 and 14). If the masters are each tryingto address the same device, arbitration continues with comparison of the data-bits if they are master-transmitter, or acknowledge-bits if they are master-receiver. Because address and data information on the I 2C-bus is determined by the winning master, no information is lost during the arbitration process.A master that loses the arbitration can generate clock pulses until the end of the byte in which it loses the arbitration.As an Hs-mode master has a unique 8-bit master code, it will always finish the arbitration during the first byte (see Section 13).If a master also incorporates a slave function and it loses arbitration during the addressing stage, it’s possible that the winning master is trying to address it. The losingmaster must therefore switch over immediately to its slave mode.Figure 9 shows the arbitration procedure for two masters. Of course, more may be involved (depending on how many masters are connected to the bus). The moment there is a difference between the internal data level of the master generating DATA 1 and the actual level on the SDA line, its data output is switched off, which means that a HIGH output level is then connected to the bus. This will not affect the data transfer initiated by the winning master.Fig.9 Arbitration procedure of two masters.handbook, full pagewidthMSC609DATA 1DATA 2SDASCLSmaster 1 loses arbitrationDATA 1 SDA。

毕业设计(论文)-基于单片机的多功能钟控收音机的设计与实现--闹钟子系统的设计与实现[管理资料]

![毕业设计(论文)-基于单片机的多功能钟控收音机的设计与实现--闹钟子系统的设计与实现[管理资料]](https://img.taocdn.com/s3/m/93ab9c330c22590103029d9e.png)

基于单片机的多功能钟控收音机的设计与实现——闹钟子系统的设计与实现摘要收音机是现在生活中的一种娱乐工具,它可以扩展我们的知识面,丰富我们是日常生活。

但是现在的收音机仅仅只拥有收台、听台、存台的功能,功能上非常的单一,为了让收音机具有更强大的的功能,设计了这套基于单片机的多功能钟控收音机系统。

这套系统在传统的收音机上增加了时钟设置、温度测量、液晶显示以及闹钟设置多项功能。

本文主要论述了系统的方案设计,系统硬件设计包括硬件选型和硬件电路图;系统软件设计包括程序流程图设计和关键代码。

通过编写代码实现收音机节目的播放、音量调节、电台切换及节目的自动搜索、节目频点存储功能、时钟设置、温度测量、液晶显示以及闹钟功能。

且能够通过按键调整系统时钟,到达设定闹铃时间值可选择蜂鸣器响或开启收音机到指定频点。

该系统与传统的收音机系统相比较,具有结构简单,抗干扰能力强,测量精度高,使用方便的特点。

关键字:单片机;收音机;闹钟;液晶显示Based on SCM multi-function clock radio control design and realized ——Alarm subsystem of design and implementationAuthor:Li XinfangTutor:Yang BoAbstractThe radio is now in the life of the one kind of entertainment tool, it can expand our knowledge, enrich our daily life is. But now the radio only accept ,listen , save a function, the function is a single, in order to let the radio has more powerful function, the set design based on single chip microcomputer multifunctional clock radio control system. The system in the traditional radio increased the clock set, temperature measurement, liquid crystal display and alarm multiple functions. This paper discusses the design of the whole system, hardware design including hardware selection and hardware circuit diagram; System software design including program flowchart design and key code. By writing code realization of radio programs broadcast, volume adjustment, radio switch and programs to be automatic search, the program frequency memory function, clock set, temperature measurement, liquid crystal display and alarm clock function. And to be able to button to adjust the system clock, to set the alarm time value can choose a buzzer rang or open radio frequency to the specified. This system and the traditional radio system comparison, the structure is simple, strong anti-jamming ability, high accuracy, easy to use features.Key words: Single chip microcomputer; the radio; the alarm clock; liquid crystal display目录1 绪论 0 0研究的目的及意义 0本文结构 (1)2 系统方案设计 (2) (2) (2)收音机模块 (3)时钟模块 (3)温度模块 (3)显示模块 (3)闹钟模块 (3)按键模块 (4)3 系统硬件设计 (5) (5) (5)AT89S52单片机的引脚结构分析 (6)单片机最小系统设计图 (7)显示模块硬件电路设计 (7) (7)显示模块电路设计 (8)按键模块硬件电路设计 (8)时钟模块的硬件电路设计 (9) (9) (9) (10)存储模块硬件电路设计 (11) (11) (11)AT24C02电路设计 (12)打铃模块电路设计 (12)4 系统软件设计 (14)系统软件总体设计 (14)主控模块详细设计 (14)显示模块详细设计 (16)按键模块详细设计 (17)时钟模块详细设计 (18) (18)存储模块详细设计 (20) (21) (23)5系统的调试与实现 (25)C介绍 (25)6 结束语 (27)参考文献 (28)致谢 (29)1 绪论收音机一直在人们的生活娱乐中占有非常重要的地位。

KT0612音频接收芯片

Applications

Wireless Microphone, DVD player, Blue ray player, Set-top Box, Portable Device, Wireless Speaker

Rev.1.2

Information furnished by KT Micro is believed to be accurate and reliable. However, no responsibility is assumed by KT Micro for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Beijing KT Micro, Ltd.

RFINP LNA RFINN ADC AOUTP Audio DAC AOUTN

DSP Based FM demodulator & Audio processor

ADC

SCL I2C Master SDA Regulator Crystal

VDDVSSXI NhomakorabeaXO

KT0612 System Diagram

Description

The KT0612 is the VHF band chip of our full suite of the revolutionary wireless microphone chips, KT06xx, which replace hundreds of discrete components in a wireless microphone system while keeping the high standard of sound quality and functionality. The KT0612 is a VHF band receiver that includes audio amplifier, de-emphasis, expander, LO synthesizer and audio DAC. It is designed to process the modulated FM signal in VHF band and demodulate it into audio signal. The KT0612 only requires a single low-voltage supply thanks to a built-in regulator. For an audio transmission system built with a KT0612, no external tuning is required, which makes design-in effort minimum. The KT0612 provides direct and simple interface to support mechanical tuning. A pre-programmed low cost EEPROM can be used to configure the radio settings to differentiate product designs and accommodate standards in various regions. No external MCU is required. It is packaged in generic QFN24.

使用DMR和DSDPlus入门说明书

Andrew Milluzzi, KK4LWR125 SE 16th Ave., Apt L202, Gainesville, FL 32601; *******************Getting Started withDMR and DSDPlus This simple tutorial can help get you started on digital modulation.Digital modulations are becoming quitepopular in Amateur Radio. Technologies likeDMR, D-STAR, and System Fusion havemade the technology accessible and a newplatform for experimentation. Recently therewas much buzz about the Tytera MD-380,an inexpensive digital mobile radio (DMR)handheld transceiver. Technologies suchas the RTL-SDR — software defined radiobased on the RTL chip set — have broughtsoftware defined radio to the masses.C ombining these two technologies canenable additional experimentation.Recently the Gator Amateur RadioClub, W4DFU, at the University of Floridainstalled a DMR repeater for Gainesvilleand the surrounding area. This repeater is agreat resource for students and Technicianclass operators to talk all over the worldusing UHF locally. It is easy to get startedwith DMR by just listening to typical DMRcontacts. Depending on the talk group, someare quick, others are well organized nets. One option to decode DMR is to purchase a radio. Another is constructing a receiver from an RTL-SDR, an antenna, and some software.What is DMR?DMR stands for Digital Mobile Radio. Sometimes it is called MotoTURBO, the DMR product produced by Motorola Solutions. Like D-STAR or System Fusion, DMR digitizes voice using a vocoder and sends the information via digital packet. Unlike D-STAR and System Fusion, DMR uses TDMA (Time Division Multiple Access) with two time slots in 12.5 kHz. This enables one DMR repeater to act as two on a given frequency.What is DSDPlus?DSDPlus is an application that runs on aWindows computer that can decode multipledigital modes.1 Similar to the open sourceDSD program, DSDPlus takes an audiostream from a radio and can generate text oraudio. The main difference for the scope ofthis tutorial is that the open source programmust be compiled from source code, whileDSDPlus offers a Windows binary.Hardware SetupMy decoding setup requires just a fewpieces of physical hardware, seen in Figure1, and a some virtual hardware. The firstthing you need is a DMR source. I alreadyhad purchased a Tytera MD-380 handheldtransceiver, since I am quite interested inthe ongoing firmware experimentationcommunity. Y ou might already have a DMRsource, via other hams and perhaps a localrepeater. If you do decided to purchase aDMR radio, Motorola Solutions and Hyteraeach make some outstanding radios. BothC onnect Systems and Tytera make somemore inexpensive options.The second needed piece of hardware is aradio to connect to your computer. Y ou coulduse a VHF/UHF radio and a sound card tointerface with your computer. However, Iopted for an RTL-SDR for this project. AnRTL-SDR is essentially an inexpensive TVtuner USB dongle for your computer. Itcan be purchased for less than $20 and cancover 50 MHz to 1.7 GHz. Your Windows Figure 1 — DMR decoding setup using a Tytera MD-380 handheld transceiver, a laptop computer, and an RTL-SDR dongle. [Andy Milluzzi, KK4LWR, photo]QEX March/April 2017 1920 QEX March/April 2017operating system will most likely need a special driver to use the card as an SDR. Y ou can install the correct driver with assistance from the Zadig web page.2 The Zadig website has a simple guide for installing the WinUSB driver. This tutorial will assume you are using an RTL-SDR with the appropriate driver. The final needed hardware component for this tutorial is virtual. The DSD software needs a way to pass the audio. If you are using your computer sound card and an external radio, then you can skip this hardware. I recommend a VB-Audio Virtual Cable as a free solution.3 When you download and install the software, you should notice a new audio input and output device on your computer that acts as a sound card.Setting up DSDPlus SuiteDownload the latest version of DSDPlus and DSDPlus DLL package from the DSDPlus web page.4 Extract the contents of the DSDPlus zip file and the DLL zip file to a folder. Y ou should see a few dozen files. For this tutorial, we will focus on FMP-VC.bat and VC.bat. In DSDPlus two programs must be configured: FMP and DSDPlus. FMP is a basic narrowband FM tuner for an SDR. DSDPlus is the decoder.With all the files extracted, open a command prompt. In the Windows environment, this can be done by pressing the Windows key on your keyboard and typing C MD. Once open, navigate to the folder containing the DSDPlus files. Another option in Windows 8 or Windows 10 is to click on the File menu in your Explorer window. One of the options listed is open a command prompt. If done from the DSDPlus folder, you will not need to navigate.Setting up FMPOpen the file FMP-VC.bat. Y ou will see several parameters. Modify this script for our use by configuring the four parameters “–I”, “–o”, “–P”, and “–f”. The “–i” parameter followed by number (without a space) indicates which SDR to use as an input. For the SDR we can assume it is the only one on your computer, so set it to “–i1”. The “–o” parameter followed by a number is the output audio device. The “–P” parameter is the parts-per million (ppm) correction for your SDR. The “–f” parameter is the frequency in megahertz.To determine the values for the other parameters requires some knowledge about your setup. Let’s first tackle the output audio source. Each computer is different. The best way to determine the audio output is to observe what FMP sees. For this next part, you might find it helpful to unplug theSDR from the computer; if it is plugged inFigure 3 — Screen capture of FMP successfully running, controlling the SDR. Note thecommand prompt window showing the correct ppm correction and frequency.Figure 2 — Running FMP .EXE produces this text. Note the listed audio output devices.the program will launch. Type “FMP .EXE” in your command prompt window. Without an SDR plugged in, the application should fail to launch, but will still list the audio devices. For this program, we need to feed the output to our virtual audio port input. On my computer it is “Audio output device #2” seen in Figure 2.QEX March/April 2017 21Setting the ppm correction for your SDR is specific to your device. You can experiment by leaving it at 0.0. Alternatively you can use another SDR program such as SDR# from the AIRSPY web page to find the ppm correction.5 My device required a ppm correction of +75.The last parameter to set is the frequency to monitor. I do not want to clog the larger DMR network with my testing traffic, so I generated my own signals on 446.075 MHz, one of the UHF simplex frequency. DMR is mostly on UHF in the United States. Once the system is working, you can change the frequency to a local repeater.If done correctly, your FMP-VC.bat should look like:“FMP –i1 –o2 –P75 –f446.075”.Plug in your SDR tuner and run the script. Y ou should see several windows pop up. Y our computer screen should look like Figure 3. Save the changes to FMP-VC.bat. Y ou can close FMP by pressing the ESC key.Setting up DSDPlusC onfigure the DSDPlus script with a similar process. Open the VC.bat file and observe the various parameters. The parameters that start with a “w”:“–wsl”, “–wss”, “–wel”, and “–wcl”control where the windows are launched. Y ou can set these as you like.We must configure the audio as we did before by launching DSDPlus from our opencommand prompt. Unfortunately, there isFigure 5 — A screen capture of several windows of DSDPlus while decoding.Figure 4 — Running DSDPlus lists both input and output audio devices.no way to stop the program from opening all the windows, so you might need to move the various windows out of the way to see the command prompt and get your results. On my computer I got the results shown in Figure 4.The input should be set to the virtual audio cable output. The output must be your system speakers. In my case this results in input device #1 and output device #1 respectively. This enables me to hear anyone calling. A few other parameters must be set to make DMR work. The first parameter, “–rv”, tells DSDPlus that we expect voice. DSDPlus must also be set to decode DMR/MotoTURBO, since DSDPlus can do much more than just DMR — DSDPlus documentation indicates that it decodes D-STAR, except audio. It also can also decode P25 Phase 1 and NEXEDGE.To enable DMR we need to pass the “–fr” parameter. We also need to tell DSDPlus which of the two time slots we want tomonitor. This is done via passing “–1” or “–2” after the “–fr” parameter. Those are the only required parameters to make it work. You can record what DSDPlus decodes using the “–Pwav” parameter to save the audio as a wave file. Y ou might also discover a “–v3” parameter in the sample provided by DSDPlus. This enables verbose logging and I recommend using it, especially for debugging your scripts.When you are done, you should have a VC.bat script similar to:“DSDPlus –fr –1 –rv -Pwav –i1 –o1 –v3 –wsl400.210 –wss100.200 –wel172.522 –wcl528.0 >>VC.log”.Run VC.bat along with FMP-VC.bat and you should be able to decode DMR audio.Figure 5 is a screen capture containing several windows of information from my test transmission. If you look at the “DSD+ DMR VC Channel Activity” window you can see my target was Talk Group 99. The signal came from my radio programmed with 3112746, my DMR-MARC registered radio number. “The DSD+ VC event log” also reflects this same information. The “DSD...” window shows a trace of the audio signal. The most useful information comes from the command prompt script, lower left window. Y ou can also see DSDPlus initially locked on my signal before getting regular information. This is because my simplex mode has an “always” admit criteria. If we tweak our script to use slot two, the information for my signal would look the same in the command prompt, but no audio would play. This is because DSDPlus is expecting time slot two to provide the audio. We can also see my radio ID and the talk group in this window.Test Radio SetupTesting was done on low power andsimplex. I programmed my Tytera MD-380to use the standard Talk Group 99, TimeSlot 1, and Color Code 1, as found on theAmateur Radio guide on the DMR-MARCweb page.6 I also have the channel admitcriteria set to “always” since there is nosignal with which to sync up.ResultsThe setup easily decodes my DMR testsignals from my MD-380. Figure 5, showsthat DSDPlus is successfully decodingthe incoming DMR voice packets. Thesoftware successfully identifies key packetinformation, such as talk group, device ID,and so on. The audio output is clear and easyto understand. The software saves a “.wavfile” of the audio, enabling me to mute thespeakers while testing to avoid feedback.With the setup working correctly, I haveconfigured an old computer with the RTL-SDR to act as a DMR monitor for W4DFUrepeater. I used the time slot selection ofDSD+ to limit monitoring to time slot 2 (toavoid hearing the near constant traffic onNorth America or World Wide talk groups).This lets me hear local traffic and just a fewlarger area talk groups. The W4DFU repeateris part of the K4USD network. Details fortime slots and talk groups can be found atthe K4USD web page.7 I live a few milesfrom the W4DFU repeater and the smallstock antenna that came with the RTL-SDRis easily able to pick up the repeater frommy desk.Next StepsLike many hams, I am always learningsomething new. I love the challenge ofmastering a new technology. I am far froman expert on DMR, but I am having fundiscovering the features of this digital mode.This SDR scanner project is just one way togain a better understanding of DMR whilealso enabling a way to connect with otherusers.This tutorial was just the tip of the icebergin terms of software defined radio. Whilescanning DMR with DSDPlus is nothingnew, the software can be intimidating. Wehave just scratched the surface in whatDSDPlus can do and hopefully this willencourage you to experiment with all thefeatures or get started with DMR. Most of theDSDPlus documentation is in text files withthe software. Give it a try and see what youcan come up with!Andy Milluzzi, KK4LWR, is an AmateurExtra licensed ham, first licensed in 2012. Heis president of the Gator Amateur Radio Club,W4DFU, at the University of Florida. Andyis 2012 alumnus, receiving a BS in ComputerEngineering and a BS in Software Engineering,of the Rose-Hulman Institute of Technology inTerre Haute, Indiana. He is a PhD candidateand 2013 alumnus, receiving a MS inElectrical and Computer Engineering, at theUniversity of Florida in Gainesville, Florida.Andy loves how Amateur Radio affords himthe ability to tinker and relax, while stillincorporating his passion for engineering.Notes/2zadig.akeo.ie/3vb-audio.pagesperso-orange.fr//download-2//download//media/Amateur_Radio_Guide_to_DMR_Rev_I_20150510.pdf22 QEX March/April 2017。

TEA5767芯片说明书