Verilog常用分频器的实现

用VerilogHDL实现基于FPGA的通用分频器的设计.kdh

0引言在数字电路中,时钟脉冲信号是最重要的信号之一。

一个数字电路往往需要多种频率的脉冲作为驱动,通常采用一个高频晶振产生一种高频率的脉冲,再利用其它的分频方法进行分频,从而产生各种不同频率的脉冲,是一种常用的方法。

本文设计的分频器是采用Verilog HDL硬件描述语言,采用参数化的设计思想,在FPGA上实现的一种软件化的分频器,且该分频器仅占用FPGA的几个逻辑单元。

1通用分频器的设计分频器分为偶数分频、奇数分频、半整数分频和小数分频等,本文采用参数化的设计思想设计偶数分频器。

所谓参数化就是把程序中的某些参数设计成可以改变的量,使用户可以根据需要设定参数的值,以满足不同的需求。

1.1分频原理在设计偶数分频器时,采用通过一个由待分频时钟上升沿所触发的计数器循环计数来实现N倍(N为偶数)分频的实现方法,这种方法可以实现占空比为50%的任意偶数分频。

1.2设计方法在FPGA上,可以采用两种不同的Verilog HDL程序语句来设计计数器。

用这两种程序语句设计的计数器功能相同,但其实现方式不同,程序结构也不一样。

所以这两种程序语句编译综合后,它们占用的逻辑单元LE数差别很大。

本文对这两种程序语句进行了分析,比较了它们所占用的逻辑单元数的差别,并对产生这种差别的原因进行了分析。

(1)方法1module FPQ_1(CLK,OUT);input CLK;output OUT;parameter bitsize=4;//计数器二进制位数parameter L=9;//1/2倍的计数基数减1reg[bitsize:0]count=0;reg OUT=0;reg counter;always@(posedge CLK)begincount=(count<L)(count+1):0;//计数counter=(count==L)1:0;用Verilog HDL实现基于FPGA的通用分频器的设计Design of General Frequency Divider Based on FPGA Using Verilog HDL罗浩1许艳1,2仲佳嘉3Luo Hao Xu Yan Zhong Jiajia(1.江西理工大学应用科学学院,江西赣州341000;2.武汉理工大学信息学院,湖北武汉430070;3.江西赣州供电公司通信自动化分公司,江西赣州341000)(1.College of Applied Science,Jiangxi Univ.of Science&Technology,Jiangxi Ganzhou341000;2.School of Information Engineering,Wuhan Univ.of Technology,Hubei Wuhan430070;3.Branch of Communication and Automatization,JiangxiGanzhou Electric Power Corporation,Jiangxi Ganzhou341000)摘要:在数字逻辑电路设计中,常常遇到一些对时钟分频的需求。

Verilog HDL分频

你好,使用以下程序即可,使用时只需改变N值,N的取值大小请看注释,此程序适合对任意时钟的整数分频(包括奇偶),此程序已通过验证。

根据你的情况,想得到1HZ,N取50000000即可;想得到5HZ,N取10000000即可。

/****************************************************************************** ************Function: 实现时钟的任意整数分频******************************************************************************* *************/module div_N(inputCLK,// 基准时钟outputCLK_div_N// N分频后得到的时钟);wire[31:0]N=20;// N为分频系数,N≥2即可,N的值为CLK除以CLK_div_N后取整(四舍五入) /******************** 产生备用时钟1 ***************/reg[31:0]cnt1;regCLK_div_N_1;always @ (posedge CLK)beginif(N%2==0)// 如果N为偶数beginif(N==2)// 如果N为2CLK_div_N_1 <= ~CLK_div_N_1;elsebeginif(cnt1==(N-2)/2)begincnt1 <= 0;CLK_div_N_1 <= ~CLK_div_N_1;endelsecnt1 <= cnt1+1;endendelse// 如果N为奇数beginif(cnt1==N-1)cnt1 <= 0;elsecnt1 <= cnt1+1;if((cnt1==N-1) || (cnt1==(N-1)/2))CLK_div_N_1 <= ~CLK_div_N_1;else ;endend/*********************** 产生备用时钟2 *********************/wireCLK0=(N%2)? (~CLK):0;// 如果N为偶数,备用时钟2(CLK_div_N_2)恒为0,即不需要用到此备用时钟reg[31:0]cnt2;regCLK_div_N_2;always @ (posedge CLK0)beginif(cnt2==N-1)cnt2 <= 0;elsecnt2 <= cnt2+1;if((cnt2==N-1) || (cnt2==(N-1)/2))CLK_div_N_2 <= ~CLK_div_N_2;end/******************** 产生最终分频时钟************************/assignCLK_div_N = CLK_div_N_1 | CLK_div_N_2;endmodule。

实验六 Verilog设计分频器计数器电路答案

实验六Verilog设计分频器/计数器电路一、实验目的1、进一步掌握最基本时序电路的实现方法;2、学习分频器/计数器时序电路程序的编写方法;3、进一步学习同步和异步时序电路程序的编写方法。

二、实验内容1、用Verilog设计一个10分频的分频器,要求输入为clock(上升沿有效),reset(低电平复位),输出clockout为4个clock周期的低电平,4个clock周期的高电平),文件命名为fenpinqi10。

v.2、用Verilog设计一异步清零的十进制加法计数器,要求输入为时钟端CLK(上升沿)和异步清除端CLR(高电平复位),输出为进位端C和4位计数输出端Q,文件命名为coute r10.v。

3、用Verilog设计8位同步二进制加减法计数器,输入为时钟端CLK(上升沿有效)和异步清除端CLR(低电平有效),加减控制端UPDOWN,当UPDOWN为1时执行加法计数,为0时执行减法计数;输出为进位端C和8位计数输出端Q,文件命名为couter8.v。

4、用VERILOG设计一可变模数计数器,设计要求:令输入信号M1和M0控制计数模,当M1M0=00时为模18加法计数器;M1M0=01时为模4加法计数器;当M1M0=10时为模12加法计数器;M1M0=11时为模6加法计数器,输入clk上升沿有效,文件命名为mcout5。

v。

5、VerilogHDL设计有时钟时能的两位十进制计数器,有时钟使能的两位十进制计数器的元件符号如图所示,CLK是时钟输入端,上升沿有效;ENA是时钟使能控制输入端,高电平有效,当ENA=1时,时钟CLK才能输入;CLR是复位输入端,高电平有效,异步清零;Q[3.。

0]是计数器低4位状态输出端,Q[7..0]是高4位状态输出端;COUT是进位输出端.三、实验步骤实验一:分频器1、建立工程2、创建Verilog HDL文件3、输入10分频器程序代码并保存4、进行综合编译5、新建波形文件6、导入引脚7、设置信号源并保存8、生成网表9、功能仿真10、仿真结果分析由仿真结果可以看出clockout输出5个clock周期的低电平和5个clock的高电平达到10分频的效果,设计正确。

小数分频器的verilog-hdl设计

频率合成技术是现代通讯系统的重要组成部分,他将一个高稳定和高准确度的基准频率,经过四则运算,产生同样稳定度和基准度的频率。

分频器是集成电路中最基础也是最常用的电路。

整数分频器的实现比较简单,可采用标准的计数器或可编程逻辑器件设计实现。

但在某些场合下,时钟源与所需的频率不成整数倍关系,此时可采用小数分频器进行分频。

本文利用veriloghdl硬件描述语言的设计方式,通过modelsimse开发软件进行仿真,设计基于fpga的双模前置小数分频器。

随着超大规模集成电路的发展,利用fpga小数分频合成技术解决了单环数字频率合成器中高鉴相频率与小频间隔之间的矛盾。

1双模前置小数分频原理小数分频器的实现方法很多,但其基本原理一样,即在若干个分频周期中采取某种方法使某几个周期多计或少计一个数,从而在整个计数周期的总体平均意义上获得一个小数分频比,设要进行分频比为k的小数分频,k可表示为:式中:n,n,x均为正整数;n为到x的位数,即k有n位小数。

另一方面,分频比又可以写成:式中:m为分频器输入脉冲数;p为输出脉冲数。

令p=10n,则:以上是小数分频器的一种实现方法,即在进行10n次n分频时,设法多输入x个脉冲。

2电路组成每个周期分频n+10-n.x,其电路双模前置小数分频器电路由÷n/n+1双模分频器、控制计数器和控制逻辑3部分组成。

当a点电平为1时,进行÷n分频;当a点电平为0时进行÷n+1分频。

适当设计控制逻辑,使在10n个分频周期中分频器有x次进行÷n+1分频,这样,当从fo输出10n个脉冲时,在fi处输入了x.(n+1)+(10n-x).n个脉冲,也就是10n.n+x个脉冲,其原理如图1所示。

3小数分频器的verilog-hdl设计现通?过设计一个分频系数为8.7的分频器来给出使用veriloghdl语言设计数字逻辑电路的一般设计方法。

这里使用÷8/9双模前置分频器,按照前面的分析,可以通过计数器计数先做3次8分频,后做7次9分频,即可得到平均分频系数8.7。

verilog奇偶分频、一段式、两段式、三段式状态机

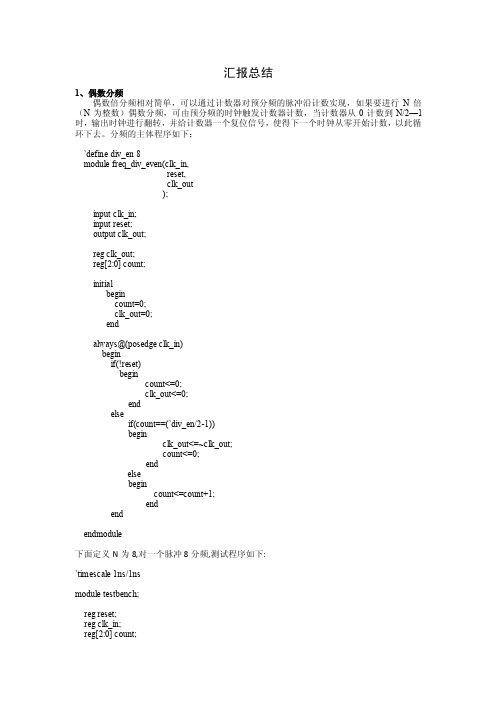

汇报总结1、偶数分频偶数倍分频相对简单,可以通过计数器对预分频的脉冲沿计数实现,如果要进行N倍(N为整数)偶数分频,可由预分频的时钟触发计数器计数,当计数器从0计数到N/2—1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数,以此循环下去。

分频的主体程序如下:`define div_en 8module freq_div_even(clk_in,reset,clk_out);input clk_in;input reset;output clk_out;reg clk_out;reg[2:0] count;initialbegincount=0;clk_out=0;endalways@(posedge clk_in)beginif(!reset)begincount<=0;clk_out<=0;endelseif(count==(`div_en/2-1))beginclk_out<=~clk_out;count<=0;endelsebegincount<=count+1;endendendmodule下面定义N为8,对一个脉冲8分频,测试程序如下:`timescale 1ns/1nsmodule testbench;reg reset;reg clk_in;reg[2:0] count;wire clk_out;freq_div_even test(.clk_in(clk_in),.reset(reset),.clk_out(clk_out));initialbeginreset=0;clk_in=0;#5 reset=1;endalways #10 clk_in=~clk_in;endmodule波形图如下:2、奇数分频对于对占空比没有特殊要求的奇数分频,需要对上升沿和下降沿脉冲进行计数,利用下降沿产生的波形移相半个输入脉冲的作用,最后用错位“异或”法实现。

verilog时钟分频设计

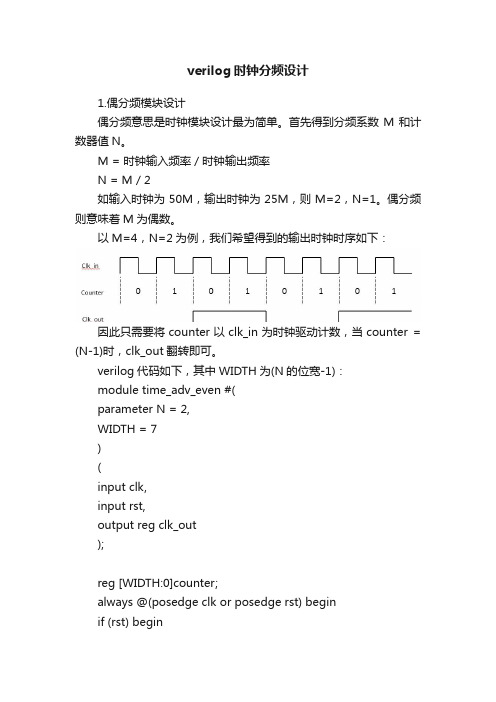

verilog时钟分频设计1.偶分频模块设计偶分频意思是时钟模块设计最为简单。

首先得到分频系数M和计数器值N。

M = 时钟输入频率 / 时钟输出频率N = M / 2如输入时钟为50M,输出时钟为25M,则M=2,N=1。

偶分频则意味着M为偶数。

以M=4,N=2为例,我们希望得到的输出时钟时序如下:因此只需要将counter以clk_in为时钟驱动计数,当counter = (N-1)时,clk_out翻转即可。

verilog代码如下,其中WIDTH为(N的位宽-1):module time_adv_even #(parameter N = 2,WIDTH = 7)(input clk,input rst,output reg clk_out);reg [WIDTH:0]counter;always @(posedge clk or posedge rst) beginif (rst) begin// resetcounter <= 0;endelse if (counter == N-1) begincounter <= 0;endelse begincounter <= counter + 1;endendalways @(posedge clk or posedge rst) beginif (rst) begin// resetclk_out <= 0;endelse if (counter == N-1) beginclk_out <= !clk_out;endendendmoduletestbench测试8分频即N=4,ISE仿真结果如下:2.奇分频模块设计奇分频需要通过两个时钟共同得到。

首先得到分频系数M和计数器值N。

M = 时钟输入频率 / 时钟输出频率N = (M-1) / 2如输入时钟为50M,输出时钟为10M,则M=5,N=2。

奇分频则意味着M为奇数。

N倍奇数分频器.(Verilog)

标签:Verilog分频器N倍奇数分频器.(V erilog)N_odd_divider.v / Verilogmodule N_odd_divider (input i_clk,input rst_n,output o_clk);parameter N = N_odd; // 设置奇数(除1外)倍分频parameter M = ?; // M="N/2"// bit_of_N: N_odd的二进制位宽reg [(bit_of_N - 1):0] cnt_p; // 上升沿计数单位reg [(bit_of_N - 1):0] cnt_n; // 下降沿计数单位reg clk_p; // 上升沿时钟reg clk_n; // 下降沿时钟assign o_clk = clk_n & clk_p; // 按位与(作用:掩码)// 上升沿计数器: 0~(N-1)always @ (posedge i_clk or negedge rst_n)beginif (!rst_n)cnt_p <= 0;elsebeginif (cnt_p == N-1)cnt_p <= 0;elsecnt_p <= cnt_p + 1'b1;endend// 生成上升沿时钟// 0~(N>>1) ↑ -> 1;((N/2)+1)~(N-1) ↑ -> 0 always @ (posedge i_clk or negedge rst_n) beginif (!rst_n)clk_p <= 0;elsebeginif (cnt_p <= M) // 0 ~ (N/2)clk_p <= 1;elseendend// 下降沿计数器: 0~(N-1)always @ (negedge i_clk or negedge rst_n) beginif (!rst_n)cnt_n <= 0;elsebeginif (cnt_n == N-1)cnt_n <= 0;elsecnt_n <= cnt_n + 1'b1;endend// 生成下降沿时钟// 0~(N>>1) ↓ -> 1;((N/2)+1)~(N-1) ↓ -> 0 always @ (negedge i_clk or negedge rst_n) beginif (!rst_n)elsebeginif (cnt_n <= M) // 0 ~ (N/2) clk_n <= 1;elseclk_n <= 0;endendendmodule仿真波形图1. N_odd = 3图2. N_odd = 5另见N倍偶数分频器.(Verilog)参考资料1. 真OO 无双的(原創) 如何設計除頻器? (SOC) (Verilog) (MegaCore)2. 位运算.(C)奇数倍分频(Verilog)奇数倍分频的方法:(以5分频为例)(n=N-1),图中,COUNT0采用上沿计数,COUNT1采用下沿计数,DIV0和DIV1是分别是上沿触发器和下沿触发器的输出,计数为0~(n/2-1)时DIV0、DIV1<='1'此处为0~1,计数为n/2~(n-1)时DIV0、DIV1<='0'此处为2~4,DIV5_CLK是DIV0和DIV1的或门输出。

分频器电路的Verilog设计

6. 偶数分频器的设计rate=even(偶数),占空比50%设计原理:定义一个计数器对输入时钟进行计数,(1)在计数的前一半时间里,输出高电平,(2)在计数的后一半时间里,输出低电平,这样输出的信号就是占空比为50%的偶数分频信号。

例如,设计一个6分频电路。

对什么计数?①计数值为0~2输出高电平,②计数值为3~5输出低电平。

上升沿计数一个计数周期0112分频module divder_even(clkin,clkout);parameter n=2;input clkin;output clkout;integer cnt;reg clkout;always@(posedge clkin)beginif(cnt<n-1) cnt<=cnt+1;else cnt<=0;endalways@(cnt)beginif(cnt<n/2) clkout<=1'b1;else clkout<=1'b0;end endmodule计数过程判断赋值过程module divder_even(clkin,clkout);parameter n=2;input clkin;output clkout;integer cnt;reg clkout;always@(posedge clkin)beginif(cnt==n/2-1)begincnt<=0;clkout<=~clkout;endelse cnt<=cnt+1;endendmodule 2分频分析4分频分析二分频四分频知识小结1.移位寄存器的verilog描述。

2.偶数分频的verilog描述。

作业1.设计一个5位串入并出的移位寄存器。

Clear :同步清零;clkin :时钟输入;databit :位输入y[4..0]并行数据输出;2.设计一个4位并入串出的移位寄存器Clear :同步清零;clkin :时钟输入(移位);dataIn :并行数据输入,y :串行数据输出。

Verilog HDL分频器设计报告

2011-2012第二学期专业选修课HDL语言应用与设计课程设计报告 Veriog HDL 分 频 器 设 计 报 告

设计时间: 2012.4 班级: 信科09-2 姓名: 程雷 学号: 08093534 指导老师: 王冠军 一、设计目的和要求: 目的: 1、学会使用Quantus软件(编译、仿真等),并利用它进行设计一些简单的数字电路; 2、 利用实验室提供的FPGA/CPLD实验箱,结合Quantus II软件实现分频器的功能。 要求:分频器可以简单实用的设置分频系数。

二、实验器件和环境 实验室提供的FPGA/CPLD实验箱,PC机和Quantus II软件。 三、设计方案和源程序代码 首先分析分频器要实现的功能,然后确定他的基本结构,因为分频器的基本功能要使其分频的的功能可以控制,所以要有控制使能端口;分频器的分频系数可以自由选择,所以应有分频系数设置使能端;分频之后可以输出分频之后的频率,所以应该有输出端口。本本设计只是任意整数分频器。 1、偶数倍分频:偶数倍分频,通过计数器计数是完全可以实现的。如进行N倍偶数分频,那么可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数。以此循环下去。这种方法可以实现任意的偶数分频。

原理:比如4分频,需要一个模4的计数器,占空比50%,计数为0~3循环,当计数到一半时,即计数输出cnt<2时翻转。

例题代码如下: //四分频 module div4(clk,rst_n,o_clk); input clk,rst_n; output o_clk; reg o_clk; reg [1:0]cnt; always @(posedge clk or negedge rst_n) begin if(!rst_n) cnt<=0; else if(cnt==3) cnt<=0; else cnt<=cnt+1; end always @(posedge clk or negedge rst_n) begin if(!rst_n) o_clk<=0; else if(cnt<2) o_clk<=1; else o_clk<=0; end endmodule 仿真结果:

分频器设计——50MHZ(含verilog程序)

分频器设计一、实验目的1、熟悉分频器的原理;2、掌握采用Verilog HDL 语言设计分频器的方法;3、进一步学习利用VerilogHDL 语言进行层次设计的方法。

二、实验内容1、采用Verilog 语言设计一个十分频器,记录Verilog 程序;2、对十分频器进行功能仿真,观察仿真波形;3、仿真没有问题后,将分频比改为50000000,实现一个50M 分频器。

利用此分频器和开发板上的50MHz 时钟信号,得到1Hz 的秒脉冲信号,完成如图1-2.28所示的秒计数器。

50M分频器50MHz 脉冲信号二位十进制计数器1Hz 秒脉冲数码管(个位)数码管(十位)复位和计数使能(拨码开关)程序设计如下:module fenp(clk_out,clk_in,reset);output clk_out;input clk_in;input reset;reg [1:0] cnt;reg clk_out;always@(posedge clk_in or posedge reset)beginif(reset)begincnt<=0;clk_out<=0;endelsebeginif(cnt==24999999)beginclk_out<=!clk_out;cnt<=0;endelsecnt<=cnt+1;endendendmodule本程序经验证,完全可以实现实验要求。

文章来自某大学EDA实验课。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Verilog常用分频器的实现

分频器是指使输出信号频率为输入信号频率整数分之一的电子电路。

在许多电子设备中如电子钟、频率合成器等,需要各种不同频率的信号协同工作,常用的方法是以稳定度高的晶体振荡器为主振源,通过变换得到所需要的各种频率成分,分频器是一种主要变换手段。

早期的分频器多为正弦分频器,随着数字集成电路的发展,脉冲分频器(又称数字分频器)逐渐取代了正弦分频器。

下面以Verilog HDL语言为基础介绍占空比为50%的分频器。

1.偶分频

偶分频比较简单,假设为N分频,只需要计数到N/2‐1,然后时钟翻转、计数清零,如此循环就可以得到N(偶)分频。

代码如下。

module fp_even(clk_out,clk_in,rst);

input clk_in,rst;

output clk_out;

reg [7:0] cnt;

reg clk_out;

`define N 6

always@(posedge clk_in or negedge rst)

begin

if(!rst)

begin

cnt<=0;

clk_out<=0;

end

else begin

if(cnt==`N/2‐1)

begin

clk_out<=~clk_out;

cnt<=0;

end

else cnt<=cnt+1;

end

end

endmodule

2.奇分频

实现奇数分频(N)分频,分别用上升沿到(N-1)/2,再计数到N-1;用下降沿计数到(N-1)/2,再计数到N-1。

得到两个波形,然后把它们相或即可得到N分频。

代码如下。

module fp_odd(clk_in,clk_out,rst,clk_neg,clk_pos);

input clk_in,rst;

output clk_out,clk_pos,clk_neg;

reg [7:0] cnt_pos,cnt_neg;

reg clk_pos,clk_neg;

`define N 5

always@(posedge clk_in or negedge rst) //从零到N‐1不停地循环计数(上升沿)

begin

if(!rst) cnt_pos<=0;

else if(cnt_pos==`N‐1) cnt_pos<=0;

else cnt_pos<=cnt_pos+1;

end

always@(posedge clk_in or negedge rst)

begin

if(!rst) clk_pos<=0;

else if( cnt_pos==(`N‐1)/2 ) clk_pos<=~clk_pos;

else if(cnt_pos==`N‐1) clk_pos<=~clk_pos;

end

always@(negedge clk_in or negedge rst) //从零到N‐1不停地循环计数(下降沿)

begin

if(!rst) cnt_neg<=0;

else if(cnt_neg==`N‐1) cnt_neg<=0;

else cnt_neg<=cnt_neg+1;

end

always@(negedge clk_in or negedge rst)

begin

if(!rst) clk_neg<=0;

else if( cnt_neg==(`N‐1)/2 ) clk_neg<=~clk_neg;

else if(cnt_neg==`N‐1) clk_neg<=~clk_neg;

end

assign clk_out=clk_neg|clk_pos;

endmodule

3.任意占空比的任意分频

在 verilog程序设计中,我们往往要对一个频率进行任意分频,而且占空比也有一定的要求。

现在在前面两个实验的基础上做一个简单的总结,实现对一个频率的任意占空比的分频。

比如:FPGA系统时钟是50MHz,而我们要产生的频率是880Hz,那么我们而要对系统时钟进行分频。

很容易想到用计数的方法来分频:50000000/800=56818。

显然这个数字不

是2的整幂次方,那么我们可以设定一个参数,让它到56818的时候重新计数就可以实现了。

程序如下:

module div(clk, clk_div);

input clk;

output clk_div;

reg [15:0] counter;

always @(posedge clk) if(counter==56817) counter <= 0; else counter <= counter+1;

assign clk_div = counter[15];

endmodule

下面我们来算一下它的占空比:我们清楚地知道,这个输出波形在counter为0到32767的时候为低,在32767到56817的时候为高,占空比为40%多一些,如果我们需要占空比为50%,那么怎么办呢?不用急,慢慢来。

我们再设定一个参数,使它为56817的一半,使达到它的时候波形翻转,那不就完了吗?呵呵,再看看:

module div(clk, clk_div);

input clk;

output clk_div;

reg [14:0] counter;

always @(posedge clk) if(counter==28408) counter <= 0; else counter <= counter+1;

reg clk_div;

always @(posedge clk) if(counter==28408) clk_div <= ~clk_div;

endmodule

占空比是不是神奇地变成50%了呢?呵呵。

继续让我们来看如何实现任意占空比,比如还是由50 M 分频产生880 Hz,而分频得到的信号的占空比为30%。

56818×30%=17045

module div(clk,reset,clk_div,counter);

input clk,reset;

output clk_div;

output [15:0] counter;

reg [15:0] counter;

reg clk_div;

always @(posedge clk)

if(!reset) counter <= 0; else if(counter==56817) counter <= 0; else counter <= counter+1; always @(posedge clk)

if(!reset) clk_div <= 0; else if(counter<17045) clk_div <= 1;else clk_div <= 0;

endmodule。