数字逻辑课程设计

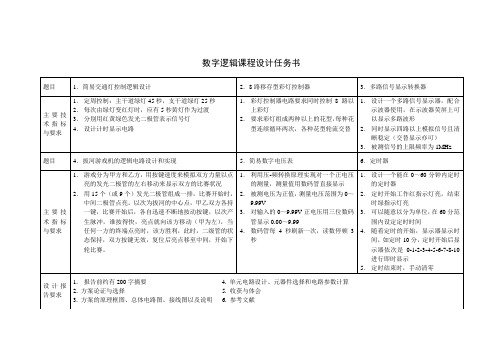

数字逻辑课程设计任务书

2.同时显示四路以上模拟信号且清晰稳定(交替显示亦可)

3.被测信号的上限频率为1MHz

题目

4.拔河游戏机的逻辑电路设计和实现

5.简易数字电压表

6.定时器

主要技术指标与要求

1.游戏分为甲方和乙方,用按键速度来模拟双方力量以点亮的发光二极管的左右移动来显示双方的比赛状况

4.设置犯规电路,对提前抢答和超时的组鸣喇叭示警,并显示犯规组号

1.设计秒信号0.1分信号脉冲产生器

2.选用十进制系数乘法器

3.设计四级BCD码计数、译码和显示器

4.选用产生行驶里程信号的继电器作为脉冲产开关电路用来改变里程单价

题目

10.数字时钟

11.限时发言时间提示器

1.设计一个用于四组参赛者的数字智力抢答器,每组设置一个抢答按钮供参赛者使用

2.电路具有第一抢答信号的鉴别和锁存功能,在主持人将系统复位后并发出指令后,若一组第一个按下开关抢答,则该组指示灯亮,并显示组号,同时,扬声器同时发出2~3秒的声音,电路具有自锁功能,使其余组的抢答开关不起作用

3.设置记分电路,开始时每组预置成100分,抢答后由主持人记分,答对一次加10分,否则减10分

2.用15个(或9个)发光二极管组成一排,比赛开始时,中间二极管点亮。以次为拔河的中心点,甲乙双方各持一键,比赛开始后,各自迅速不断地按动按键,以次产生脉冲,谁按得快,亮点就向该方移动(甲为左),当任何一方的终端点亮时,该方胜利,此时,二级管的状态保持,双方按键无效,复位后亮点移至中间,开始下轮比赛。

题目

1.简易交通灯控制逻辑设计

2.8路移存型彩灯控制器

3.多路信号显示转换器

数字逻辑与数字系统设计课程设计

数字逻辑与数字系统设计课程设计一、课程设计背景数字逻辑与数字系统设计课程介绍了数字电路的基本概念、设计和分析方法。

数字逻辑是电子技术中非常重要的一部分,广泛应用于计算机、通信、自动化控制、计算器、游戏机等电子产品。

通过本课程的学习,学生将掌握数字逻辑和数字系统设计的基本原理和方法。

二、课程设计内容本次数字逻辑与数字系统设计课程设计主要分为以下几个部分:1.实验一:Karnaugh图和逻辑多路选择器设计实验2.实验二:数字逻辑电路的组合设计实验3.实验三:数字电路的时序设计实验4.实验四:数字系统设计实验5.实验五:数字逻辑综合设计实验实验一:Karnaugh图和逻辑多路选择器设计实验通过本实验,学生将学会运用Karnaugh图方法设计简单的逻辑电路,掌握最小化布尔函数的方法。

同时,学生将学习多路选择器的设计方法,掌握多路选择器的应用技巧。

实验二:数字逻辑电路的组合设计实验通过本实验,学生将学习的是数字逻辑电路的组合设计方法,包括基本逻辑门和复杂逻辑电路的设计技术。

同时,学生还将掌握基本电路的仿真方法,通过仿真软件对电路进行验证。

实验三:数字电路的时序设计实验在本实验中,学生将掌握数字电路的时序设计方法,了解时序电路的作用、分类和基本原理。

同时,学生将学习数字电路时序仿真的方法,能够进行基本时序电路模拟。

实验四:数字系统设计实验在本实验中,学生将学习数字系统设计的基本方法和过程,包括总体结构设计、输入输出接口的设计、存储器的设计等;同时,学生还将了解数字系统的仿真和测试方法,对设计的数字系统进行仿真和测试。

实验五:数字逻辑综合设计实验在本实验中,学生将通过数字逻辑综合设计,掌握数字逻辑综合应用技巧,并能够在实践中学习根据需求进行电路综合的方法。

三、课程设计特点本次数字逻辑与数字系统设计课程设计不仅注重理论教学,更加强调实践教学,特点如下:1.注重实验教学,对学生的动手能力和实践能力进行提高。

2.充分利用仿真软件进行电路设计和验证,使学生在熟悉实际电路设计方法的同时,也能提高计算机仿真的技能和水平。

数字逻辑课程设计

数字逻辑课程设计一、课程设计目的《数字逻辑课程设计》是计算机大类学生的必修课之一,是《数字逻辑》课程的一个重要的实践教学环节,它与理论教学和实验教学相结合,培养学生综合运用所学的基础理论和掌握的基本技能来解决实际问题的能力。

课程设计通过完成一个课题的理论设计和实际调试工作,即能加深对所学知识的理解,又能培养综合的实践技能,从而提高分析问题和解决问题的能力。

训练学生综合运用学过的数字逻辑的基本知识,独立设计比较复杂的数字电路的能力。

通过实践教学引导学生在理论指导下有所创新,为专业课的学习和日后工程实践奠定基础。

二、课程设计要求(一)教学要求1.巩固和加深对数字逻辑各类型电路的设计方法及电子器件所构成电路的理解,并适当拓宽学生在电子线路领域的知识面。

2.初步掌握数字电路的设计、计算方法。

能根据系统的技术指标,论证、拟订设计方案;选用合适的电路形式并进行工程计算及选择电路的元器件。

3.培养独立组织实验方案、正确选择使用实验仪器的能力,提高对功能电路和系统的安装调整、测试技术,以及综合运用所学理论知识解决实际问题的能力。

(二)能力培养要求1.通过查阅手册和有关文献资料培养学生独立分析和解决实际问题的能力。

2.通过实际电路方案的比较分析、设计计算、元件选取、安装调试等环节,掌握简单实用电路的分析方法和工程设计方法。

3.掌握常用仪器设备的使用方法,学会简单的实验调试,提高动手能力。

4.综合应用课程中学到的理论知识去独立完成一个设计任务。

5.培养严肃认真的工作作风和严谨的科学态度。

三、课程设计内容从参考题目中自选1题进行资料查找和设计,具体课题及要求见附件1。

1.数码管显示控制器2.乒乓球游戏机3.智力竞赛抢答器4.数字钟5.交通灯控制器四、设计报告的内容和要求报告的内容包括以下几个方面:1、课程设计题目:自选题目名称2、设计任务及主要性能指标和要求3、电路的设计(1)根据功能要求构建总体设计方案,比较和选定设计的系统方案,确定整个电路的组成及各单元电路完成的功能,画出系统框图。

数字逻辑课程设计——111序列检测器

课程设计课程名称数字逻辑设计题目“1 1 1”序列检测器专业计算机科学与技术专业班级0706姓名孙禹指导教师巩晶2009 年06 月28 日课程设计任务书学生姓名孙禹学生专业班级计算机 0706指导教师巩晶学院名称计算机科学与技术学院一、题目:“1 1 1”序列检测器。

原始条件:使用D触发器( 74 LS 74 )、“与”门( 74 LS 08 )、“或”门( 74 LS 32 )、非门( 74 LS 04 ),设计“1 1 1”序列检测器。

二、要求完成设计的主要任务如下:1.能够运用数字逻辑的理论和方法,把时序逻辑电路设计和组合逻辑电路设计相结合,设计一个有实际应用的数字逻辑电路。

2.使用同步时序逻辑电路的设计方法,设计“1 1 1”序列检测器。

写出设计中的5个过程。

画出课程设计图。

3.根据74 LS 74、74 LS 08、74 LS 32、74 LS 04集成电路引脚号,在设计好的“1 1 1”序列检测器电路图中标上引脚号。

4.在试验设备上,使用74 LS 74、74 LS 08、74 LS 32、74 LS 04集成电路连接、调试和测试“1 1 1”序列检测器电路。

指导教师签名:2009 年6 月29 日系主任(责任教师)签名:2009 年月日一、实验目的:1、深入了解与掌握同步时序逻辑电路的设计过程;2、了解74LS74、74LS08、74LS32及74LS04芯片的功能;3、能够根据电路图连接好实物图,并实现其功能。

学会设计过程中的检验与完善。

二、实验内容描述:题目:“1 1 1”序列检测器。

原始条件:使用D触发器( 74 LS 74 )、“与”门( 74 LS 08 )、“或”门( 74 LS 32 )、非门( 74 LS 04 ),设计“1 1 1”序列检测器。

集成电路引脚图:D触发器( 74 LS 74 ) “与”门( 74 LS 08 )“或”门( 74 LS 32 ) 非门( 74 LS 04 )三、实验设计过程:第1步,画出原始状态图和状态表。

北邮数字逻辑课程设计..

CLK q3 q2 q1 q0

× 0 0 0 0 上升 预置值 上升 计数值加1 × 保持不变

同步预置为 “1010”

仿真波形 counter16.vhd

简易电子琴

音符 (C)

1

2

3

4

5

6

7

i

频率(Hz) 262 294 330 349 392 440 494 523

输入的主频=100KHz 不同的键对100KHz进行分频

实验要求

●熟练掌握isp EXPERT软件的使用方法

●熟练掌握isp器件的使用方法

●熟练掌握用VHDL进行数字逻辑电路设计 ●熟练掌握isp器件的下载方法 ●认真写出课程设计报告 ●7月7日~7月17日在实验室完成四个实验

实验要求

信号流程 Multimedia

输入信号

→

I/O单元 → 全局布线

→ 通用逻辑单元 →

A B

S Co

实体说明、结构体格式

四位二进制同步计数器 areset R sset S enable EN CLK clk

R 1 0 0 0 S × 1 0 0 EN × × 1 0

CO Q0 Q1 Q2 Q3

cout

q0 q1 q2 q3

LIBRARY IEEE; 标准无符号 USE IEEE.std_logic_1164.ALL; 类型程序包 USE IEEE.std_logic_arith.ALL; USE IEEE.std_logic_unsigned.ALL; ENTITY counter IS PORT (clk, areset, sset ,enable : IN std_logic; cout : OUT std_logic; q : BUFFER std_logic_vector(3 DOWNTO 0)); END counter; ARCHITECTURE rtl_arc OF counter IS BEGIN PROCESS (clk,areset) BEGIN IF (areset ='1') THEN q <= '0'; ELSIF (clk'event AND clk ='1') THEN IF (sset ='1') THEN q <= "1010"; ELSIF (enable ='1') THEN q <= q +1; ELSE q <= q; END IF; END IF; END PROCESS; cout <= '1' WHEN q = "1111" AND enable ='1' ELSE '0'; END rtl_arc;

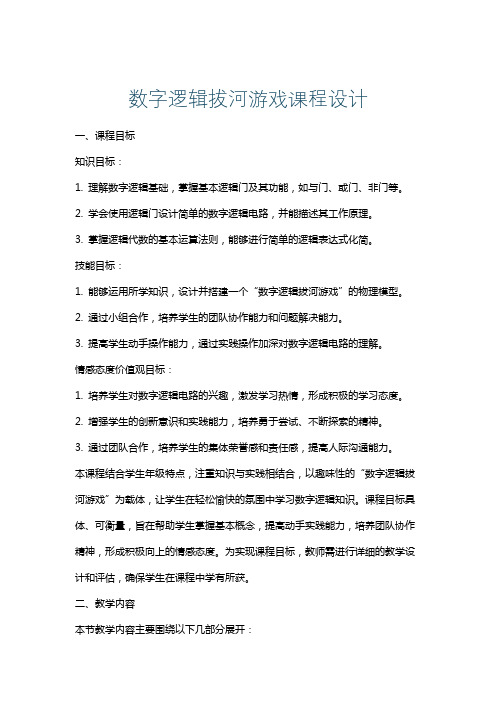

数字逻辑拔河游戏课程设计

数字逻辑拔河游戏课程设计一、课程目标知识目标:1. 理解数字逻辑基础,掌握基本逻辑门及其功能,如与门、或门、非门等。

2. 学会使用逻辑门设计简单的数字逻辑电路,并能描述其工作原理。

3. 掌握逻辑代数的基本运算法则,能够进行简单的逻辑表达式化简。

技能目标:1. 能够运用所学知识,设计并搭建一个“数字逻辑拔河游戏”的物理模型。

2. 通过小组合作,培养学生的团队协作能力和问题解决能力。

3. 提高学生动手操作能力,通过实践操作加深对数字逻辑电路的理解。

情感态度价值观目标:1. 培养学生对数字逻辑电路的兴趣,激发学习热情,形成积极的学习态度。

2. 增强学生的创新意识和实践能力,培养勇于尝试、不断探索的精神。

3. 通过团队合作,培养学生的集体荣誉感和责任感,提高人际沟通能力。

本课程结合学生年级特点,注重知识与实践相结合,以趣味性的“数字逻辑拔河游戏”为载体,让学生在轻松愉快的氛围中学习数字逻辑知识。

课程目标具体、可衡量,旨在帮助学生掌握基本概念,提高动手实践能力,培养团队协作精神,形成积极向上的情感态度。

为实现课程目标,教师需进行详细的教学设计和评估,确保学生在课程中学有所获。

二、教学内容本节教学内容主要围绕以下几部分展开:1. 数字逻辑基础:讲解基本逻辑门(与门、或门、非门等)的功能和原理,使学生掌握数字逻辑电路的基本组成。

2. 逻辑代数:介绍逻辑代数的基本运算法则,包括与、或、非等操作,以及逻辑表达式的化简方法。

3. 数字逻辑电路设计:教授如何使用基本逻辑门设计简单的数字逻辑电路,并结合实际案例进行分析。

4. 数字逻辑拔河游戏设计:结合所学知识,指导学生设计并搭建一个具有趣味性的数字逻辑拔河游戏物理模型。

具体教学内容安排如下:1. 第一阶段:数字逻辑基础(1课时)- 介绍基本逻辑门及其功能- 分析基本逻辑门的工作原理2. 第二阶段:逻辑代数(1课时)- 讲解逻辑代数基本运算法则- 举例说明逻辑表达式的化简方法3. 第三阶段:数字逻辑电路设计(2课时)- 分析实际案例,教授设计方法- 学生自主设计简单的数字逻辑电路4. 第四阶段:数字逻辑拔河游戏设计(2课时)- 分组讨论,确定设计方案- 学生动手实践,搭建数字逻辑拔河游戏模型教学内容与教材紧密关联,按照教学大纲逐步推进,确保学生能够扎实掌握数字逻辑知识,提高实践能力。

数字逻辑课程设计报告(优秀版)

目录目录 (1)一、设计目的 (2)二、设计要求 (2)三、设计方案 (2)四、顶层图及相关模块说明 (3)1、顶层图 (3)2、各模块说明(1)进制模块 (3)a、二十四进制 (5)b、六十进制 (5)(1)动态扫描模块 (6)(2)分频模块 (8)(3)报时模块 (9)(4)二路选择器模块 (10)五、经验总结 (12)一、设计目的1.学会应用数字系统设计方法进行电路设计;2.进一步提高QuartusⅡ9.0软件的开发应用能力;3.培养学生书写综合实验报告的能力。

二、设计要求1、能进行正常的时、分、秒计时,用动态扫描的方式显示,需用6个数码管。

(1)用M6M5进行24进制小时的显示。

(2)用M4M3进行60进制分的显示。

(3)用M2M1进行60进制秒的显示。

2、利用按键实现“校时”、“校分”和“秒清0”功能。

(1)SA:校时键。

按下SA键时,时计数器迅速递增,按24小时循环,并且计满23时回到00。

(2)SB:校分键。

按下SB键时,分计数器迅速递增,按60小时循环,并且计满59时回到00,但不向时进位。

(3)SC:秒清零。

按下SC时,秒计数器清零。

要求按键均不产生数字跳变,因此须对“SA”、“SB”进行消抖处理。

3、能进行整点报时。

(1)在59分50、52、54、56、58秒按500Hz频率报时;(2)在59分60秒用1KHz的频率作最后一声正点报时。

4、更高要求:能进行闹时功能(1)闹时的最小时间间隙为10分钟,闹时长度为1分钟。

闹时频率可以自己设置。

(2)按下闹时按键SD后,将一个闹时时间数存入计数器内。

时钟正常运行时,闹时时间和运行的时间进行比较,当比较结果相同时输出一个启动信号,触发闹时电路工作,输出音频信号。

三、设计方案1、按自顶向下的层次化设计方法设计。

(1)顶层图(2)消抖电路用D触发器构成,SA、SB、SC为包含抖动的输入信号,而电路的输出则是一个边沿整齐的输出信号。

(3)计时(24进制计数器),计分(60进制计数器)、计秒(60进制计数器)模块可由10进制计数器连接构成,也可用VHDL语言完成。

数字逻辑课程设计完整报告(精编文档).doc

【最新整理,下载后即可编辑】一、概述智能抢答器是一种生活中常见的装置,电视节目中都可以看得到,是一种简易但又特别实用的一种装置。

本次我的课程设计的要求是设计一个智力竞赛抢答装置,可以供4人(组)使用,并且每人对应着一个开关,每个开关对应着一个发光二极管,当选手抢答成功时,所对应的发光二极管就会亮,主持人也有一个开关,当主持人按下自己开关使,选手才可以抢答,比赛才开始,并且计时器开始计时,如果在2分钟时间内没有选手抢答,那么这道题作废,主持人断开自己开关,再进行下道题。

二、方案论证设计一个智能抢答器,可以供4人比赛,每人对应一个开关和发光二极管。

主持人控制一个开关,当主持人按下开关,抢答开始并且开始计时,如果2分钟内没有选手抢答,那么本题作废,主持人断开开关,进行下题。

方案一:方案一原理框图如图1所示。

图1 智力抢答器电路的原理框图方案二:方案二原理框图如图2所示。

图2 智力抢答器电路的原理框图本设计采用的是方案二,电路简单,易懂,更具性价比。

三、电路设计 1.抢答电路抢答电路是实现抢答功能,当主持人按下开关抢答开始,当最先开始选手按下开关并且对应发光二极管发光,而且其他选手抢答无效。

为实现功能当一个开关闭合同时其它开关处于断开状态时,输出高电平对应二极管发光,同时将其它三个二极管锁定为低电平,这三个开关失效。

图3 抢答电路2.计时电路计时器电路主要由三片74LS190N 构成。

将三片计数器芯片接成120进制的加法计数器并将初始值置为000,接收脉冲信号由000开始计时。

选手按钮显示电路译码电路 控制电路主持人按钮脉冲电路计时电路 报警电路表1 同步十进制加/减计数器74LS190N功能表的控制停止计数且保持当前数据不变;当LD′=0时,计数器不受CLK的控制预置数;当CTEN′=0,LD′=1,U′/D=0时计数器加法计数,CTEN′=0,LD′=1,U′/D=1时计数器减法计数;当低位计数器U8到9时进位,高位加1。

数字逻辑课程设计速度表

数字逻辑课程设计速度表一、教学目标本课程的教学目标是使学生掌握数字逻辑的基本概念、原理和方法,培养学生运用数字逻辑分析和解决实际问题的能力。

具体目标如下:1.知识目标:学生能够理解数字逻辑的基本概念,掌握逻辑门、逻辑函数、逻辑电路的设计与分析方法,了解数字逻辑在计算机硬件中的应用。

2.技能目标:学生能够运用数字逻辑设计简单的电路,进行逻辑函数的化简和优化,并能使用相关工具软件进行电路仿真。

3.情感态度价值观目标:培养学生对计算机科学的兴趣,提高学生分析问题和解决问题的能力,培养学生的创新精神和团队合作意识。

二、教学内容本课程的教学内容主要包括以下几个部分:1.数字逻辑基本概念:数字逻辑电路的定义、分类和特点,逻辑门的概念及其分类,逻辑函数的定义和性质。

2.逻辑电路的设计与分析:逻辑电路的绘制方法,逻辑门电路的功能和特性,逻辑函数的化简方法,卡诺图的应用。

3.数字逻辑电路的应用:组合逻辑电路的设计与分析,时序逻辑电路的设计与分析,数字电路仿真。

4.数字逻辑在计算机硬件中的应用:计算机的基本组成原理,中央处理器(CPU)的结构和工作原理,存储器的分类和特点。

三、教学方法本课程采用讲授法、讨论法、案例分析法和实验法等多种教学方法,以激发学生的学习兴趣和主动性。

1.讲授法:通过讲解使学生掌握数字逻辑的基本概念、原理和方法。

2.讨论法:学生进行小组讨论,培养学生分析问题和解决问题的能力。

3.案例分析法:分析实际案例,使学生了解数字逻辑在计算机硬件中的应用。

4.实验法:让学生动手设计、搭建和测试数字逻辑电路,提高学生的实践能力。

四、教学资源本课程的教学资源包括教材、参考书、多媒体资料和实验设备等。

1.教材:选用权威、实用的教材,为学生提供系统的学习资料。

2.参考书:提供丰富的参考资料,帮助学生拓展知识面。

3.多媒体资料:制作精美的课件,为学生提供直观的学习体验。

4.实验设备:配置齐全的实验设备,为学生提供实践操作的机会。

数字逻辑课程设计任务书

数字逻辑课程设计任务书一教学目标<一> 课程性质数字电子技术课程设计是学生的专业基础课。

课程设计是以实验为基础在教师指导下独立查阅资料、设计和调试特定功能的电子电路。

课程设计对于提高学生的电子工程素质和科学实践能力非常重要,是由学生自行设计和自行调试的综合性训练。

<二> 课程目的训练学生综合地运用所学的<模拟电子技术><数字电子技术>的基本知识,独立、完整地设计一定功能的电子电路,并培养设计软件应用和仿真等综合能力。

二、设计内容基本要求〈一〉课程设计题目1、多功能数字钟设计基本要求:1)由振荡器输出稳定的高频脉冲信号作为时间基准,经分频器输出标准的秒脉冲。

2)秒计数器满60向分计数器进位,分计数器满60向小时计数器进位,小时计数器按“12翻1”规律计数,计数器经译码器送到显示器。

3)计数出现误差可用校时电路进行校时、校分、校秒。

扩展要求:4)具有可整点报时与定时闹钟的功能。

2、数字式竞赛抢答器基本要求:1)给主持人设置一个控制按钮,用来控制系统清零(抢答显示数码管灭灯)和抢答的开始。

2)4名选手编号为:1,2,3,4。

各有一个抢答按钮,按钮的编号与选手的编号对应,也分别为1,2,3,4。

3)抢答器具有数据锁存和显示的功能。

抢答开始后,若有选手按动抢答按钮,该选手编号立即锁存,抢答显示器上显示该编号,同时扬声器给出音响提示,封锁输入编码电路,禁止其他选手抢答。

4)抢答器具有定时(9秒)抢答的功能。

当主持人按下开始按钮后,定时器开始显示倒计时间,若无人抢答,倒计时结束时,扬声器响持续1秒。

参赛选手在设定时间(9秒)内抢答有效,抢答成功,扬声器响持续1秒,同时定时器停止倒计时,抢答显示器上显示选手的编号,定时显示器上显示剩余抢答时间,并保持到主持人将系统清零为止。

5)如果抢答定时已到,却没有选手抢答时,本次抢答无效。

系统扬声器报警(音响持续1秒),并封锁输入编码电路,禁止选手超时后抢答,时间显示器显示0。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第一题part1: 1. 问题的描述: Using the Xilinx Verilog tools and the Nexys3 board, create and download a circuit that can connect the lower four slide switches to logic functions driving the lower four LEDs, the upper four slide switches directly to the upper four LEDs, and the pushbuttons to the seven-segment display anodes through inverters. The lower four slide switches should use the logic functions: assign LD0 = ~SW0; assign LD1 = SW1 & ~SW2; assign LD3 = SW2 & SW3; assign LD2 = LD1 | LD3; Note that a logic '0' on the seven-segment cathode connection will turn that cathode "on", and likewise, a logic '0' on an anode signal will turn the corresponding anode "on" (i.e., both the anode and cathode signals are active low). After completing the source file to describe the circuit, but before implementing or downloading the design to the Nexys3 bociate the logic signals in your design with physical pins on the FPGA. This association can be created using a “.ucf” file. Guidance and instructions on creating and using a .ucf file can be found in the ISE tutorial, and will be presented during an in-class discussion. 2.verilog语言描述 (1) . module test_sj1(

input wire[7:0]Lw, input wire[3:0]Bn, output wire[7:0]Lk, output wire[3:0]Ag, output wire[6:0]Gf ); assign Lk[0]=~Lw[0]; assign Lk[1]=Lw[1]&~Lw[2]; assign Lk[3]=Lw[2]&Lw[3]; assign Lk[2]=Lk[1]&Lk[3]; assign Lk[4]=Lw[4]; assign Lk[5]=Lw[5]; assign Lk[6]=Lw[6]; assign Lk[7]=Lw[7]; assign Ag[0]=~Bn[0]; assign Ag[1]=~Bn[1]; assign Ag[2]=~Bn[2]; assign Ag[3]=~Bn[3]; assign Gf=7'b0000000; endmodule

(2).测试仿真代码: module test1; // Inputs reg [7:0] Lw; reg [3:0] Bn; // Outputs wire [7:0] Lk; wire [3:0] Ag; wire [6:0] Gf; // Instantiate the Unit Under Test (UUT) project1_1uut ( .Lw(Lw), .Bn(Bn), .Lk(Lk), .Ag(Ag), .Gf(Gf) ); initial begin // Initialize Inputs Lw = 0; Bn = 0; // Wait 100 ns for global reset to finish #100; Lw=8'b00000000; Bn=4'b0000; // Add stimulus here以下写测试代码段 #100; Lw=8'b00000001; #100; Lw=8'b00000010; #100; Lw =8'b00000100; #100; Lw =8'b00001000; #100; Lw =8'b00010000; #100; Lw =8'b00100000; #100; Lw =8'b01000000; #100; Lw =8'b10000000; #100; Bn=4'b0001; #100; Bn=4'b0010; #100; Bn=4'b0100; #100; Bn=4'b1000; end endmodule

3.实验结果截屏:

4.约束文件:

NET "Lw[0]" LOC = "T10"; NET "Lw[1]" LOC = "T9"; NET "Lw[2]" LOC = "V9"; NET "Lw[3]" LOC = "M8"; NET "Lw[4]" LOC = "N8"; NET "Lw[5]" LOC = "U8"; NET "Lw[6]" LOC = "V8"; NET "Lw[7]" LOC = "T5"; NET "Bn[0]" LOC = "C4"; NET "Bn[1]" LOC = "D9"; NET "Bn[2]" LOC = "A8"; NET "Bn[3]" LOC = "C9"; NET "Lk[0]" LOC = "U16"; NET "Lk[1]" LOC = "V16"; NET "Lk[2]" LOC = "U15"; NET "Lk[3]" LOC = "V15"; NET "Lk[4]" LOC = "M11"; NET "Lk[5]" LOC = "N11"; NET "Lk[6]" LOC = "R11"; NET "Lk[7]" LOC = "T11"; NET "Ag[0]" LOC = "N16"; NET "Ag[1]" LOC = "N15"; NET "Ag[2]" LOC = "P18"; NET "Ag[3]" LOC = "P17";

5.实验电路图:

Part2: 1.问题描述: Create a shift register that updates at different frequencies, all less than about 50Hz (so you can see the LEDs blinking) according to the logic values present on SW0, SW1, and SW2. Since the Nexys3 board main clock is 100MHz, this design will require a clock divider to create lower frequencies. A clock divider is one of the more common applications for counters. In this application, a higher frequency clock drives a counter’s clock input, and the counter outputs provide lower frequency signals at 1/2n of the input frequency, where n is the counter output bit number (assuming bit #0 is the LSB). Thus, the LSB of the counter provides a frequency of ½ the input frequency, bit #1 provides 1/4th the input frequency, bit #2 1/8th the frequency, and so on. In most technologies, the output of one flip-flop (such as a counter output bit) can directly drive the clock inputs of other flip-flops. This design will use eight different clock sources, all derived from the same counter-divider. The count range of a 26-bit counter is 0 to 2^26, or about 64 million. The main input clock is 100MHz, so a 26-bit counter running from the main clock will produce a most-significant bit with a frequency of 50/33, or about 1.5Hz. Less significant bits will produce clocks that are ½ of the more significant bit frequencies (so for example, counter bit 25 will be about 3Hz, and bit 24 about 6Hz). One of these eight different clock sources can be selected to drive the clock input to the shift register. The figure below shows an 8:1 mux, with the output directly driving the sift registers clock input. This is a poor design practice, and should not be implemented (in fact, the Xilinx tools will issue a warning). A clock signal to a flip-flop should never come from a combinational logic circuit, because glitches are possible, and because the internal resources of the FPGA are not designed for this use (clocks should only come from clock buffers, or directly from other flip-flops). Rather than the design shown below, a flip-flop should be inserted between the mux and shift register.