实验四 流水线及流水线中的冲突

流水线的相关问题

流水线只有连续不断地流动,不出现断流,才能获得高效率。

如果处理不当,使流水线产生“断流”,就会使流水效率显著下降。

流水过程中因为相关问题而产生冲突,是导致流水线断流的主要原因。

一般来讲,流水线的相关主要分为以下三种类型。

1. 结构相关结构相关是指当指令在重叠执行过程中,硬件资源满足不了指令重叠执行的要求,两条或两条以上指令争用同一资源而引起的冲突,因此,结构相关又称为资源相关。

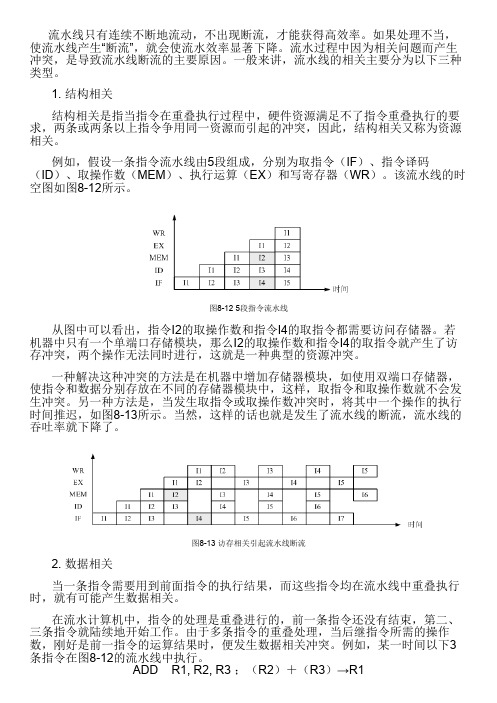

例如,假设一条指令流水线由5段组成,分别为取指令(IF)、指令译码(ID)、取操作数(MEM)、执行运算(EX)和写寄存器(WR)。

该流水线的时空图如图8-12所示。

图8-12 5段指令流水线从图中可以看出,指令I2的取操作数和指令I4的取指令都需要访问存储器。

若机器中只有一个单端口存储模块,那么I2的取操作数和指令I4的取指令就产生了访存冲突,两个操作无法同时进行,这就是一种典型的资源冲突。

一种解决这种冲突的方法是在机器中增加存储器模块,如使用双端口存储器,使指令和数据分别存放在不同的存储器模块中,这样,取指令和取操作数就不会发生冲突。

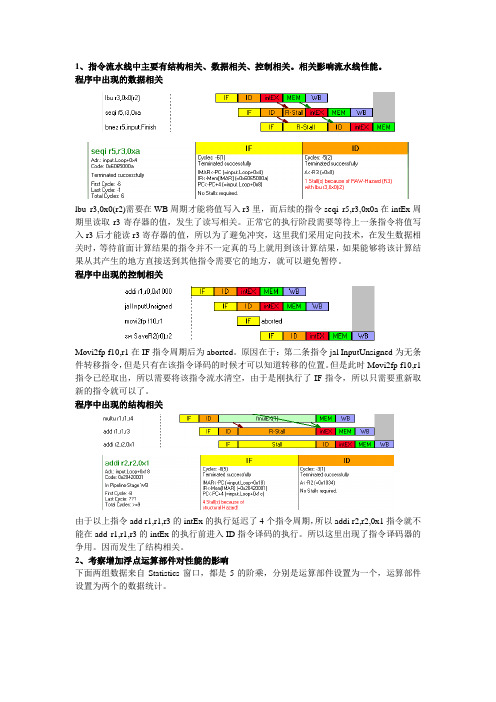

另一种方法是,当发生取指令或取操作数冲突时,将其中一个操作的执行时间推迟,如图8-13所示。

当然,这样的话也就是发生了流水线的断流,流水线的吞吐率就下降了。

图8-13 访存相关引起流水线断流2. 数据相关当一条指令需要用到前面指令的执行结果,而这些指令均在流水线中重叠执行时,就有可能产生数据相关。

在流水计算机中,指令的处理是重叠进行的,前一条指令还没有结束,第二、三条指令就陆续地开始工作。

由于多条指令的重叠处理,当后继指令所需的操作数,刚好是前一指令的运算结果时,便发生数据相关冲突。

例如,某一时间以下3条指令在图8-12的流水线中执行。

ADD R1, R2, R3 ;(R2)+(R3)→R1SUB R4, R1, R5 ;(R1)-(R5)→R4AND R6, R1, R7 ;(R1)∧(R7)→R6其中,SUB指令的EX段需要执行R1减R5,而同一时间,其上一条指令正在执行写结果到R1的操作。

流水线设计

流水线设计1. 概述在计算机科学中,流水线是一种用于提高计算机性能的技术。

它将复杂的任务划分为一系列简单的子任务,并且在同时执行这些子任务的同时传递数据,从而实现更高的吞吐量和更短的响应时间。

本文将介绍流水线设计的基本原理和常见的应用。

我们将讨论流水线的架构、流水线的设计要点以及流水线中可能遇到的一些问题和解决方案。

2. 流水线的架构流水线的基本架构由以下几个组成部分组成:2.1. 输入单元输入单元负责接收外部输入并将其转换为计算机可以处理的格式。

它可以是键盘、鼠标、传感器等。

输入单元还可以包括解码器、缓冲区等组件,以提高数据传输的效率和稳定性。

2.2. 控制单元控制单元负责协调整个流水线中的各个组件的操作。

它根据指令和状态信息来决定下一步的操作,并将相应的指令发送给执行单元。

2.3. 执行单元执行单元是流水线中最重要的部分之一。

它负责执行任务的实际计算部分。

执行单元可以包括算术逻辑单元(ALU)、浮点运算单元(FPU)、乘法器、除法器等。

执行单元可以根据具体的需求进行扩展和优化。

2.4. 存储单元存储单元用于存储流水线中的数据和指令。

它可以是寄存器、缓存、内存等。

存储单元要具备高速访问和大容量的特性,以满足流水线的高效率要求。

2.5. 输出单元输出单元将计算结果输出给外部设备或其他计算机系统。

它可以是显示器、打印机、网络接口等。

输出单元还可以包括编码器、缓冲区等组件,以提高数据传输的效率和稳定性。

3. 流水线的设计要点在设计流水线时,我们需要考虑以下几个要点:3.1. 指令级并行流水线可以将任务划分为一系列子任务,并且在同时执行这些子任务的同时传递数据。

这种指令级并行可以提高计算机的性能。

在设计流水线时,我们需要合理划分子任务,并确保它们之间的依赖关系正确处理。

3.2. 数据冲突在流水线中,由于子任务之间的数据传递,可能会出现数据冲突的情况。

数据冲突会导致流水线的停顿和性能损失。

为了解决数据冲突,我们需要采取一些技术手段,如使用缓存、乱序执行、数据旁路等。

计算机体系结构——流水线技术(Pipelining)

单功能流水线:流水线只完成一种固定功能 多功能流水线:流水线可以完成多种功能,如 TI公司的ASC机,8段流水线,能够实现:定点加减 法、定点乘法、浮点加法等功能 3.按同一时间内各段之间的连接方式分 静态多功能流水线 :同一时间内,多功能结构只能按一种功能的连接方式工作。 动态多功能流水线:在同一时间内,可以有多种功能的连接方式同时工作 4.按处理的数据类型 标量流水线 向量流水线 5.按控制方式 同步流水线 异步流水线:当Si功能段要向Si+1段传送数据时,首 先发出就绪信号,Si+1功能段收到信号后,向Si回送 一个回答信号。 6.按任务从输出端的流出顺序 顺序流水方式:指令流出顺序 = 指令流入顺序 乱序流水方式:指令流出顺序 != 指令流入顺序 7. 线性流水线——不带反馈回路的流水线

三、流水线的分类(了解)

四、流水线相关及冲突(重点) 1.流水线相关 2.流水线冲突 3.流水线冲突带来问题 4.数据冲突及其解决方案 5.结构冲突及其解决方案 6.控制冲突及其解决方案

五、流水线性能分析(含例题讲解) 1.流水线的基本参数——吞吐率 2.流水线的基本参数——加速比 3.流水线的基本参数——效率 4.结果分析 5.有关流水线性能的若干问题

整体评估、反馈、再改进

3. 指令周期

单周期处理机模型:一个周期完成一个指令(每个周期是等长的),指令长度可能不一样,会造成很大的浪费 多周期处理机模型:将一个指令的完成划分成若干个周期来实现 流水线模型

二、流水线技术 1. 什么是流水线? 计算机中的流水线是把一个重复的过程分解为若干个子过程,每个子过程与其他子过程并行进行。由于这种工作方式与工厂中的生产 流水线十分相似, 因此称为流水线技术 从本质上讲,流水线技术是一种时间并行技术。

流水线相关性分析

1、指令流水线中主要有结构相关、数据相关、控制相关。

相关影响流水线性能。

程序中出现的数据相关lbu r3,0x0(r2)需要在WB周期才能将值写入r3里,而后续的指令seqi r5,r3,0x0a在intEx周期里读取r3寄存器的值,发生了读写相关。

正常它的执行阶段需要等待上一条指令将值写入r3后才能读r3寄存器的值,所以为了避免冲突,这里我们采用定向技术,在发生数据相关时,等待前面计算结果的指令并不一定真的马上就用到该计算结果,如果能够将该计算结果从其产生的地方直接送到其他指令需要它的地方,就可以避免暂停。

程序中出现的控制相关Movi2fp f10,r1在IF指令周期后为aborted。

原因在于:第二条指令jal InputUnsigned为无条件转移指令,但是只有在该指令译码的时候才可以知道转移的位置。

但是此时Movi2fp f10,r1指令已经取出,所以需要将该指令流水清空,由于是刚执行了IF指令,所以只需要重新取新的指令就可以了。

程序中出现的结构相关由于以上指令add r1,r1,r3的intEx的执行延迟了4个指令周期,所以addi r2,r2,0x1指令就不能在add r1,r1,r3的intEx的执行前进入ID指令译码的执行。

所以这里出现了指令译码器的争用。

因而发生了结构相关。

2、考察增加浮点运算部件对性能的影响下面两组数据来自Statistics窗口,都是5的阶乘,分别是运算部件设置为一个,运算部件设置为两个的数据统计。

通过比较可以发现,这两组数据在性能统计上是一样的。

所以增加浮点运算部件对性能的影响没有什么影响(对于该程序而言)。

3、考察增加forward部件对性能的影响左右分别是采用forwarding和没有采用forwarding部件的统计效果。

性能比较必须是计算同一个值的时候。

通过比较发现,采用forwarding 技术,总的周期数为95次,暂停了31次。

而没有采用forwarding 技术则总的周期数为112次,暂停了49次。

计算机组成原理流水线设计基础知识全面解析

计算机组成原理流水线设计基础知识全面解析计算机组成原理是计算机科学与技术的基础课程之一,而流水线设计则是其中的重要内容之一。

本文将全面解析计算机组成原理流水线设计的基础知识,介绍其工作原理、优势、流水线冲突及解决方法等内容。

一、工作原理计算机组成原理中,流水线设计是通过将指令的执行过程划分为多个阶段,并将这些阶段在不同的处理单元上并行执行的方式,从而提高指令的执行效率。

流水线设计主要包含以下几个阶段:1. 取指令阶段(IF):从内存中读取指令并将其送至指令译码器。

2. 指令译码阶段(ID):对指令进行解码,判断其类型,并提取相关寄存器的值。

3. 执行阶段(EX):根据指令的类型,对操作数进行计算,并将结果保存至寄存器中。

4. 访存阶段(MEM):如果指令需要访问内存,则进行内存读取或写入操作。

5. 写回阶段(WB):将计算结果写回到寄存器中。

通过将指令的执行划分为多个阶段,并使用多个处理单元并行执行,流水线设计可以大大提高指令的执行效率,加快程序的运行速度。

二、优势流水线设计具有以下几个优势:1. 并行处理:通过将指令的执行划分为多个阶段,并使用多个处理单元并行执行,可以加快指令的执行速度。

2. 提高资源利用率:由于每个处理单元都可以执行不同的指令阶段,因此可以充分利用硬件资源,提高整体的资源利用率。

3. 灵活性:不同的指令可以使用不同的处理单元进行执行,在保持高效率的同时,增加了系统的灵活性,可以执行更多的指令类型。

然而,除了以上的优势外,流水线设计也存在一些问题,即流水线冲突。

三、流水线冲突及解决方法1. 结构冲突:当多个指令需要使用同一硬件资源时,会发生结构冲突。

例如,同时对存储器进行读取和写入操作。

解决方法:通过增加硬件资源的数量或调整指令的执行顺序,可以避免结构冲突的发生。

2. 数据冲突:当后续指令需要使用前一条指令的运算结果时,会发生数据冲突。

例如,一条指令的结果被另一条指令使用。

解决方法:可以通过插入空闲周期或使用旁路机制,将结果传递给后续指令,从而解决数据冲突。

3.3 流水线相关冲突及解决办法_v3.0介绍

计算机体系结构

3.4 流水线的相关

例如:考虑下述代码: DIV.D F2,F6,F4 ADD.D F6,F0,F12 SUB.D F8,F6,F14 DIV.D和ADD.D存在反相关。 进行寄存器换名(F6换成S)后,变成: DIV.D F2,F6,F4 ADD.D S,F0,F12 SUB.D F8,S,F14

2.

北京信息科技大学

计算机体系结构

3.4 流水线的相关

指令j与指令i之间的名相关有两种:

反相关:如果指令j写的名与指令i读的名相同,则 称指令i和j发生了反相关。

指令j写的名=指令i读的名

输出相关:如果指令j和指令i写相同的名,则称指 令i和j发生了输出相关。

指令j写的名=指令i写的名

北京信息科技大学

计算机体系结构

3.4 流水线的相关

数据相关 对于两条指令i(在前,下同)和j(在后,下同),如 果下述条件之一成立,则称指令j与指令i数据相关。 指令j使用指令i产生的结果; 指令j与指令k数据相关,而指令k又与指令i数据相关。 数据相关具有传递性。 数据相关反映了数据的流动关系,即如何从其产生者流 动到其消费者。

北京信息科技大学

计算机体系结构

3.4 流水线的冲突

由于访问同一个存储器而引起的结构冲突 北京信息科技大学

计算机体系结构

3.4 流水线的冲突

为消除结构冲突而插入的流水线气泡 北京信息科技大学

计算机体系结构

3.4 流水线的冲突

引入暂停后的时空图 指令编号 1 指令i 指令i+1 指令i+2 指令i+3 指令i+4 指令i+5 IF 2 ID IF 3 EX ID IF 4 MEM EX ID stall 时钟周期 5 WB MEM EX IF WB MEM ID IF WB EX ID IF WB MEM EX ID WB MEM EX WB MEM 6 7 8 9 10

计算机体系结构流水线冲突与乱序执行的解决方法

计算机体系结构流水线冲突与乱序执行的解决方法在计算机体系结构中,流水线是一种有效提高指令处理速度的技术。

然而,流水线执行过程中可能会出现冲突和乱序执行的问题。

本文将探讨流水线冲突的原因以及相应的解决方法。

一、流水线冲突的原因在流水线中,冲突主要由以下几个因素引起:1. 结构冲突:当多个指令需要同时访问同一个计算资源,比如存储器或者寄存器时,产生结构冲突。

这会导致流水线阻塞,降低执行效率。

2. 数据冲突:数据相关性是指指令间存在的数据依赖关系。

当某个指令需要等待上一条指令的执行结果时,就会发生数据冲突。

数据冲突分为读后写、写后读和写后写三种类型。

3. 控制冲突:当分支指令的判断结果还未确定时,指令执行流程可能发生改变。

这会导致原本在流水线中已经执行的指令无效,需要清空掉重新执行,造成控制冲突。

二、解决结构冲突的方法针对结构冲突,可以采取以下几种解决方法:1. 资源冲突解决:通过增加计算资源的数量来解决结构冲突。

比如增加缓存的容量、加大寄存器的数量等。

这样可以减少多个指令竞争同一资源的情况。

2. 指令重排解决:在源代码级别上进行指令重排,通过调整指令的顺序来避免结构冲突。

这一般需要编译器的支持,通过静态分析源代码并进行优化。

三、解决数据冲突的方法对于数据冲突,有以下几种解决方法:1. 数据旁路解决:当一个指令需要等待上一条指令的执行结果时,可以通过数据旁路的方式将上一条指令的结果直接传递给下一条指令,避免流水线的停顿。

2. 数据预测解决:对于分支指令引起的数据冲突,可以采用数据预测的方法来预测分支的结果。

如果预测正确,可以顺利执行;如果预测错误,则需要清空流水线并重新执行。

四、解决控制冲突的方法针对控制冲突,可以采取以下几种解决方法:1. 预测解决:通过对分支指令进行预测,尽可能准确地预测分支结果,从而减少控制冲突。

常用的预测方法有静态预测和动态预测。

2. 延迟解决:在流水线中引入延迟槽,即在分支指令后面放置几条无关紧要的指令,以填充流水线的空闲时间。

流水线的工作原理

流水线的工作原理

流水线的工作原理是将一个任务拆分成多个子任务,并由多个处理单元按照顺序进行并行处理,从而实现提高任务处理效率的目的。

具体来说,流水线工作原理分为以下几个步骤:

1. 任务拆分:将一个任务分解成多个子任务,每个子任务具有一定的独立性,可以并行处理。

2. 指令执行阶段划分:将每个子任务划分为不同的阶段,每个阶段需要不同类型的处理单元进行处理。

3. 并行处理:每个处理单元在每个阶段对应的子任务上进行处理,各个处理单元同时工作,形成并行处理的效果。

4. 流水线寄存器:流水线中的每个阶段之间通过流水线寄存器进行数据传输,保证各个阶段之间的数据同步。

5. 流水线冲突处理:由于流水线中各个阶段同时进行,可能会出现数据相关等冲突,需要通过添加硬件逻辑或进行优化来解决这些冲突,以保证流水线的正常工作。

6. 结果合并:当所有子任务完成处理后,将各个处理单元输出的结果合并得到最终的任务结果。

通过以上步骤,流水线能够将一个任务分解并并行处理,充分利用硬件资源,提高任务处理的效率和速度。

但是流水线也会因为流水线寄存器的引入,导致任务执行速度下降,同时需要处理冲突问题,因此需要根据具体情况进行流水线设计和优化。

第5章标量处理机(5.4,5.5,5.6)流水线的冲突MIPS流水线素材

ALU

ALU

DSUB R4,R1,R5

IM

Reg

DM

Reg

ALU

XOR R6,R1,R7

计算机科学与技术系 yangruioot@

对于在一个时钟周期内同一寄存器堆进行操作,在时钟的前半部 分进行写寄存器的操作,后半部分进行读寄存器的操作。

计算机科学与技术系 yangruioot@

如何解决对同一寄存器的访问冲突?

把写操作安排在时钟周期的前半拍完成,

每一个周期作为一个流水段;

在各段之间加上锁存器(流水寄存器)。

IF 段 IM

ID 段 Reg

EX 段

MEM 段 DM

WB 段 Reg

流水寄存器

计算机科学与技术系 yangruioot@

ALU

流水寄存器保证了流水线中不同段的指令不会相互影 响。每个时钟周期结束之后,该段的所有执行结果都 保存在流水段寄存器中,在下一个时钟周期开始作为 下一个段的输入。

采用定向技术消除上例中的相关 DSUB操作是在DADD操作产生了结果之后才使

用该结果的,考虑将DADD的结果从EX/MEM寄 存器移到DSUB需要的地方,也就是ALU的输入 锁存器,则不需要引入停顿。

计算机科学与技术系

yangruioot@

时间(时钟周期) 1 DADD R1,R2,R3 IM 2 Reg 3 4 DM 5 Reg 6

计算机科学与技术系

yangruioot@

时间(时钟周期) 1 load M 2 Reg 3 4 M 5 Reg 6 7 8

ALU

ALU

指令 i+1

M

Reg

M

Reg

ALU

指令 i+2

高性能计算中的流水线技术分析(一)

高性能计算中的流水线技术分析随着科技的发展和数据量的不断增长,高性能计算成为当代信息技术领域的重要组成部分。

在高性能计算中,流水线技术起到了至关重要的作用。

本文将从流水线的定义、原理、优势和应用等方面进行深入分析。

一、流水线的定义和原理流水线技术是一种将一个复杂的任务分为多个子任务,通过多个阶段分别处理的技术。

它的运行原理是将输入的任务划分成若干个阶段,每个阶段处理一个任务,并通过将每个任务传递给下一个阶段,实现任务的并行处理。

流水线技术可以提高系统的整体性能和处理效率。

二、流水线技术的优势1. 提高处理效率:流水线技术能够将复杂任务分解成多个简单任务,在每个阶段都能并行处理多个任务,从而提高整体的处理效率。

2. 实现指令重叠:在流水线中,每个阶段都可以同时处理不同的任务,从而实现指令的重叠执行,提高了系统的吞吐量。

3. 减少资源闲置:由于流水线技术可以同时处理多个任务,并且每个阶段都可以开始下一个任务,所以能够减少资源的闲置时间,提高系统的利用率。

三、流水线技术的应用1. CPU设计中的流水线技术:在计算机的CPU设计中,流水线技术广泛应用。

将计算机指令划分为取指令、译码、执行、写回等阶段,并在每个阶段同时处理指令,提高了CPU的计算性能。

2. 图像处理中的流水线技术:在图像处理领域,流水线技术可以将图像处理任务划分为多个阶段,如图像读取、图像滤波、图像增强等,并通过并行处理,快速完成大规模的图像处理任务。

3. 云计算系统中的流水线技术:在云计算系统中,流水线技术可以将用户请求的处理过程划分为多个阶段,如请求接收、请求解析、资源分配等,并将每个阶段分别处理,提高了系统的响应速度和处理能力。

四、流水线技术的挑战和解决方案1. 数据依赖:在流水线中,不同任务之间可能存在依赖关系,导致任务的执行顺序发生变化,从而影响并行处理效果。

解决方案是通过增加冲突检测和处理的机制,在保证数据一致性的前提下实现最大程度的并行处理。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验4 流水线及流水线中的冲突

一.实验目的

(1)理解计算机流水线基本概念。

(2)理解MIPS结构如何用5段流水线来实现。

(3)理解各段的功能和基本操作。

(4)加深对数据冲突、结构冲突的理解,理解这两类冲突对CPU性能的影响。

(5)进一步理解解决数据冲突的方法,掌握如何应用定向技术来减少数据冲突引起的停顿。

二.实验内容和步骤

(1)启动MIPSsim:

(2)、根据预备知识中关于流水线各段操作的描述,进一步理解流水线窗口中各段的功能,掌握各流水寄存器的含义。

(用鼠标双击各段,就可以看到各流水寄存器的内容)

流水线窗口如下所示:

取指令(IF)、指令译码/读寄存器(ID)、执行/访存有效地址计算(EX)、存储器访问(MEM)、结果写回寄存器(WB)

流水寄存器窗口:

IF:

ID:

EX:

MEM:

WB流水线段为空

(3)、参照MIPSsim模拟器使用说明,熟悉MIPSsim模拟器的操作和使用方法。

(4)、选择配置菜单中的“流水方式”选项,使模拟器工作于流水方式下。

(5)、观察程序在流水线中的执行情况,步骤如下:

1)选择MIPSsim的“文件”—>“载入程序”选项来加载pipeline.s。

2)关闭定向功能。

这是通过“配置”—>“定向”。

3)用单步执行一个周期的方式执行该程序,观察每一个周期中,各段流水寄存器内容的变化、指令的执行情况(“代码”窗口)以及时钟周期图。

执行周期总数为1时:

执行周期总数为2时:

执行周期总数为3时:

执行周期总数为4时:

执行周期总数为5时:

执行周期总数为6时:

执行周期总数为7时:

执行周期总数为8时:

执行周期总数为9时:

执行周期总数为10时:

执行周期总数为11时:

执行周期总数为12时:

执行周期总数为13时:

4)当执行到第13个时钟周期时,各段分别正在处理的指令是: IF: LW $r4,60($r6)

ID: ADDI $r3,$r0,25

EX: ADDI $r1,$r1,-1

MEM: ADDI $r6,$r0,8

WB: ADD $r2,$r1,$r0

画出这时的时钟周期图。

(6)、这时各流水寄存器中的内容为:

IF/ID.IR: 2361655356

IF/ID.NPC: 48

ID/EX.A: 0

ID/EX.B: 0

ID/EX.IR: 537067545

ID/EX.Imm: 25

EX/MEM.ALUo: 4

EX/MEM.IR: 539099135

MEM/WB.LMD: 0

MEM/WB.ALUo: 8

MEM/WB.IR: 537264136

(7)、观察和分析结构冲突对CPU性能的影响,步骤如下:

1)加载structure_hz.s

2)执行该程序,找出存在结构冲突的指令对以及导致结构冲突的部件。

答:结构冲突的指令:ADD.D$f2,$f0,$f1和ADD.D$f3,$f0,$f1

结构冲突部件:加法寄存器

3)记录由结构冲突引起的停顿时钟周期数,计算停顿时钟周期数占总执行周期数

的百分比。

答:结构冲突引起的停顿时钟周期数:9

停顿时钟周期数占总执行周期数的百分比:69.23077%

4)把浮点加法器的个数改为4个。

5)再次重复步骤1)-步骤3)的工作。

1)加载structure_hz.s。

2)执行该程序,找出存在结构冲突的指令对以及导致结构冲突的部件。

答:结构冲突的指令:ADD.D$f4,$f0,$f1和ADD.D$f5,$f0,$f1, 结构冲突部件:加法寄存器

3)记录由结构冲突引起的停顿时钟周期数,计算停顿时钟周期数占总执行周期数的百分比。

答:

结构冲突引起的停顿时钟周期数:1

停顿时钟周期数占总执行周期数的百分比:14.28571%

6)分析结构冲突对CPU性能的影响,讨论解决结构冲突的方法。

答:对CPU性能的影响:当发生冲突时,流水线会发生停顿,从而降低了CPU 的性能。

解决方法:在流水线处理机中设置相互独立的指令存储器和储存器(8)、观察数据冲突并用定向技术来减少停顿,步骤如下:

1)全部复位。

(所有的都回到最初状态)

2)加载data_hz.s。

3)关闭定向功能

4)单步执行一个周期,同时查看时钟周期图,列出在什么时刻发生了RAW (先写后读)冲突。

4、5、6、8、9、10、12、13、16、17、19、20、24、25、26、27、28、31、32、35、、36、38、39周期发生了RAW冲突

5)记录数据冲突引起的停顿时钟周期数及程序执行的总时钟周期数,计算停顿时钟周期数占总执行周期数的百分比。

数据冲突引起的停顿时钟周期数:23

程序执行的总时钟周期数:43

停顿时钟周期数占总执行周期数的百分比:53.48837%

6)复位CPU

7)打开定向功能。

8)单步执行一个周期,同时查看时钟周期图,列出在什么时刻发生了RAW (先写后读)冲突,并与步骤(3)的结果进行比较。

答:第4、6、8、9、10、12、13、18、20、22、24、25、30、32、34、36、37周期发生了RAW冲突

9)记录由数据冲突引起的停顿时钟周期数以及程序执行的总时钟周期数,计算采用定向技术后的性能是原来的几倍。

答:数据冲突引起的停顿时钟周期数:13

程序执行的总时钟周期数:43

停顿时钟周期数占总执行周期数的百分比:30.23256%

采用定向技术后的性能是原来的1.77倍

三.实验结果分析

当发生结构冲突时,流水线会出现停顿,从而降低了CPU的性能。

要避免结构冲突就要在流水线处理机中设置相互独立的指令存储器和数据存储器。

当发生数据冲突时,程序执行并定向时的总停顿周期比没有定向功能的时候少,说明要降低数据冲突的方法是对CPU复位并定向。

四.实验心得

通过本次实验,我对流水线的工作原理、流水线的冲突以及解决方法

都有了更深入的了解,对5段流水线的的理解和掌握更深刻了,通过观察时钟周期图能够辨别冲突类型及冲突原因,对结构冲突和数据冲突有了更好的认识。