为什么高速PCB设计绕等长一定要绕个山路十八弯

做内层PCB不仅要会绕等长,你还应该了解哪些?

做内层PCB不仅要会绕等长,你还应该了解哪些?经常画高速板的同学都知道,10个高速板有9个要绕等长,而且内存出现的频率尤其频繁,整的现在画板子不绕两下都有点不习惯。

好在上期给大家介绍了几种快的不能再快的绕等长的方法,用allegro绕等长还是非常任性的。

看看下图,多么漂亮,整齐,干净,密密麻麻绕的像一根根肠子似的等长线。

内存在高速板中的频繁出现,意味着PCB工程师必须掌握内存的PCB设计,而且还得熟练的掌握,要会对各种信号进行分组,要会选用拓扑结构,要会布局,要会设等长规则......当然还得会绕等长。

根据小编多年跳槽面试的经验,内存的设计要求也是经常会被问到的问题之一,10个面试官有9个会问,而你对答的好坏或者回答问题的深度直接影响到面试官对你的整体印象。

以DDR3为例,一般的同学可能会从这些方面去回答:布局:1.考虑BGA可维修性:BGA周边器件5MM禁布,最小3mm;2.DFM 可靠性:按照相关的工艺要求,布局时器件与器件间满足DFM的间距要求;且考虑元件摆放的美观性;3.绝对等长是否满足要求,相对长度是否容易实现:布局时需要确认长度限制,及时序要求,留有足够的绕等长空间;4.滤波电容、上拉电阻的位置等:滤波电容靠近各个PIN放置,储能电容均匀放置在芯片周边(在电源平面路径上);上拉电阻按要求放置(布线长度小于500mil)。

布线:1.特征阻抗:单线50欧姆,差分100欧姆;2.数据线每11根(D0~D7,DM0,DQS0+/-),(D8~D15, DM1,DQS1+/-)....以此类推.同组同层,优先以地为参考平面,中间不能夹杂其他任何信号;3.所有信号线少换层,尤其是数据线、时钟线不超过2个过孔,所有信号线间距至少满足3W原则;。

详解PCB走线与信号完整性问题

详解PCB走线与信号完整性问题高速信号的PCB走线现在但凡打开SoC原厂的PCB Layout Guide,都会提及到高速信号的走线的拐角角度问题,都会说高速信号不要以直角走线,要以45度角走线,并且会说走圆弧会比45度拐角更好。

事实是不是这样?PCB走线角度该怎样设置,是走45度好还是走圆弧好?90度直角走线到底行不行?大家开始纠结于PCB走线的拐角角度,也就是近十几二十年的事情。

上世纪九十年代初,PC界的霸主Intel主导定制了PCI总线技术。

似乎从PCI接口开始,我们开始进入了一个“高速”系统设计的时代。

电子设计和芯片制造技术按照摩尔定律往前发展,由于IC制程的工艺不断提高,IC的晶体管开关速度也越来越快,各种总线的时钟频率也越来越快,信号完整性问题也在不断的引起大家的研究和重视。

早期PCB拉线菌应该还是比较单纯,把线路拉通、撸顺,整洁、美观即可,不用去关注各种信号完整性问题。

比如下图所示的HP经典的HP3456A万用表的电路板,大量的90°角走线,几乎是故意走的直角,绝大多数地方没有铺铜。

上面PCB板的右上角,不仅走直角不止,拐弯后,线宽还变小了,会造成信号反射问题,影响信号完整性。

本文跟大家探讨一下关于高频/高速信号的走线拐角角度问题。

我们从锐角到直角、钝角、圆弧一直到任意角度走线,看看各种走线拐角角度的优缺点。

为什么PCB不能以锐角走线?PCB能不能以锐角走线,答案是否定的。

先不管以锐角走线会不会对高速信号传输线造成负面影响,单从PCB DFM方面,就应该避免出现锐角走线的情形。

因为在PCB导线相交形成锐角处,会造成一种叫酸角“acid traps”的问题。

在PCB制板过程中,在PCB线路蚀刻环节,在“acid traps”处会造成PCB线路腐蚀过度,带来PCB线路虚断的问题。

虽然,我们可以借助CAM 350 进行DFF Audit自动检测出“acid traps”潜在问题,避免在PCB在制造产生时产生加工瓶颈。

高速pcb设计规则

高速pcb设计规则

高速PCB设计规则是指在设计PCB时需要遵循的一系列规则和原则,以确保信号传输的质量和稳定性。

高速 PCB 的设计需要考虑多

种因素,如信号传输速度、信号波形、传输距离、干扰等等。

以下是一些常见的高速 PCB 设计规则:

1. 避免信号线的走线路径过长,尽可能缩短信号线的长度,以

减小信号传输延迟和损耗。

2. 保证信号线之间的距离足够大,以避免互相干扰,同时也能

降低信号串扰的风险。

3. 使用合适的层次结构设计,尽可能将信号线和电源线分离,

以减少干扰和噪声。

4. 在 PCB 的布线中,保证地线和供电线的宽度足够宽,以确保稳定的供电和地面连接。

5. 在 PCB 的布线中,避免过多的弯曲或拐角,以减小信号传输中的损失和延迟。

6. 选用合适的 PCB 材料和厚度,以满足高速信号传输的需求。

7. 注意 PCB 的电磁兼容性,通过合理的布线和屏蔽来减少干扰。

以上是高速 PCB 设计中的一些基本规则,但实际上,高速 PCB 的设计涉及的方面非常广泛,需要根据具体的应用场景来进行设计。

为了保证高速 PCB 的质量和可靠性,需要有专业的技术人员进行设

计和测试。

- 1 -。

九条高速PCB信号走线规则

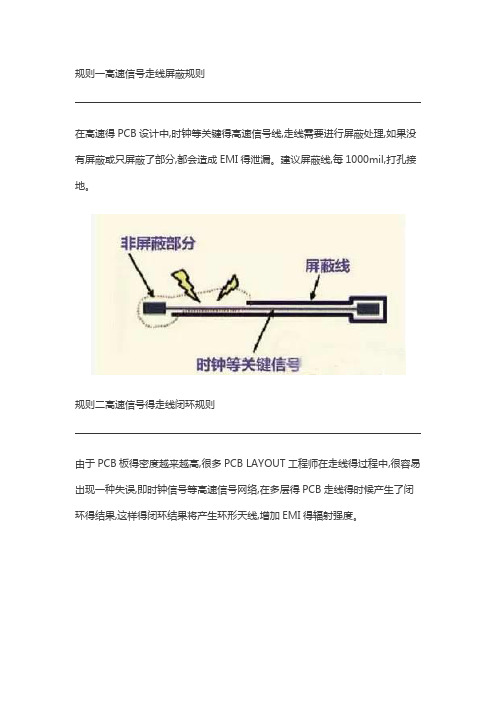

规则一高速信号走线屏蔽规则在高速得PCB设计中,时钟等关键得高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI得泄漏。

建议屏蔽线,每1000mil,打孔接地。

规则二高速信号得走线闭环规则由于PCB板得密度越来越高,很多PCB LAYOUT工程师在走线得过程中,很容易出现一种失误,即时钟信号等高速信号网络,在多层得PCB走线得时候产生了闭环得结果,这样得闭环结果将产生环形天线,增加EMI得辐射强度。

规则三高速信号得走线开环规则规则二提到高速信号得闭环会造成EMI辐射,然而开环同样会造成EMI辐射。

时钟信号等高速信号网络,在多层得PCB走线得时候一旦产生了开环得结果,将产生线形天线,增加EMI得辐射强度。

规则四高速信号得特性阻抗连续规则高速信号,在层与层之间切换得时候必须保证特性阻抗得连续,否则会增加EMI得辐射。

也就就是说,同层得布线得宽度必须连续,不同层得走线阻抗必须连续。

规则五高速PCB设计得布线方向规则相邻两层间得走线必须遵循垂直走线得原则,否则会造成线间得串扰,增加EMI辐射。

简而言之,相邻得布线层遵循横平竖垂得布线方向,垂直得布线可以抑制线间得串扰。

规则六高速PCB设计中得拓扑结构规则在高速PCB设计中,线路板特性阻抗得控制与多负载情况下得拓扑结构得设计,直接决定着产品得成功还就是失败。

图示为菊花链式拓扑结构,一般用于几Mhz 得情况下为益。

高速PCB设计中建议使用后端得星形对称结构。

规则七走线长度得谐振规则检查信号线得长度与信号得频率就是否构成谐振,即当布线长度为信号波长1/4得时候得整数倍时,此布线将产生谐振,而谐振就会辐射电磁波,产生干扰。

规则八回流路径规则所有得高速信号必须有良好得回流路径。

尽可能地保证时钟等高速信号得回流路径最小。

否则会极大得增加辐射,并且辐射得大小与信号路径与回流路径所包围得面积成正比。

规则九器件得退耦电容摆放规则退耦电容得摆放得位置非常得重要。

Altium Designer关于绕等长的方式跟技巧(From to)教程

Altium Designer关于绕等长的方式和方法(From to)教程1、为什么要等长,等长的重要性。

在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。

由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDR SDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。

等长走线的目的就是为了尽可能的减少所有相关信号在PCB上的传输延迟的差异。

至于USB/SATA/PCIE等串行信号,并没有上述并行总线的时钟概念,其时钟是隐含在串行数据中的。

数据发送方将时钟包含在数据中发出,数据接收方通过接收到的数据恢复出时钟信号。

这类串行总线没有上述并行总线等长布线的概念。

但因为这些串行信号都采用差分信号,为了保证差分信号的信号质量,对差分信号对的布线一般会要求等长且按总线规范的要求进行阻抗匹配的控制。

2、绕等长的命令和技巧方法一:第一步:连接好需要绕等长的线,。

第二步:T+R开始绕等长,TAB键调出等长属性设置框,如下图:志博教育--专业高速PCB设计与培训 官网:www.zbpcb.com第三步:滑动走蛇形线即可;其中“<”和“>”可以分别调整蛇形线的上下幅度,数字键1减小拐角幅度,数字键2增大拐角幅度、数字键3减小Gap间距、数字键4增大Gap间距:方法二:Shift+A可以直接在走线模式下饶点对点等长。

设置属性和方法一相同。

3、差分对等长快捷键T+I,属性设置可参考单根等长属性设置。

【常用模块的饶等长技巧】1)、远端分支型走线等长要求是L1+L2=L3+L1一般操作的方法是先设置好T点,尽量让L1和L2等长,若T点设置在中间的,一般就是差不多了,若T点设置不在中间可适当对某一分支进行绕线。

方法一:删掉一边分支,(如:L2),之后对L1进行绕线。

[经验之谈]简单讲讲为什么高速PCB需要等长布线

![[经验之谈]简单讲讲为什么高速PCB需要等长布线](https://img.taocdn.com/s3/m/f1fd71e8ba4cf7ec4afe04a1b0717fd5360cb2aa.png)

[经验之谈]简单讲讲为什么高速PCB需要等长布线高速信号有效的建立保持窗口比较小,要让数据和控制信号都落在有效窗口内,数据、时钟或数据之间、控制信号之间的走线长度差异就很小。

具体允许的偏差可以通过计算时延来得到。

其实一般来说,时序逻辑信号要满足建立时间和保持时间并有一定的余量。

只要满足这个条件,信号是可以不严格等长的。

然而,实际情况是,对于高速信号来说(例如DDR2、DDR3、FSB),在设计的时候是无法知道时序是否满足建立时间和保持时间要求(影响因素太多,包括芯片内部走线和容性负载造成的延时差别都要考虑,很难通过计算估算出实际值),必须在芯片内部设置可控延时器件(通过寄存器控制延时),然后扫描寄存器的值来尝试各种延时,并通过观察信号(直接看波形,测量建立保持时间)来确定延时的值使其满足建立时间和保持时间要求。

不过同一类信号一般只对其中一根或几根信号线来做这种观察,为了使所有信号都满足时序要求,只好规定同一类信号走线全部严格等长。

上面说的是高速并行信号。

对于高速的串行信号,如果是带时钟的,时钟和串行数据也必须满足建立保持时间要求,所以也要控制好长度。

有些高速串行信号虽然带时钟,但这个时钟不是用来锁存数据而是一个频率较低的参考时钟,那么数据和时钟以及多个通道之间的数据的skew就可以宽松很多,不用严格等长,因为接收芯片是能够正确找出每个通道的起始位并且把参考时钟经过PLL倍频和相移来锁存数据的。

例如TMDS信号,串行数据的差分对之间要严格等长,但数据之间的skew放宽到+/-20%的时钟周期。

不过为了避免不必要的问题,一般来说像TMDS、PCI-E这些串行信号,通道间一般也要做等长,不过允许的偏差可以比较大,例如200ps以上。

至于低速信号,其建立保持窗口一般在ns级以上,这样就没必要做长度控制了,因为无论布线怎么差也很难搞出ns级的skew。

PCB电路板高速PCB设计指南

PCB电路板高速PCB设计指南高速PCB设计指南之一第一篇PCB布线在PCB设计中,布线是完成产品设计的重要步骤,可以说前面的准备工作都是为它而做的,在整个PCB中,以布线的设计过程限定最高,技巧最细、工作量最大。

PCB布线有单面布线、双面布线及多层布线。

布线的方式也有两种:自动布线及交互式布线,在自动布线之前,可以用交互式预先对要求比较严格的线进行布线,输入端与输出端的边线应避免相邻平行,以免产生反射干扰。

必要时应加地线隔离,两相邻层的布线要互相垂直,平行容易产生寄生耦合。

自动布线的布通率,依赖于良好的布局,布线规则可以预先设定,包括走线的弯曲次数、导通孔的数目、步进的数目等。

一般先进行探索式布经线,快速地把短线连通,然后进行迷宫式布线,先把要布的连线进行全局的布线路径优化,它可以根据需要断开已布的线。

并试着重新再布线,以改进总体效果。

对目前高密度的PCB设计已感觉到贯通孔不太适应了,它浪费了许多宝贵的布线通道,为解决这一矛盾,出现了盲孔和埋孔技术,它不仅完成了导通孔的作用,还省出许多布线通道使布线过程完成得更加方便,更加流畅,更为完善,PCB板的设计过程是一个复杂而又简单的过程,要想很好地掌握它,还需广大电子工程设计人员去自已体会,才能得到其中的真谛。

1电源、地线的处理既使在整个PCB板中的布线完成得都很好,但由于电源、地线的考虑不周到而引起的干扰,会使产品的性能下降,有时甚至影响到产品的成功率。

所以对电、地线的布线要认真对待,把电、地线所产生的噪音干扰降到最低限度,以保证产品的质量。

对每个从事电子产品设计的工程人员来说都明白地线与电源线之间噪音所产生的原因,现只对降低式抑制噪音作以表述:(1)、众所周知的是在电源、地线之间加上去耦电容。

(2)、尽量加宽电源、地线宽度,最好是地线比电源线宽,它们的关系是:地线>电源线>信号线,通常信号线宽为:0.2~0.3mm,最经细宽度可达0.05~0.07mm,电源线为1.2~2.5mm对数字电路的PCB可用宽的地导线组成一个回路,即构成一个地网来使用(模拟电路的地不能这样使用)(3)、用大面积铜层作地线用,在印制板上把没被用上的地方都与地相连接作为地线用。

PCB等长那些事儿

据有关高速PCB布线建议的文章介绍,SDRAM存储器走线时要注意“尽量短且等长”,不知道它说得是仅指数据线呢,还是包括数据线、地址线、控制线?对于数据线,等长比较好走,因为它是点到点的,而对于地址线、控制线,等长就难了,因为它们是一点到多点的,所以还与总线拓扑结构有关,而且PCB走线时空间紧张;请问各位有什么好的建议,尤其是地址线、控制线的拓扑结构,是否需要作等长处理,如果要的话,怎样作等长处理?一.主要还是看SDRAM的频率能跑多高了!尽量做到地址线等长,和数据线等长,我们在计算等长时分别算主芯片到匹配电阻的长度和匹配电阻到SDRAM的长度并且要算过孔数(将过孔大致折算成线长),然后将总长度算出,再做等长匹配.如果有多块SDRAM的话,地址线尽量走T型线,数据线尽量等长,芯片应该都能跑起来的.我做的DVD板,SDRAM基本都不走等长(因为频率基本上是108M,和133M的芯片,呵呵),实在看不过去的线就绕一下,相差不是很悬殊的就没问题,都能跑起来的!我做的好几块板子都正常运作;不过DDR的就不能大意了.要计算后再绕.重在布局,布局合理会省很大的事。

二.数据线在板子上是不需要额外作阻抗匹配的,只有地址线和控制线需要在dimm末端加一termination电阻作终端阻抗匹配,防止反射。

后来又做一个DDR2的板子,地址线等长T形走线(有两片)、数据线等长处理,程序跑得很稳定。

当然,光等长是不行的,在走线时,所有数据线与地址线均使用同一个参考面,电源与端接电源的去耦做好。

只要这么做了,系统就是稳定,什么都不用担心。

另外,告诉大家:一般的SDRAMController都是可以调时序的,所以数据与地址线、时钟线不必等长,软件调好时序就可以(当然这些参数是可以计算的,可不要瞎调哦)三.时钟线与控制线,地址线尽量等长,他们一起实现逻辑控制;数据线自己尽量等长可以了;当然,全部等长最好;[四.控制信号(CS,CKE)、命令信号(WE,CAS,RAS等)和地址信号(Ax,BAx)还有数据信号(EDX)都是由主设备SDRAM控制器发出的,主设备利用内部CLK上升沿把数据和控制信号输出到总线上,在下一个CLK的上升沿把数据或控制信号打入到SDRAM。

PCB特殊走线的三种技巧分享

PCB特殊走线的三种技巧分享在讲解PCB布线完成后的检查工作之前,先为大家介绍三种PCB的特殊走线技巧。

将从直角走线,差分走线,蛇形线三个方面来阐述PCB LAYOUT的走线:一、直角走线(三个方面)直角走线的对信号的影响就是主要体现在三个方面:一是拐角可以等效为传输线上的容性负载,减缓上升时间;二是阻抗不连续会造成信号的反射;三是直角尖端产生的EMI,到10GHz以上的RF设计领域,这些小小的直角都可能成为高速问题的重点对象。

二、差分走线(“等长、等距、参考平面”)何为差分信号(Differential Signal)?通俗地说就是驱动端发送两个等值、反相的信号,接收端通过比较这两个电压的差值来判断逻辑状态“0”还是“1”。

而承载差分信号的那一对走线就称为差分走线。

差分信号和普通的单端信号走线相比,最明显的优势体现在以下三方面:1)抗干扰能力强,因为两根差分走线之间的耦合很好,当外界存在噪声干扰时,几乎是同时被耦合到两条线上,而接收端关心的只是两信号的差值,所以外界的共模噪声可被完全抵消。

2)能有效抑制EMI,同样的道理,由于两根信号的极性相反,他们对外辐射的电磁场可以相互抵消,耦合的越紧密,泄放到外界的电磁能量越少。

3)时序定位精确,由于差分信号的开关变化是位于两个信号的交点,而不像普通单端信号依靠高低两个阈值电压判断,因而受工艺,温度的影响小,能降低时序上的误差,同时也更适合于低幅度信号的电路。

目前流行的LVDS(low voltage differenTIal signaling)就是指这种小振幅差分信号技术。

三、蛇形线(调节延时)蛇形线是Layout中经常使用的一类走线方式。

其主要目的就是为了调节延时,满足系统时序设计要求。

其中最关键的两个参数就是平行耦合长度(Lp)和耦合距离(S),很明显,信号在蛇形走线上传输时,相互平行的线段之间会发生耦合,呈差模形式,S越小,Lp。

allegro 高速pcb设计技巧

allegro 高速pcb设计技巧

在Allegro中进行高速PCB设计时,以下是一些技巧和注意事项:

1. 确保足够的间距:在高速信号线之间保持足够的间距,以减少串扰和信号失真。

2. 避免过长的连线:尽量减少高速信号线的长度,以减少信号传输时间和延迟。

3. 使用合适的线宽:根据信号的频率和电流负载,选择合适的线宽以减小信号的衰减和失真。

4. 考虑使用差分对:对于需要高速传输和高可靠性的信号,可以使用差分对来提高信号质量和抗干扰能力。

5. 避免使用过长的接地线:过长或弯曲的接地线可能会产生额外的电感和电容,影响信号完整性。

6. 考虑使用去耦电容:在关键信号线和电源平面之间添加去耦电容,以减小电源噪声和改善信号完整性。

7. 使用合适的层叠结构:根据设计需求选择合适的层叠结构,包括信号层、电源层和接地层的数量和排列方式。

8. 考虑使用阻抗控制:通过精确控制导线的阻抗,可以减小信号反射和失真。

9. 使用仿真工具进行验证:在布局布线完成后,使用仿真工具进行信号完整性验证,以确保设计满足性能要求。

10. 参考标准和经验:遵循相关的设计标准和经验法则,例如IPC标准、JEDEC标准等,以确保设计的可靠性和一致性。

以上是一些基本的Allegro高速PCB设计技巧,实际设计中可能还需要考虑更多的因素和细节。

建议在设计过程中不断学习和总结经验,以提高设计水平。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

高速PCB设计绕等长一定要绕个山路十八弯太算吊?xfire 高频高速PCB设计围观361次 2 条评论编辑日期:2015-08-16 字体:大中小初次接觸高速訊號或DDR設計的人,可以找到一些在談走線繞等長的舊資料(當中不乏過去大廠的design guide),但近幾年一些DDRII(或更快)的design rule,漸漸改以定義setup time, hold time budget with jitter取代length-matching routing rule,並且改以強調對時序圖的理解與使用模擬(margin predict)的重要性。

簡單說:rule 就是不管你怎麼layout設計,但你時序要滿足規格(timing margin),或傳輸線的損耗要在規格內(S-parameter)。

我們在評估不同group之間的走線等長要求,或同一個group內的走線等長要求,必須就時序的角度來考慮。

一般特性阻抗50 ohm的microstrip於1000mils的傳遞時間大約是150~160ps,假設point-point的DDRII走線總長約1000~1500mils,其中各別線長的差異了不起500mils,此時線長差異對SI影響其實很小,但光是1000~1500mils長的走線於1.6mm板厚的PCB上過孔換層,就會造成100~250ps 不等的傳遞延遲時間差了。

線長差異只是影響時序的因素之一,stack-up\via\stub\coplane\slot…這些因素在高速訊號設計的領域裡,在PCB與package level,彼此是有不同程度的交互影響,如果只是一味的要求蛇線等長,而讓走線的總線長大幅增加,並且蛇線本身引入的阻抗彎折處的不連續性與相鄰線的電容寄生效應變大,這反而對高速訊號的設計是非常不利的,未蒙其利,先受其害。

本文將以DDRII為例,說明貫孔換層,與相鄰貫孔的clearance hole (anti-pad)把內層plane打破,對訊號的影響。

另外,走線長度差異所造成的delay只是total timing skew的因素之一,不一定是關鍵的因素,反而過嚴的等長要求或過度繞蛇線會造成SI\EMI惡化。

我們該注意的是。

以最短的蛇線滿足設計要求、維持至少2W rule (DDRII如果有開ODT, 甚至1W也可),並確保地迴路的連續性。

文章目录[显示]控制線長誤差在300mils以內的DDRII Addr\Cmd\Ctrlgroup (serpentine routing)本例其實不算是過嚴的length-matching routing,因為尚容許走線之間300mils的長度差。

黃色是走線在layer 1與layer 4,但layer 4走線被layer 2 plane(綠色是GND net)遮住了所以看不到。

以Designer\Nexxim模擬模擬結果整個group total skew大約190ps (with Rs=22 ohm),且可以看到走線分成兩群,波形SI較佳的是走在top layer沒有過孔換層的,波形SI較差且時間延遲較大的是走在bottom layer有一次過孔換層的。

Rs=22W,overshoot\undershoot沒有超標控制線長誤差在50mils以內的DDRII Data Group (serpentine routing)Layout雖然滿足data group內的線長差異控制在50mils以內,但整個走線太長沒有最佳化,多繞了一些蛇線:沒有開ODT,但有串連終端Rs=22W,模擬結果發現overshoot\undershoot過大,且眼圖很差;這是一個過度繞蛇線導致眼圖較差的實例修改後的layout同樣滿足data group內的線長差異在50mils以內,但整個走線有最佳化總線長縮短300mils,且線與線之間保持3W space,繞蛇線的程度較輕微,如下圖所示沒有開ODT,但有串連終端Rs=22W,模擬結果發現眼圖有明顯改善完全不管線長差異的Addr\Cmd\Ctrl Group (走線要求as short as possible and straight forward)沒有VDDQ-GND de-coupling capacitor,且BGA下方的地,被相鄰的anti-pad (clearance hole)打破下圖所示為一群DDRII的Addr\Cmd\Ctrl bus,且在主控IC的BGA正下方,可見一整排的via打破了內層plane,其中綠色是layer 2 ground plane,黃色走線在layer 1,另外layer 4也有走線,但被layer 2 plane遮住了所以看不到。

模擬結果整個group total skew大約800ps (Rs=22),會這麼差並不是因為走線沒取等長造成的,主要是因為此例還沒有加de-coupling capacitor 0.1uF於VDDQ-GND之間,所以走線只要一換層(從top轉到bottom),地迴路的連續性就被破壞了有VDDQ-GND de-coupling capacitor,且BGA下方被相鄰的anti-pad打破的地,用網線補起來(grid ground)模擬結果顯示,整個group total skew大約310ps (Rs=22);這是因為增加了VDDQ-GND之間的0.1uF,減輕因為換層走線造成的地迴路不連續issue。

此例在anti-pad之間補細線的方式,一開始是透過PADS PCB layout tool施作,再由SIwave import .pcb轉出.siw的,在這轉換過程中,SIwave雖然視這些ground line為GND net,但在屬性上還是把它當trace而不是copper的一部份,而Ansoft 處理trace與copper plane的方法是不同的,這可能會導致模擬結果有差異,無法完全呈現補grid ground後的ground plane performance針對補grid ground這部份,我們在SIwave中用”Draw Rectangle”選擇”Merge”,再重新補一次,如下圖所若整個project有很多net=GND的trace要改成plane,選定net後,執行Tools\ Convert Traces To Planes模擬結果顯示,整個group total skew一樣大約310ps (Rs=22),但這次很明顯的看出走在layer 1的訊號是一群,走在layer 4的訊號是一群,後者delay與over-shoot\under-shoot都較大。

這波形就很清楚的呈現了走線在top layer沒有過孔換層,與走線經過貫孔走bottom layer的差異就將近200ps了,剩下因為線長的差異所引起的timing skew其實只有數十ps。

只要減小PCB板厚(減輕via effect),將可以很看到這兩群訊號SI特性較一致,且時序也接近的改善效果Rs=22W undershoot超出標準模擬結果顯示,改Rs=33W,整個group total skew大約295ps改Rs=33W,undershoot改善了完全不管線長差異的Data Group (走線要求as short as possible and straight forward)模擬結果跟section 2.1一樣都很差,沒有sec. 2.2來的好,主要的修改是走線拉直取最短,但這不是比sec. 2.2差的主因,變差的主因是沒有維持3W▪高密度小BGA封裝的高速PCB設計,應盡量避免內層的plane(不管是power或ground plane)被相鄰的一整排anti-pad打破,形成破壞地迴路連續性的slot。

改善方法是在anti-pad 之間,在PCB製程可以確保良率的前提下,補細線成grid ground,這對SI\PI的改善非常顯著,且這種技巧因為在PCB內層施作,由外觀上不易識別出來,是板級設計技術差異的關鍵之一。

▪以DDRII-800 point-point routing的Addr\Cmd\Ctrl Group而言,即使完全不繞蛇線也OK。

而對Data group總線長1000mils以上,些微的蛇線做length-matching會好一點;若總線長可做在1000mils以內,即使完全不繞蛇線、不用ODT也OK;point-to-point的DDR routing,data group的走線可以縮到總線長600mils以內。

線越短、繞蛇線的部份越少越好;另外3W rule的影響在DDRII-800於四層板施作的影響較小,2W rule即可。

如果打開ODT或伴地線則可以1W施作Anti-pad補充說明繞蛇線的幾個原則繞蛇線的間距— isolate space有些是寫15~20mils、有些是寫3W、有些是寫6H…這都對,但若考慮物理意義來說,應該以相對於堆疊高度的定義6H比較好螺旋型蛇線效果較好[1]差動對繞蛇線的原則—繞線盡量集中在產生線長差異的那一端,主要是為了保有差動對可以抗CM noise的物理特性(這點讀者可以想一下,很有意思的)3W rule在四層板真的有這麼重要嗎?看也些板子只留1W,DDRII-666或DDRII-800也可以跑的動呀?Ans:筆者這裡所強調的是較理想的作法,依此建議可以輕易做到不開ODT(省電,省熱耗)而跑到DDRII-800,但您如果用1W走線,可能就要犧牲量產時對各家DDRII的window餘量,甚至要打開ODT才可以原文链接:http://www.oldfriend.url.tw/SIwave/Antipad_Slot_Serpentine_Routing.htm原创文章,转载请注明:转载自吴川斌的博客 /。