PCB常见平板电脑阻抗压合结构图

PCB线路板常用阻抗设计及叠层结构

PCB线路板常用阻抗设计及叠层结构PCB线路板(Printed Circuit Board)是现代电子设备中常用的一种基础组件,用于支持和连接电子元件,实现电路功能。

在PCB设计过程中,阻抗是一个重要的设计参数,特别是在高频信号传输和高速数字信号传输中。

1.电源和地线:电源和地线通常被设计成具有低阻抗的结构,以确保稳定的电源供应和良好的信号接地。

在PCB布局中,电源和地线一般会采用较宽的铜箔,以降低电阻和电感。

2.信号线:对于高速数字信号和高频信号的传输,常常需要控制信号线的阻抗。

阻抗匹配可以提高信号传输的带宽和抗干扰能力。

常见的阻抗设计包括单端阻抗和差分阻抗。

单端线路一般采用50欧姆的阻抗,而差分线路一般采用90欧姆的阻抗。

3.地平面:在高速数字信号传输中,地平面既可以作为信号的返回路径,同时也可以帮助抑制信号的辐射和干扰。

为了保持地平面的阻抗一致性,通常会在地平面上布满大面积的铜箔,以降低电阻和电感。

5.间距和宽度:阻抗的大小与线路的宽度和间距密切相关。

调整线路的宽度和间距可以实现对阻抗的精确控制。

在设计过程中,可以使用专业的PCB设计工具进行阻抗仿真和优化,以满足设计需求。

对于PCB线路板的叠层结构,常见的设计包括以下几种:1. 单面板(Single Layer PCB):单面板是最简单的PCB结构,只有一层导电层,通常用于简单的电路或低成本的产品中。

2. 双面板(Double Layer PCB):双面板具有两层导电层,信号可以在两层之间进行传输。

双面板可以实现更复杂的电路布局和更高的密度,通常用于中等复杂度的产品。

3. 多层板(Multilayer PCB):多层板由内外多个导电层组成,其中通过绝缘层来隔离。

多层板可以实现更高的集成度和更复杂的布局,用于高速数字信号传输和复杂电路的设计。

4. 刚性-柔性板(Rigid-Flex PCB):刚性-柔性板结合了刚性电路板和柔性电路板的优势。

PCB阻抗多层板:层压结构及参数

阻抗多层板:层压结构及参数阻抗计算的几个注意事项(1)线宽宁愿宽,不要细。

因为我们知道制程里存在细的极限,宽是没有极限的。

如果到时候板厂为了调阻抗把线宽调细而碰到细的极限时那就麻烦了,要么增加成本,要么范松阻抗管控,要么修改设计...所以在计算时相对宽就意味着目标阻抗稍微偏低,比如50欧姆,我们算到49欧姆就可以了,尽量不要算到51欧姆。

(2)整体呈现一个趋势。

我们的设计中可能有多个阻抗管控目标,那么就整体偏大或偏小,不要100欧姆的偏大,90欧姆的偏小(3)考虑残铜率和流胶量。

当半固化片一边或两片是蚀刻线路时,压合过程中胶会去填补蚀刻的空隙处,这样两层间的胶厚度会减小,残铜率越小,填的越多,剩下的越少。

所以如果你需要的两层间半固化片厚度是5mil,要根据残铜率选择稍厚的半固化片。

(4)指定玻璃布型号和含胶量。

看过板材datasheet都知道不同的玻璃布,不同的含胶量的半固化片或者芯板的节点系数是不同的,即使是差不多高度的也可能是3.5和4的差别,这个差别可以引起单线阻抗3欧姆左右的变化。

另外玻纤效应和玻璃布开窗大小密切相关,如果你是10Gbps或更高速的设计,而你的叠层又没有指定材料,板厂用了单张1080的材料,那就可能出现信号完整性问题。

(5)多和板厂沟通当然残铜率和流胶量有时候计算会有误差,新材料的介电系数有时和标称不一致,有的玻璃布板厂没有备料等等都会造成设计的叠层实现不了或者交期延后。

出现这些情况的时候,最好的办法就是在设计之初让板厂按设计师的要求,根据他们的经验设计个叠层,经过多次的沟通和确认,这样最多几个来回就可以得到理想的叠层,方便后续的设计。

层叠设计关于层叠和阻抗设计,设计师需要经历的几个阶段(1)小白级:刚接触PCB设计的时候,可能所涉及的产品非常简单不属于高速的范畴,完全不需要控制阻抗,把线拉通就完事了,运气好点的工程师刚涉及PCB设计的时候就能接触高速的产品,但是却不知道要控制阻抗,导致设计出问题;(2)初级:经过一段时间的PCB设计,慢慢了解到阻抗相关的一些概念,具备了高速电路的一些基本知识,知道了控制阻抗的必要性,但是缺乏PCB材料和工艺制程以及阻抗计算相关的一些知识,对阻抗的认识还不是很深,只知道控阻抗需要提供阻抗需求表给板厂给板厂来控。

PCB阻抗设计与阻抗类型图解

PCB阻抗设计与阻抗类型图解(仅限交流与学习使用,请勿用于其它作用)A、阻抗定义阻抗就是指在某一频率下,电子器件传输信号线中(也就是我们制作的线路板的铜线),相对某一参考层(也就是我们说的屏蔽层、影射层或参考层),其高频信号或电磁波在传播过程中所受的阻力称之为特性阻抗,它实际上是电阻抗、电感抗、电容抗等一个矢量总和。

在直流电中,物体对电流阻碍的作用叫做电阻;在交流电的领域中除了电阻会阻碍电流以外,电容及电感也会阻碍电流的流动,这种作用就称之为电抗,意即抵抗电流的作用。

电容及电感的电抗分别称作电容抗及电感抗,简称容抗及感抗。

从一个器件输出信号,经传输后进入另一个器件,这两者阻抗之间的特定匹配关系。

简单说整个过程就像软管送水浇花,一端接在水龙头,另一端手握处加压使其射出水柱,当握管处所施压的力道恰好,而让水柱的射程正确洒落在目标区为最佳,力过度水注射程太远,腾空越过目标浪费水资源,挤压不足以致射程太近者,则照样得不到想要的结果。

阻抗就是施压的力道,保障发出的信号经传输后能准确匹配接收端的需求影响特性阻抗的因数1) 介质介电常数,与特性阻抗值成反比(Er)2)线路层与接地层(或外层)间介质厚度,与特性阻抗值成正比(H)3) 阻抗线线底宽度(下端W1);线面(上端W2)宽度,与特性阻抗成反比。

4) 铜厚,与特性阻抗值成反比(T)5) 相邻线路与线路之间的间距,与特性阻抗值成正比(差分阻抗)(S)6) 基材阻焊厚度,与阻抗值成反比(C)B、模型分类阻抗线可分为6类:1、单端阻抗线2、差分阻抗线3、单端共面地阻抗线4、差分共面地阻抗线5、层间差分阻抗线(包含:异层差分)6、共模阻抗外层单端外层差分外层单端共面地外层差分共面地常见的几种阻抗模型内层单端[两面屏蔽]内层差分[两面屏蔽]内层单端共面地[两面屏蔽]内层差分共面地[两面屏蔽]特殊的阻抗模型层间差分各类阻抗线在实际PCB文件中的效果图各类阻抗线在实际PCB文件中的效果图各类阻抗线在实际PCB文件中的效果图深圳拓普西科技有限公司Thank You!Mar, 2014Tuopx Co., Ltd. Confidential Slide 11。

PCB常用阻抗设计方案及叠层

PCB常用阻抗设计方案及叠层PCB(Printed Circuit Board,印刷电路板)是电子设备中最常见的一种电路板,用于连接和支持电子组件。

在PCB设计中,阻抗是一个重要的考虑因素,特别是在高频电路和信号传输中。

以下是PCB常用阻抗设计方案及叠层的介绍:1.阻抗定义和常见值:阻抗是指电路中电流和电压之间的比率,表示电路对交流信号的阻碍程度。

在PCB设计中,常见的阻抗值包括50Ω,75Ω和100Ω等,其中50Ω应用最为广泛。

2.单层PCB阻抗设计:在单层PCB设计中,通过控制信号线的宽度和距离来实现特定的阻抗值。

一般来说,信号线的宽度越宽,阻抗越低。

在设计过程中,可以使用阻抗计算工具或阻抗计算公式来确定合适的信号线宽度。

3.双层PCB阻抗设计:在双层PCB设计中,可以使用不同的叠层结构来实现特定的阻抗值。

常见的叠层结构包括两层相邻的信号层,两层信号层之间夹一层地层,以及两层信号层之间夹一层电源层等。

4.多层PCB阻抗设计:多层PCB通常包含四层或六层,在更高层数的PCB中,可以使用更复杂的阻抗设计方案。

常见的多层PCB阻抗设计方案包括均匀分布阻抗线和差分阻抗线。

5.均匀分布阻抗线:均匀分布阻抗线是指在PCB内部平面层上均匀分布的阻抗线。

通过控制平面层与信号层之间的距离和信号层上的信号线宽度,可以实现特定的阻抗值。

这种设计方案适用于高频电路和差分信号传输。

6.差分阻抗线:差分阻抗线是指将信号和其反相信号同时传输在两条平行的信号线上。

差分信号传输具有很好的抗干扰能力和信号完整性。

在PCB设计中,通过控制差分信号线和地线之间的距离和信号线宽度,可以实现特定的阻抗值。

总之,PCB阻抗设计是非常重要的一部分,在高频电路和信号传输中尤其关键。

通过合理选择信号线宽度、距离以及叠层结构等设计参数,可以实现所需的阻抗值。

在PCB设计过程中,可以借助专业的设计软件和计算工具,以及参考相关的设计规范和指南来进行阻抗设计。

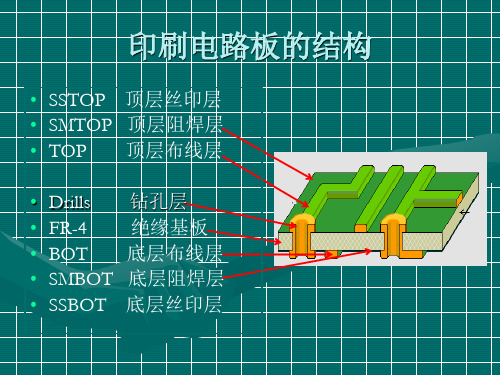

阻焊层板图SolderMask丝印层板图

• Rotation栏设置器件转角参数。

• Increment:器件旋转角度

• Snap:转角解析度,调整角度最小量。

•

设 置 板 层

• 点击按键 ,或点击Tools/layer/select from Spreedsheet调出板层 设置表。该四层板分为顶层、底层和Inner1、Inner2两个内层, 其状态均为Routing。另有Gnd和Pawer的状态为Plane,为两个 电源板层。将inner1和inner2等不用的板层改为Unused,这两个 板层即被取消,四层板变为只有顶层和底层的两层板设置。

• 在Capture 执行项目管理器 命令 Tools/Create Netlist

• 如图选择参数 • 确定后生成Layout电连接

网表.mnl • 选择英制单位 • OrCAD中是以电连接网表

文件的形式将设计好的电 路图传递给PCB设计软件 的。

PCB设计流程

➢ 调用OrCAD/Layout Plus软件,出现Layout Plus管理窗口,进 入PCB设计。

• 打开layout/tools/Library Manager • 电阻的封装是在TM_AXIAL 库中

的AX/RC05 • 无极性电容的封装是TM_RAD中

的 RAD/CK05 • 晶体管的封装是在TO库中的

TO237AA • CON2的封装在LAYOUT库中的

TP/2P

电阻的封装

PCB设计的文件

➢ 指定板框文件(.tpl)及技术文件(.tch),确定PCB设计过 程采用的设计环境和运用的策略。初学者可直接选用软件提 供的Default文件。

➢ 调入电路连接网表文件(.mnl)。若未调入.mnl文件,表示 在Layout Plus中将不调入电路图设计,只是应用Layout Plus软 件采用手工设计方法设计一个PCB。

印制电路板(PCB)的阻抗控制介绍

印制电路板(PCB)的阻抗控制介绍一:特性阻抗原理:传输线的定义,在国际标准IPC-2141 3.4.4说明其原则“当 信号在导线中传输时,若该导线长度大到信号波长的1/7,则该导线应被视做传输线。

如当某电磁波信号以时钟频率为900MHZ (GSM手机传输频率)在导线中传播时,则如果线路的长度大于:1/7波长=1C/7F=4.76CM 时,该线路就被定义为传输线。

众所周知,直流电路中电流传输时遇到的阻力叫电阻,交流电路中电流遇到的阻力叫阻抗而高频(》400MHZ )电路中传输信号所遇到的阻力叫特性阻抗,在高频情况下,印制板上的传输信号铜导线可以被视为由一串等效电阻及一并连电感所组合而成的传导线路,而此等效电阻在高频分析时小到可以忽略不记,因此我们在对一个印制板的信号传输进行高频分析时,则只需考虑杂散分布之串联电感及并联电容的效应,我们可以得到以下公式;Z0=R+√L/C √≈√L/C ( Z0为特性阻抗值)关于特性阻抗,有以下几原则:1、 在数字信号在板子上传输时,印制板线路的特性阻抗值必须与头尾元件的电子阻抗匹配,如果不匹配的话,所传送的信号能量将出现反射,散失,衰减,或延误,等现象,从而产生杂信,2、 由于电子元件的电子阻抗越高时,其传输速率才越快,因而电路板的特性阻抗值也要随之提高,才能与之匹配,3、射频通信用的PCB ,除强调 Z0外,有时更加强调板材本身具有低的 Er (介质常数)值及低的Df (介质损耗因子)值。

高频信号在介质中的传输速度为C/ Er,可知:Er 越小,传输速度越快,这也是为何高频要用低介质常数的高频材料。

Df 影响着信号在介质传输过程中的失真,Df 越小,失真越小。

二:特性阻抗的常见形式和计算方法:在线路板的设计中,传输信号最常见的有4种单线布线和2种差分布线方式方式:以上四种单线传输信号布线方式的阻抗计算公式见下;(差分略)1、 微带线:Z 。

=87ln 「5.98H/(0.8W+T )」Er+1.412、 埋入式微带线Z 。

PCB阻抗设计参考

前言为保证信号传输质量、降低EMI干扰、通过相关的阻抗测试认证,需要对PCB关键信号进行阻抗匹配设计。

本设计指南是综合常用计算参数、电视机产品信号特点、PCB Layout实际需求、SI9000软件计算、PCB供应商反馈信息等,而最终得出此推荐设计。

适用于大部分PCB供应商的制程工艺标准和具有阻抗控制要求的PCB板设计。

一、 双面板阻抗设计100欧姆差分阻抗推荐设计①、包地设计:线宽、间距 7/5/7 mil地线宽度≥20mil信号与地线距离6mil,每400mil内加接地过孔;②、不包地设计:线宽、间距 10/5/10mil差分对与对之间距离≥20mil(特殊情况不能小于10mil)建议整组差分信号线外采用包地屏蔽,差分信号与屏蔽地线距离≥35mil(特殊情况不能小于20mil)。

90欧姆差分阻抗推荐设计①、包地设计:线宽、间距 10/5/10mil地线宽度≥20mil信号与地线距离6mil或5mil,每400mil内加接地过孔;②、不包地设计:线宽、间距 16/5/16mil差分对与对之间距离≥20mil建议整组差分信号线外采用包地屏蔽,差分信号与屏蔽地线距离≥35mil(特殊情况不能小于20mil)。

要领:优先使用包地设计,走线较短并且有完整地平面可采用不包地设计;计算参数:板材FR-4,板厚1.6mm+/-10%,板材介电常数4.4+/-0.2,铜厚1.0盎司(1.4mil)阻焊油厚度 0.6±0.2mil,介电常数 3.5+/-0.3图1 包地设计图2 不包地设计二、四层板阻抗设计100欧姆差分阻抗推荐设计线宽、间距 5/7/5mil差分对与对之间距离≥14mil(3W准则)注:建议整组差分信号线外采用包地屏蔽,差分信号与屏蔽地线距离≥35mil(特殊情况不能小于20mil)。

90欧姆差分阻抗推荐设计线宽、间距 6/6/6mil差分对与对之间距离≥12mil(3W准则)要领:在差分对走线较长情况下,USB的差分线建议两边按6mil的间距包地以降低EMI风险(包地与不包地,线宽线距标准一致)。

阻抗计算说明及图解

PCB 层数 1 2 3 4 5 6 7 8

6A 层板设置 TOP GND VCC SING GND BOTTOM

注:TOP 层成品铜厚 1OZ。

6A 层板设置(图示)

6B 层板设置 TOP VCC SING SING GND BOTTOM

8 层板设置 TOP GND SING VCC GND SING GND BOTTOM

15. L4 层 SING 90 Байду номын сангаас姆共面差分阻抗,参考层 L3 层 VCC& L5 层 GND:

16. L4 层 SING 100 欧姆共面差分阻抗,参考层 L3 层 VCC& L5 层 GND:

适用范围:内层差分共面阻抗,参考层为 同一层面的 GND/VCC 及与其邻近的两 个 GND/VCC 层 。( 阻 抗 线 被 周 围 GND/VCC 包围,周围 GND/VCC 即为 参考层面)。 参数说明: H1:阻抗线路层到其邻近 GND/VCC 层之间的介质厚度 H2:阻抗线路层到其较远 GND/VCC 层之间的介质厚度 W2: 阻抗线线面宽度 W1: 阻抗线线底宽度 D1:阻抗线与 GND/VCC 之间的距离 T1:线路铜厚=基板铜厚 S1:差分阻抗线间隙 Er1:H1 对应介质层介电常数 Er2:H2 对应介质层介电常数

5. L4 层 SING 50 欧姆特性阻抗,参考层 L3 层 VCC& L5 层 GND:

ALICE

适用范围:两个 VCC/GND 夹一个线 路层之阻抗计算 参数说明: H1:线路层到较近之 VCC/GND 间 距离 H2:线路层到较远之 VCC/GND 间 距离+线路层铜厚 Er1:介质层介电常数(线路层到相邻 VCC/GND 间介质) Er2:介质层介电常数(线路层到较远 VCC/GND 间介质) W2:阻抗线线面宽度 W1: 阻抗线线底宽度

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

No.L1--------------------------1/3oz + Plating2116*1 4milL2-------------------------0.7 H/H mm 含铜L3-------------------------2116*1 4milL4-------------------------1/3oz + Plating压合厚度:0.9±0.1MM成品厚度:1.0±0.1MMPP厚度为填胶后厚度阻抗计算:L1/L4(屏蔽层L2/L3):单端:线宽 6.5mil ,阻值 50Ω±10%单端:线宽 4.5mil ,阻值 60Ω±10%差分:线宽6mil,线距6mil,阻值 90Ω±10%差分:线宽5mil,线距7mil,阻值 100Ω±10%No.L1--------------------------1/3oz + Plating1080*1 3milL2-------------------------0.7 H/H mm 含铜(偏上限料)L3-------------------------1080*1 3milL4-------------------------1/3oz + Plating压合厚度:0.9±0.1MM成品厚度:1.0±0.1MMPP厚度为填胶后厚度阻抗计算:L1/L4(屏蔽层L2/L3):单端:线宽 5mil ,阻值 50Ω±10%单端:线宽 4mil ,阻值 55Ω±10%差分:线宽4.5mil,线距5.5mil,阻值 90Ω±10%差分:线宽3.5mil,线距5.5mil,阻值 100Ω±10% L3(屏蔽层L2&L4):差分:线宽3.5mil,线距6mil,阻值 90Ω±10%No.L1--------------------------1/3oz + Plating1080*1 3milL2-------------------------0.9MM 1/1 OZ 含铜L3-------------------------1080*1 3milL4-------------------------1/3oz + Plating压合厚度:1.1±0.1MM成品厚度:1.2±0.1MMPP厚度为填胶后厚度阻抗计算:L1/L4(屏蔽层L2/L3):单端:线宽 4.7mil ,阻值 50Ω±10%单端:线宽 3.8mil ,阻值 55Ω±10%差分:线宽4.5mil,线距5.5mil,阻值 90Ω±10%差分:线宽3.5mil,线距5.5mil,阻值 100Ω±10%L3(屏蔽层L2&L4):单端:线宽 3mil ,阻值 55Ω±10%差分:线宽3mil,线距8mil,阻值 100Ω±10%No.L1--------------------------1/3oz + Plating2116*1 4milL2-------------------------0.15 H/H mm 含铜L3-------------------------7628*2 15milL4-------------------------0.15 H/H mm 含铜L5-------------------------2116*1 4milL6-------------------------1/3oz + Plating压合厚度:0.9±0.1MM成品厚度:1.0±0.1MMPP厚度为填胶后厚度阻抗计算:L1/L6(屏蔽层L2/L5):单端:线宽 11mil ,阻值 60Ω±10%(阻抗层L1,屏蔽层L3)单端:线宽 4mil ,阻值 60Ω±10%差分:线宽4mil,线距4.5mil,阻值 100Ω±10%L3(屏蔽层L2&L4):单端:线宽 4mil ,阻值 60Ω±10%差分:线宽4mil,线距5mil,阻值 100Ω±10%No.L1--------------------------1/3oz + Plating2116*1 4milL2-------------------------0.2 H/H mm 含铜L3-------------------------2116*2 10milL4-------------------------0.2 H/H mm 含铜L5-------------------------2116*1 4milL6-------------------------1/3oz + Plating压合厚度:0.9±0.1MM成品厚度:1.0±0.1MMPP厚度为填胶后厚度阻抗计算:L1/L6(屏蔽层L2/L5):单端:线宽 18.5mil ,阻值 50Ω±10%(阻抗层L1,屏蔽层L3)单端:线宽 5mil ,阻值 55Ω±10%差分:线宽5.5mil,线距6mil,阻值 90Ω±10%差分:线宽4mil,线距6mil,阻值 100Ω±10%L4(屏蔽层L3&L5):单端:线宽 5mil ,阻值 55Ω±10%差分:线宽6mil,线距6mil,阻值 90Ω±10%差分:线宽4mil,线距4.5mil,阻值 100Ω±10%No.L1--------------------------1/3oz + Plating1080*1 3milL2-------------------------0.15MM 1/1 含铜L3-------------------------7628*2 16milL4-------------------------0.15MM 1/1 含铜L5-------------------------1080*1 3milL6-------------------------1/3oz + Plating压合厚度:0.9±0.1MM成品厚度:1.0±0.1MMPP厚度为填胶后厚度阻抗计算:L1/L6(屏蔽层L2/L5):单端:线宽 13.5mil ,阻值 50Ω±10%(阻抗层L1,屏蔽层L3)单端:线宽 4.6mil ,阻值 50Ω±10%差分:线宽4.2mil,线距4.5mil,阻值 90Ω±10%差分:线宽3.5mil,线距5.5mil,阻值 100Ω±10%L4(屏蔽层L3&L5):单端:线宽 4mil ,阻值 50Ω±10%差分:线宽3mil,线距7mil,阻值 100Ω±10%No.L1--------------------------1/3oz + Plating1080*1 3milL2-------------------------0.15MM 1/1OZ 含铜L3-------------------------7628*2 16milL4-------------------------0.15MM 1/1OZ 含铜L5-------------------------1080*1 3milL6-------------------------1/3oz + Plating压合厚度:0.9±0.1MM成品厚度:1.0±0.1MMPP厚度为填胶后厚度阻抗计算:L1/L6(屏蔽层L2/L5):单端:线宽 4.7mil ,阻值 50Ω±10%差分:线宽4.7mil,线距6mil,阻值 90Ω±10%差分:线宽4mil,线距8mil,阻值 100Ω±10%L4(屏蔽层L3&L5):差分:线宽3.2mil,线距8.8mil,阻值100Ω±10%No.L1--------------------------1/3oz + Plating1080*1 3milL2-------------------------0.2 1/1 mm 含铜L3-------------------------7628*2+2116*1 20milL4-------------------------0.2 1/1 mm 含铜L5-------------------------1080*1 3milL6-------------------------1/3oz + Plating压合厚度:1.1±0.1MM成品厚度:1.2±0.1MMPP厚度为填胶后厚度阻抗计算:L1/L6(屏蔽层L2/L5):单端:线宽 5mil ,阻值 50Ω±10%单端:线宽 4mil ,阻值 55Ω±10%差分:线宽 5mil,线距8mil,阻值 90Ω±10%差分:线宽 3.5mil,线距4.5mil,阻值 100Ω±10% L3(屏蔽层L2&L4):单端:线宽 5mil ,阻值 55Ω±10%差分:线宽 5mil,线距5.5mil,阻值 90Ω±10%No.L1--------------------------1/3oz + Plating1080*1 3milL2-------------------------0.15MM 1/1OZ 含铜L3-------------------------7628*3 24milL4-------------------------0.15MM 1/1OZ 含铜1080*1 3milL6-------------------------1/3oz + Plating压合厚度:1.1±0.1MM成品厚度:1.2±0.1MMPP厚度为填胶后厚度阻抗计算:L1/L6(屏蔽层L2/L5):单端:线宽 4.6mil ,阻值 50Ω±10%单端:线宽 3.7mil ,阻值 55Ω±10%差分:线宽 4mil,线距4.5mil,阻值 90Ω±10%差分:线宽 3.3mil,线距5mil,阻值 100Ω±10% L3(屏蔽层L2&L4):单端:线宽 3.2mil ,阻值 55Ω±10%差分:线宽 3.5mil,线距5.5mil,阻值 90Ω±10%差分:线宽 3mil,线距7mil,阻值 100Ω±10%No.L1--------------------------1/3oz + Plating1080*1 3milL2-------------------------0.15 1/1 mm 含铜L3-------------------------2116*1 5mil-------------------------0.4 H/H mm 含铜(蚀刻成光板)-------------------------2116*1 5milL4-------------------------0.15 1/1 mm 含铜L5-------------------------1080*1 3milL6-------------------------1/3oz + Plating压合厚度:1.1±0.1MM成品厚度:1.2±0.1MMPP厚度为填胶后厚度阻抗计算:L1/L6(屏蔽层L2/L5):单端:线宽 5mil ,阻值 50Ω±10%单端:线宽 4mil ,阻值 55Ω±10%差分:线宽 4mil,线距4mil,阻值 90Ω±10%L4(屏蔽层L2&L5):单端:线宽 3.5mil ,阻值 55Ω±10%差分:线宽 3.3mil,线距4.7mil,阻值 90Ω±10%No.L1--------------------------1/3oz + Plating2116*1 4.6mil0.2 H/H mm 含铜L3-------------------------2116*1 4.6milL4-------------------------0.2 H/H mm 含铜L5-------------------------2116*1 4.6milL6-------------------------0.2 H/H mm 含铜L7-------------------------2116*1 4.6milL8-------------------------1/3oz + Plating压合厚度:1.1±0.1MM成品厚度:1.2±0.1MMPP厚度为填胶后厚度阻抗计算:L1/L8(屏蔽层L2/L7):单端:线宽 7.87mil ,阻值 50Ω±10%单端:线宽 4mil ,阻值 65Ω±10%差分:线宽 4.5mil,线距5mil,阻值 100Ω±10% L3(屏蔽层L2&L4):单端:线宽 4mil ,阻值 55Ω±10%差分:线宽 4mil,线距8mil,阻值 100Ω±10%L5(屏蔽层L4&L6):单端:线宽 4mil ,阻值 55Ω±10%差分:线宽 4mil,线距8mil,阻值 100Ω±10%L6(屏蔽层L5&L7):单端:线宽 4mil ,阻值 55Ω±10%差分:线宽 4mil,线距8mil,阻值 100Ω±10%No.L1--------------------------1/3oz + Plating2116*1 4milL2-------------------------0.6 H/H mm 含铜L3-------------------------2116*1 4milL4-------------------------1/3oz + Plating压合厚度:0.8±0.1MM成品厚度:0.9±0.1MMPP厚度为填胶后厚度阻抗计算:L1/L4(屏蔽层L2/L3):单端:线宽 6mil ,阻值 50Ω±10%单端:线宽 4mil ,阻值 60Ω±10%No.L1--------------------------1/3oz + Plating2116*1 4milL2-------------------------0.7 1/1 mm 含铜L3-------------------------2116*1 4milL4-------------------------1/3oz + Plating压合厚度:0.9±0.1MM成品厚度:1.0±0.1MMPP厚度为填胶后厚度阻抗计算:L1/L4(屏蔽层L2/L3):单端:线宽 6mil ,阻值 50Ω±10%单端:线宽 5mil ,阻值 55Ω±10%差分:线宽6mil,线距7mil,阻值 90Ω±10%差分:线宽4mil,线距5.5mil,阻值 100Ω±10%No.L1--------------------------1/3oz + Plating1080*1 3milL2-------------------------0.7 H/H mm 含铜L3-------------------------1080*1 3milL4-------------------------1/3oz + Plating压合厚度:0.9±0.1MM成品厚度:1.0±0.1MMPP厚度为填胶后厚度阻抗计算:L1/L4(屏蔽层L2/L3):单端:线宽 6mil ,阻值 45Ω±10%单端:线宽 5mil ,阻值 50Ω±10%差分:线宽4.8mil,线距5.44mil,阻值 90Ω±10%差分:线宽4.5mil,线距8mil,阻值 95Ω±10%No.L1--------------------------1/3oz + Plating1080*1 2.8milL2-------------------------0.15 H/H mm 含铜L3-------------------------7628*2+1080*1 17.8milL4-------------------------0.15 H/H mm 含铜L5-------------------------1080*1 2.8milL6-------------------------1/3oz + Plating压合厚度:0.9±0.1MM成品厚度:1.0±0.1MMPP厚度为填胶后厚度阻抗计算:L1/L6(屏蔽层L2/L5):单端:线宽 14mil ,阻值 50Ω±10%(阻抗层L1,屏蔽层L3)单端:线宽 4.5mil ,阻值 50Ω±10%差分:线宽5mil,线距10mil,阻值 90Ω±10%差分:线宽4mil,线距9mil,阻值 100Ω±10%L3/L4(屏蔽层L2&L5):单端:线宽 5mil ,阻值 50Ω±10%差分:线宽5mil,线距5mil,阻值 90Ω±10%差分:线宽4mil,线距6mil,阻值 100Ω±10%No.L1--------------------------1/3oz + Plating1080*1 2.8milL2-------------------------0.15MM 1/1 含铜L3-------------------------7628*2+1080*1 17.8milL4-------------------------0.15MM 1/1 含铜L5-------------------------1080*1 2.8milL6-------------------------1/3oz + Plating压合厚度:0.9±0.1MM成品厚度:1.0±0.1MMPP厚度为填胶后厚度阻抗计算:L1/L6(屏蔽层L2/L5):单端:线宽 13mil ,阻值 50Ω±10%(阻抗层L1,屏蔽层L3)单端:线宽 4.3mil ,阻值 50Ω±10%差分:线宽4.3mil,线距5.7mil,阻值 90Ω±10%差分:线宽3.1mil,线距4.9mil,阻值 100Ω±10%L3/L4(屏蔽层L2&L5):单端:线宽 4mil ,阻值 50Ω±10%差分:线宽4mil,线距7.5mil,阻值 90Ω±10%差分:线宽3mil,线距7mil,阻值 100Ω±10%No.L1--------------------------1/3oz + Plating2116*1 4milL2-------------------------0.15 H/H mm 含铜L3-------------------------2116*1 4mil-------------------------0.8 H/H mm 含铜(蚀刻成光板)-------------------------2116*1 4milL4-------------------------0.15 H/H mm 含铜L5-------------------------2116*1 4milL6-------------------------1/3oz + Plating压合厚度:1.5±0.15MM成品厚度:1.6±0.15MMPP厚度为填胶后厚度阻抗计算:L1/L6(屏蔽层L2/L5):单端:线宽 5mil ,阻值 55Ω±10%差分:线宽 5mil,线距7.5mil,阻值 100Ω±10%L3(屏蔽层L2&L5):单端:线宽5mil ,阻值 55Ω±10%差分:线宽 5mil,线距7.5mil,阻值 100Ω±10%No.L1--------------------------1/3oz + Plating2116*1 4.5milL2-------------------------0.15 1/1 mm 含铜L3-------------------------7628*1 7mil-------------------------0.7 H/H mm 含铜(蚀刻成光板)-------------------------7628*1 7milL4-------------------------0.15 1/1 mm 含铜L5-------------------------2116*1 4.5milL6-------------------------1/3oz + Plating压合厚度:1.5±0.15MM成品厚度:1.6±0.15MMPP厚度为填胶后厚度阻抗计算:L1/L6(屏蔽层L2/L5):单端:线宽 6mil ,阻值 55Ω±10%差分:线宽 5.5mil,线距7mil,阻值 100Ω±10%L3/L4(屏蔽层L2&L5):单端:线宽4mil ,阻值 55Ω±10%差分:线宽 4.8mil,线距7.7mil,阻值 90Ω±10%差分:线宽 3.8mil,线距8.7mil,阻值 100Ω±10% No.L1--------------------------Hoz + Plating2116*1 4milL2-------------------------0.2MM 1/1OZ 含铜L3-------------------------2116*1 4mil1080*1 3milL4-------------------------0.2MM 1/1OZ 含铜L5-------------------------1506*1 6milL6-------------------------0.2MM 1/1OZ 含铜L7-------------------------1080*1 3mil2116*1 4milL8-------------------------0.2MM 1/1OZ 含铜L9-------------------------2116*1 4milL10-------------------------Hoz + Plating压合厚度:1.5±0.15MM成品厚度:1.6±0.16MMPP厚度为填胶后厚度阻抗计算:L1/L10(屏蔽层L2/L9):单端:线宽 6.5mil ,阻值 50Ω±10%差分:线宽5mil,线距8mil,阻值 100Ω±10%L3/L4(屏蔽层L2&L5): 单端:线宽 5.5mil ,阻值 50Ω±10%差分:线宽4.5mil,线距9mil,阻值 100Ω±10% L7/L8(屏蔽层L6&L9): 单端:线宽 5.5mil ,阻值 50Ω±10%差分:线宽4.5mil,线距9mil,阻值 100Ω±10%。