实验《二》:组合逻辑与时序逻辑电路的VHDL模型实验

时序逻辑电路和组合逻辑电路的设计。.

BEGIN WAIT UNTIL clk = ‘0’; ┇ AND PROCESS;

JK触发器

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY JKff_v1 IS

q <= d;

ELSIF ena='1' THEN

IF updown = '0' THEN q <= q+1;

IF q = 255 THEN COUT <= '1'; END IF;

ELSE

q <= q-1;

IF q = 0 THEN COUT <= '0'; END IF;

END IF;

END IF;

ELSIF (clk'EVENT AND clk = '1')THEN IF(J='0' AND K='1')THEN Q_temp <= '0'; QB_temp <= '1‘ ELSIF(J='1' AND K='0')THEN Q_temp <= '1'; QB_temp <= '0'; ELSIF(J='1' AND K='1')THEN Q_temp <= NOT Q_temp ; QB_temp <= NOT QB_temp; END IF;

BEGIN IF clr='0' THEN q_temp <= "00000000";

实验二 组合逻辑电路的设计 fpga

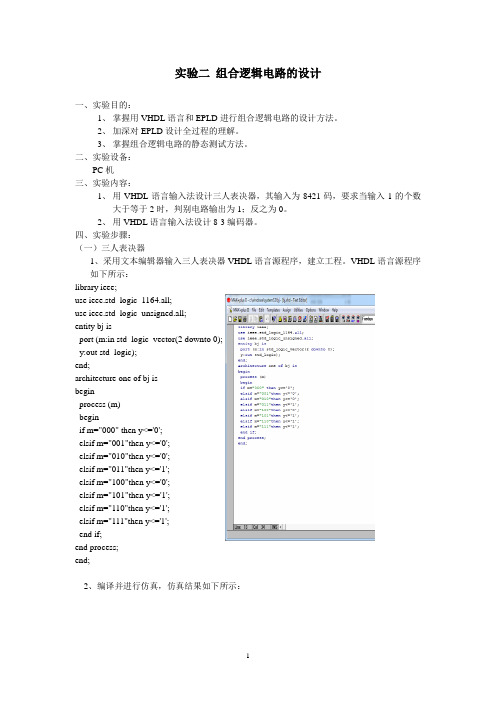

实验二组合逻辑电路的设计一、实验目的:1、掌握用VHDL语言和EPLD进行组合逻辑电路的设计方法。

2、加深对EPLD设计全过程的理解。

3、掌握组合逻辑电路的静态测试方法。

二、实验设备:PC机三、实验内容:1、用VHDL语言输入法设计三人表决器,其输入为8421码,要求当输入1的个数大于等于2时,判别电路输出为1;反之为0。

2、用VHDL语言输入法设计8-3编码器。

四、实验步骤:(一)三人表决器1、采用文本编辑器输入三人表决器VHDL语言源程序,建立工程。

VHDL语言源程序如下所示:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity bj isport (m:in std_logic_vector(2 downto 0);y:out std_logic);end;architecture one of bj isbeginprocess (m)beginif m="000" then y<='0';elsif m="001"then y<='0';elsif m="010"then y<='0';elsif m="011"then y<='1';elsif m="100"then y<='0';elsif m="101"then y<='1';elsif m="110"then y<='1';elsif m="111"then y<='1';end if;end process;end;2、编译并进行仿真,仿真结果如下所示:由仿真结果可以验证当输入1的个数大于等于2时,判别电路输出为1;反之为0。

vhdl实验报告

vhdl实验报告VHDL实验报告引言:VHDL(Very High Speed Integrated Circuit Hardware Description Language)是一种硬件描述语言,广泛应用于数字电路设计和仿真。

本篇实验报告将介绍我在VHDL实验中的学习和实践经验,包括实验目的、实验过程、实验结果以及对VHDL的理解和展望。

一、实验目的VHDL实验的主要目的是让我们掌握VHDL语言的基本语法和使用方法,能够利用VHDL描述数字电路,并通过仿真和综合工具进行验证和实现。

通过这些实验,我们可以深入了解数字电路的原理和设计方法,提高我们的逻辑设计能力和工程实践能力。

二、实验过程在实验过程中,我们首先学习了VHDL的基本语法,包括实体声明、端口声明、信号声明等。

然后,我们通过实例学习了VHDL的建模方法,包括组合逻辑电路的建模和时序逻辑电路的建模。

在组合逻辑电路的建模中,我们学习了使用逻辑运算符和条件语句描述电路的功能;在时序逻辑电路的建模中,我们学习了使用过程语句和时钟信号描述电路的状态转换。

在学习了VHDL的基础知识后,我们开始进行实验设计。

我们选择了一个简单的数字电路,如4位加法器,来进行实验验证。

首先,我们通过VHDL语言描述了加法器的功能和结构,包括输入端口、输出端口和中间信号。

然后,我们使用仿真工具进行了功能仿真,验证了加法器的正确性。

接着,我们使用综合工具将VHDL代码综合成门级电路,并进行了时序仿真和时序优化,验证了加法器的时序正确性和性能。

三、实验结果通过实验,我们成功地实现了4位加法器的功能,并验证了其正确性和性能。

在功能仿真中,我们输入了不同的测试数据,观察了输出结果,发现加法器能够正确地进行加法运算,并得到了正确的结果。

在时序仿真中,我们观察了电路的时序行为,包括输入信号的变化、输出信号的响应和中间信号的传播延迟等,发现加法器能够在时序上满足要求,并且具有较好的性能。

实验二 VHDL程序设计-时序逻辑模块(学生)

三.实验内容

• 利用基本的触发器、各种寄存器、计数器等模块, 设计一个由寄存器构成的时序模块。 • 在QuartusⅡ或ISE14.3中完成一个工程的设计、 编辑、综合和实现的全过程。 • 通过波段开关和LED指示灯进行控制和结果显示。 • 观察和分析仿真波形。

注:模块例程参见“附件3” 及实验指导书相关例程.

四.实验要求

• 画出各模块的VHDL程序的结构图(反映出 编程者的设计思路) • 画出模块的电路图 • 分析电路的仿真波形 • 记录设计和调试过程(遇到什么问题及如 何解决的?配合图表来比较说明)

1台 1套

Байду номын сангаас

二.实验任务

1. 完成时序逻辑模块的设计和仿真调试。

2.进一步掌握常用的语句的用法。

3. 利用TEC-CA-I开发板的I/O设备,用VHDL 语言编程,去控制输入/输出(I/O)设备。 4. 或利用ISE开发软件及XJECA开发板,用 VHDL语言编程,去控制输入/输出(I/O) 设备。

计算机组织与结构专题实验

西安交通大学计算机系

实验三. VHDL程序设计 —时序逻辑模块

一. 实验目的

• • • • 掌握Vhdl语言框架、编程及调试的方法 熟悉VHDL中的基本语法 掌握Altera QuartusⅡ平台的基本操作 掌握TEC-CA-I开发板的I/O应用

实验设备 • 装有QuartusⅡ6.0的计算机 • EP1C6Q240C6开发板

vhdl设计实验报告

vhdl设计实验报告VHDL设计实验报告引言VHDL(Very High Speed Integrated Circuit Hardware Description Language)是一种硬件描述语言,广泛应用于数字电路设计和验证。

本实验旨在通过设计一个简单的电路来熟悉VHDL语言的基本语法和设计流程。

一、实验背景数字电路是现代电子系统的基础,而VHDL则是描述和设计数字电路的重要工具。

VHDL可以帮助工程师们以一种形式化的语言来描述电路的功能和结构,从而实现电路的模拟和验证。

二、实验目的本实验的目的是通过使用VHDL语言设计一个简单的电路,加深对VHDL语言的理解,并掌握基本的电路设计流程。

三、实验步骤1. 确定电路功能在设计电路之前,首先需要明确电路的功能。

本实验中,我们选择设计一个4位加法器电路。

2. 设计电路结构根据电路功能的要求,设计电路的结构。

在本实验中,我们需要设计一个4位加法器,因此需要使用4个输入端口和一个输出端口。

3. 编写VHDL代码使用VHDL语言编写电路的描述代码。

在代码中,需要定义输入和输出端口的类型和位宽,并实现电路的功能。

4. 进行仿真使用仿真工具对设计的电路进行仿真,以验证电路的功能是否符合预期。

通过输入不同的测试数据,观察输出是否正确。

5. 下载到FPGA开发板将设计好的电路代码下载到FPGA开发板上进行验证。

通过连接输入信号和观察输出信号,验证电路在实际硬件上的运行情况。

四、实验结果与分析经过仿真和实际验证,我们设计的4位加法器电路在功能上符合预期。

输入不同的数据进行加法运算时,输出结果都正确。

五、实验总结通过本次实验,我们深入了解了VHDL语言的基本语法和设计流程。

通过设计一个简单的电路,我们掌握了VHDL的应用方法,并通过仿真和实际验证,加深了对电路设计的理解。

六、实验心得本实验让我对VHDL语言有了更深入的认识。

通过实际操作,我更加熟悉了VHDL的编写和仿真流程。

VHDL与数字电路设计实验报告

VHDL与数字电路设计实验报告引言本实验旨在通过使用VHDL编程语言和数字电路设计技术,实现特定功能的电路设计。

本文档将对实验的步骤、设计原理和结果进行详细描述。

实验步骤1. 步骤一:熟悉VHDL编程语言在实验开始之前,团队成员对VHDL编程语言进行了研究和熟悉。

我们了解了VHDL的基本语法、数据类型和结构,并获得了对VHDL设计原理的初步理解。

2. 步骤二:设计功能电路在本实验中,我们选择了一个特定的功能电路进行设计。

我们首先进行了功能需求分析,并根据需求确定了电路的输入输出信号以及主要的逻辑运算。

然后,我们使用VHDL编程语言将电路的逻辑运算实现为代码,并进行了仿真和测试。

3. 步骤三:电路仿真和验证为了验证我们设计的电路功能的正确性,我们使用了VHDL仿真工具进行了电路的仿真和验证。

我们根据输入信号的不同组合,观察输出信号的变化,并与我们预期的结果进行比较。

通过这一步骤,我们确认了我们设计的电路能够按照预期工作。

4. 步骤四:电路实现和测试在确认电路的设计和仿真结果无误之后,我们进一步将电路实现到实际的数字电路平台上,并进行了硬件测试。

我们使用实际的输入信号来测试电路的性能和稳定性,并对输出信号进行观察和分析。

通过这一步骤,我们验证了电路在实际环境中的可行性。

设计原理我们设计的电路基于特定的功能需求,采用了经典的数字电路设计原理。

通过使用VHDL编程语言,我们将电路的逻辑运算实现为逻辑门和触发器的组合。

通过将输入信号连接到适当的逻辑门和触发器,我们实现了所需的功能。

结果与分析经过实验步骤的完成,我们成功地设计和实现了一个具有特定功能的数字电路。

在仿真测试和实际测试中,电路都表现出了良好的性能和稳定性。

根据结果的分析,我们验证了电路的设计原理和逻辑的正确性。

结论本实验通过使用VHDL编程语言和数字电路设计技术,成功地实现了一个具有特定功能的电路设计。

我们的实验结果表明,VHDL和数字电路设计技术在电路设计领域具有重要的应用价值。

数电实验报告

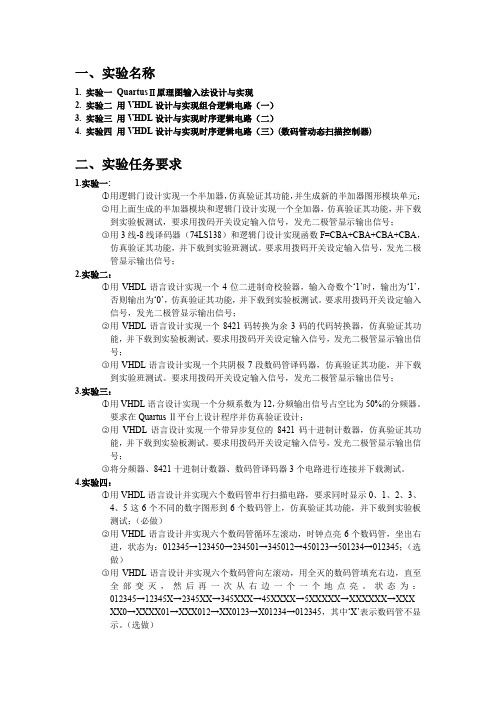

一、实验名称1. 实验一QuartusⅡ原理图输入法设计与实现2. 实验二用VHDL设计与实现组合逻辑电路(一)3. 实验三用VHDL设计与实现时序逻辑电路(二)4.实验四用VHDL设计与实现时序逻辑电路(三)(数码管动态扫描控制器)二、实验任务要求1.实验一:○1用逻辑门设计实现一个半加器,仿真验证其功能,并生成新的半加器图形模块单元;○2用上面生成的半加器模块和逻辑门设计实现一个全加器,仿真验证其功能,并下载到实验板测试,要求用拨码开关设定输入信号,发光二极管显示输出信号;○3用3线-8线译码器(74LS138)和逻辑门设计实现函数F=CBA+CBA+CBA+CBA,仿真验证其功能,并下载到实验班测试。

要求用拨码开关设定输入信号,发光二极管显示输出信号;2.实验二:○1用VHDL语言设计实现一个4位二进制奇校验器,输入奇数个…1‟时,输出为…1‟,否则输出为…0‟,仿真验证其功能,并下载到实验板测试。

要求用拨码开关设定输入信号,发光二极管显示输出信号;○2用VHDL语言设计实现一个8421码转换为余3码的代码转换器,仿真验证其功能,并下载到实验板测试。

要求用拨码开关设定输入信号,发光二极管显示输出信号;○3用VHDL语言设计实现一个共阴极7段数码管译码器,仿真验证其功能,并下载到实验班测试。

要求用拨码开关设定输入信号,发光二极管显示输出信号;3.实验三:○1用VHDL语言设计实现一个分频系数为12,分频输出信号占空比为50%的分频器。

要求在Quartus Ⅱ平台上设计程序并仿真验证设计;○2用VHDL语言设计实现一个带异步复位的8421码十进制计数器,仿真验证其功能,并下载到实验板测试。

要求用拨码开关设定输入信号,发光二极管显示输出信号;○3将分频器、8421十进制计数器、数码管译码器3个电路进行连接并下载测试。

4.实验四:○1用VHDL语言设计并实现六个数码管串行扫描电路,要求同时显示0、1、2、3、4、5这6个不同的数字图形到6个数码管上,仿真验证其功能,并下载到实验板测试;(必做)○2用VHDL语言设计并实现六个数码管循环左滚动,时钟点亮6个数码管,坐出右进,状态为:012345→123450→234501→345012→450123→501234→012345;(选做)○3用VHDL语言设计并实现六个数码管向左滚动,用全灭的数码管填充右边,直至全部变灭,然后再一次从右边一个一个地点亮。

实验二-组合逻辑电路VHDL实现

实验二组合逻辑电路的VHDL实现一、实验目的掌握使用VHDL语言进行时序逻辑电路设计的方法。

二、实验设备及器件IBM PC机一台三、实验内容(1)用VHDL 语言设计一个D触发器,对程序进行编译和仿真,并记录仿真波形。

提示:D触发器的符号如右图所示,当时钟信号输入端CLK接收到上升沿信号时,输入端D的信号被传送到输出端Q输出,否则输出端Q维持原来的状态不变。

实验代码:D触发器LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164.ALL ;ENTITY DFF1 ISPORT (CLK : IN STD_LOGIC ;D : IN STD_LOGIC ;Q : OUT STD_LOGIC );END ;ARCHITECTURE bhv OF DFF1 ISSIGNAL Q1 : STD_LOGIC ; --类似于在芯片内部定义一个数据的暂存节点BEGINPROCESS (CLK)BEGINIF CLK'EVENT AND CLK = '1'THEN Q1 <= D ;END IF;Q <= Q1 ; --将内部的暂存数据向端口输出END PROCESS ;END bhv;(2)用VHDL语言设计一个十进制加法计数器,对程序进行编译和仿真,并记录仿真波形。

提示:十进制加法计数器的电路如下图所示,在时钟信号的驱动下,计数器进行累加,每次加1,其输出状态由0000变化到1001,加满回零。

当复位输入端reset为低电平时,计数器复位,输出状态回到0000。

十进制加法计数器电路图实验代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY jsq10 ISPORT(CLK,RESET:IN STD_LOGIC;Q:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0));END jsq10;ARCHITECTURE ONE OF jsq10 ISBEGINPROCESS(CLK,RESET)BEGINIF(RESET='0') THEN Q<="0000";ELSIF(CLK' EVENT AND CLK='1') THENQ<="0000";ELSEQ<=Q+1;END IF;END IF;END PROCESS;END ONE;(3)用VHDL语言设计一个电平锁存器,对程序进行编译和仿真,并记录仿真波形。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

汕头大学实验报告

学院: 工学院系: 电子专业年级成绩:

姓名: 学号组: 实验时间: 2010-04-10 指导教师签字:

_______________________________________________________________________________ 实验《二》:组合逻辑与时序逻辑电路的VHDL模型实验

一、实验目的:

1、掌握组合逻辑和时序逻辑电路的设计方法。

2、掌握组合逻辑电路的静态测试方法。

加深FPGA设计的过程,并比较原理图输入和

文本输入的优劣。

3、了解通用同步计数器,异步计数器的使用方法。

4、理解积分分频器的原理。

二、硬件要求

1、拨位开关。

2、FPGA主芯片:EP1K30QC208。

3、LED显示模块。

三、实验原理

译码器是输入数码和输出数码之间的对应关系,也就是说,“输入码和输出码之间的对应表”这应该算是设计译码器的必须条件。

译码器常用来做码和码之间的转换器,也常被用于地址总线或用作电路的控制线。

例如下面为常见的3×8译码器的真值表:

实验中可根据需要,为3×8译码器加入使能控制脚。

一般的分频器可获得的分频频率种类分布不均匀,积分分频,能比较好的解决这个问题。

1、分频结果=来源频率×N/(2ⁿ-1);

2、频率波形不均匀。

四、实验内容及步骤

本实验内容是完成38译码器和5/8分频器的设计,然后将3×8译码器的结果在实验箱上实现,5/8分频器则能正确仿真、显示,实验步骤如下:

1、编写3×8译码器的VHDL代码。

2、用Quartus II对其进行编译仿真。

3、在仿真确定无误后,选择芯片ACEX1K EP1K30QC208。

4、给芯片进行管脚绑定,在此进行编译。

5、根据自己绑定的管脚,在实验箱上对键盘接口、显示接口和FPGA之间进行正确连

线。

6、给目标板下载代码,在开关输入键值,观看实验结果。

7、编写5/8分频器的VHDL代码。

8、用Quartus II对其进行编译仿真。

9、使用WaveForm进行波形仿真。

五、实验结果与分析

1、对于3×8译码器,设置了3位拨动开关为输入,8位LED为输出。

时序仿真结果如下:

由图可知,A的三位为输入,Y的8位为输出。

符合三八译码器真值表。

经过验证,3位拨

动开关的不同组合输入,都会在LED上得到正确的输出。

验证了38译码器的功能。

2、5/8分频器

由图可知,实现了5/8分频器的功能,仿真成功。

六、程序代码

1、38译码器:

LIBRARY ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

ENTITY decode3_8 IS

port(a:in std_logic_vector(2 downto 0);

en:in std_logic;

y:out std_logic_vector(7 downto 0));

end decode3_8;

architecture behave of decode3_8 is

signal sel:std_logic_vector(3 downto 0);

begin

sel(0)<=en; sel(1)<=a(0);

sel(2)<=a(1);sel(3)<=a(2);

with sel select

y<="00000001"when"0001",

"00000010"when"0011",

"00000100"when"0101",

"00001000"when"0111",

"00010000"when"1001",

"00100000"when"1011",

"01000000"when"1101",

"10000000"when"1111",

"11111111"when others;

end behave;

2、5/8分频器

LIBRARY ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

ENTITY fp5_8 IS

port(cp:in std_logic;

op:out std_logic);

end fp5_8;

architecture behave of fp5_8 is

signal dly:std_logic;

signal qn:std_logic_vector(3 downto 0);

begin

process(cp)

begin

if cp'event and cp='1' then

dly<=qn(3);

qn<=qn+5;

end if;

end process;

op<=(qn(3) Xor dly) and (not cp);

end behave;

七、思考题

如果要设计7/8分频器,需要如果进行改动?

答:只需要把程序里的qn<=qn+5 改为qn<=qn+7就能实现7/8分频了。