计算机体系结构(深入理解计算机系统)样卷

计算机体系结构(深入理解计算机系统)样卷

19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

(b) The box below shows the format of a physical address. Indicate (by labeling the diagram) the fields that would be used to determine the following: PPO The physical page offset PPN The physical page number

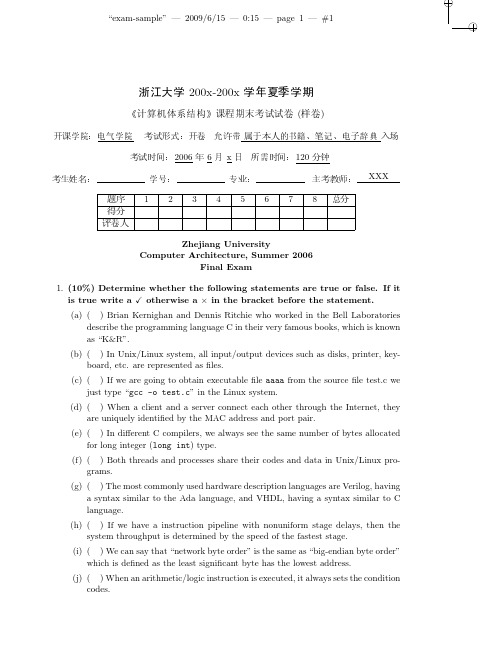

(a) ( ) Brian Kernighan and Dennis Ritchie who worked in the Bell Laboratories describe the programming language C in their very famous books, which is known as “K&R”.

(f) ( ) Both threads and processes share their codes and data in Unix/Linux programs.

(g) ( ) The most commonly used hardware description languages are Verilog, having a syntax similar to the Ada language, and VHDL, having a syntax similar to C language.

1

2

3

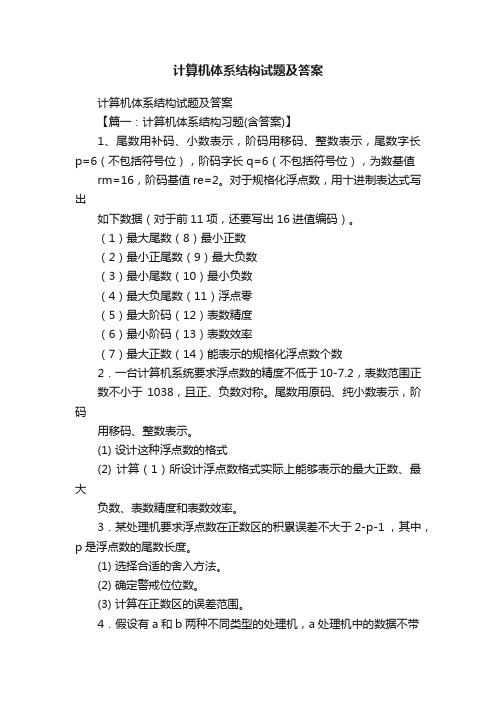

TLB Tag PPN Valid

03 B 1 07 6 0 28 3 1 01 F 0 31 0 1 12 3 0 07 E 1 0B 1 1 2A A 0 11 1 0 1F 8 1 07 5 1 07 3 1 3F F 0 10 D 0 32 0 0

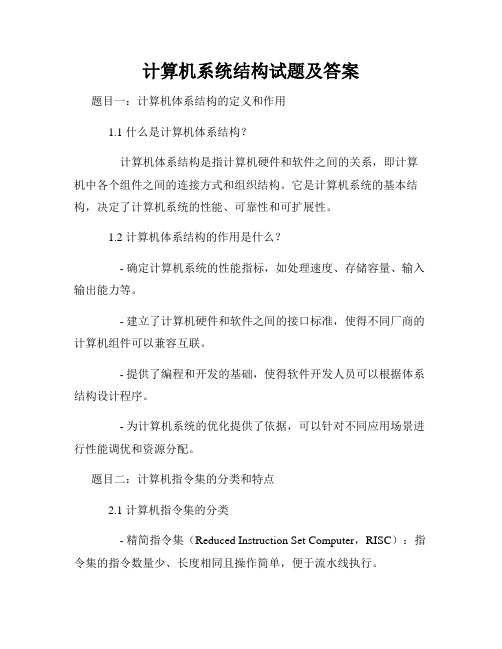

计算机系统结构试题及答案

计算机系统结构试题及答案题目一:计算机体系结构的定义和作用1.1 什么是计算机体系结构?计算机体系结构是指计算机硬件和软件之间的关系,即计算机中各个组件之间的连接方式和组织结构。

它是计算机系统的基本结构,决定了计算机系统的性能、可靠性和可扩展性。

1.2 计算机体系结构的作用是什么?- 确定计算机系统的性能指标,如处理速度、存储容量、输入输出能力等。

- 建立了计算机硬件和软件之间的接口标准,使得不同厂商的计算机组件可以兼容互联。

- 提供了编程和开发的基础,使得软件开发人员可以根据体系结构设计程序。

- 为计算机系统的优化提供了依据,可以针对不同应用场景进行性能调优和资源分配。

题目二:计算机指令集的分类和特点2.1 计算机指令集的分类- 精简指令集(Reduced Instruction Set Computer,RISC):指令集的指令数量少、长度相同且操作简单,便于流水线执行。

- 复杂指令集(Complex Instruction Set Computer,CISC):指令集的指令数量多、长度不一且操作复杂,提供了更高层次的指令和功能。

2.2 计算机指令集的特点- 性能折中:RISC指令集追求指令简单高效,减少指令周期;CISC指令集追求完成更复杂的功能,减少指令数量。

- 硬件与软件的关系:RISC指令集更注重硬件设计,减少指令执行的硬件复杂度;CISC指令集更注重编译器的优化,减少指令编写的软件复杂度。

- 执行流水线:RISC指令集易于流水线操作,指令之间无数据依赖,提高指令执行速度;CISC指令集指令复杂度高,难以流水线操作,容易产生数据依赖和冲突。

题目三:冯·诺伊曼体系结构和哈佛体系结构3.1 冯·诺伊曼体系结构(Von Neumann Architecture)冯·诺伊曼体系结构由冯·诺伊曼于1945年提出,是现代计算机体系结构的基础。

其特点如下:- 存储程序:指令和数据都存储在同一存储器中,通过地址寻址来访问。

深入理解计算机系统配套练习卷终审稿)

深入理解计算机系统配套练习卷文稿归稿存档编号:[KKUY-KKIO69-OTM243-OLUI129-G00I-FDQS58-《深入》题目李永伟第一章题目我们通常所说的“字节”由_____个二进制位构成。

A 2B 4C 6D 8微型计算机硬件系统中最核心的部位是__。

A 主板B. CPUC 内存处理器D I/O设备CPU中有一个程序计数器(又称指令计数器)。

它用于存储__。

A.保存将要提取的下一条指令的地址B.保存当前CPU所要访问的内存单元地址C.暂时存放ALU运算结果的信息D.保存当前正在执行的一条指令下列叙述中,正确的是A.CPU能直接读取硬盘上的数据B.CPU能直接存取内存储器C.CPU由存储器、运算器和控制器组成D.CPU主要用来存储程序和数据“32位微型计算机”中的32指的是()。

A.微机型号B.内存容量C.运算速度D.机器字长第二章题目求下列算是得值,结果用十六进制表示:0x503c + 64 =______A. 0x507cB.0x507bC. 0x506cD.0x506b将十进制数167用十六进制表示的结果是______A.0XB7B.0XA7C.0XB6D.0XA6位级运算:0x69 & 0x55 的结果是_______A.0X40B.0X41C.0X42D.0X43逻辑运算!!0x41的结果用十六进制表示为_____A.0X00B.0X41C.0X14D.0X01位移运算:对参数则x>>4(算术右移)的结果是______A.[01010000]B.[00001001]C.D.截断:假设一个4位数值(用十六进制数字0~F表示)截断到一个3位数值(用十六进制0~7表示),[1011]截断后的补码值是___A.-3B.3C.5D.-5浮点表示:数字5用浮点表示时的小数字段frac的解释为描述小数值f,则f=______A.1/2B.1/4C.1/8D.1/162.4.2 _25-8数字5用浮点表示,则指数部分E=_____A.1B.2C.3D.4数字5用浮点表示,则指数部分位表示为___A .2^ (K-1)+1B. 2^K+1C. 2^ (K-1)D. 2^K浮点运算:(3.14+1e10)-1e10 在计算机中的运算结果为A .3.14B .0C .1e10D .0.0第三章题目计算Imm(E b ,E i ,s)这种寻址模式所表示的有效地址:A .Imm + R[E b ]+R[E s ] *sB. Imm + R[E b ]+R[Es]C. Imm + R[E b ]D. Imm +R[E s ]下面这种寻址方式属于_____M[R[E b ]]A. 立即数寻址B. 寄存器寻址C. 绝对寻址D. 间接寻址假设初始值:%dh=CD,则执行下面一条指令后,%eax的值为多少?MOVB %DH ,%ALA. %eax= 987654CDB. %eax= CD765432C %eax= FFFFFFCDD. %eax= 000000CD假设初始值:%dh=CD,则执行下面一条指令后,%eax的值为多少?MOVSBL %DH ,%ALA. %eax= 987654CDB. %eax= CD765432C %eax= FFFFFFCDD. %eax= 000000CD假设初始值:%dh=CD,则执行下面一条指令后,%eax的值为多少?MOVZBL %DH ,%ALA. %eax= 987654CDB. %eax= CD765432C %eax= FFFFFFCDD. %eax= 000000CD假设寄存器%eax的值为x,%ecx的值为y,则指明下面汇编指令存储在寄存器%edx中的值Leal (%eax ,%ecx),%edxA. xB yC x + yD x –y假设寄存器%eax的值为x,%ecx的值为y,则指明下面汇编指令存储在寄存器%edx中的值Leal 9(%eax ,%ecx , 2),%edxA. x +y +2B 9*(x + y + 2)C 9 + x + y +2D 9 + x + 2y条件码CF表示______A 零标志B 符号标志C 溢出标志D进位标志条件码OF表示______A 零标志B 符号标志C 溢出标志D进位标志在奔腾4上运行,当分支行为模式非常容易预测时,我们的代码需要大约16个时钟周期,而当模式是随机时,大约需要31个时钟周期,则预测错误处罚大约是多少?A. 25B. 30C. 35D. 40第五章题目指针xp指向x,指针yp指向y,下面是一个交换两个值得过程:Viod swap (int *xp ,int *yp){*xp = *xp + *yp //x+y*yp = *xp - *yp //x+y-y=x*xp = *xp - *yp //x+y-x=y}考虑,当xp=yp时,xp处的值是多少A . xB. yC . 0D.不确定考虑下面函数:int min( int x , int y ) { return x < y x : y;}int max( int x , int y ){ return x < y y : x; }viod incr (int *xp ,int v) { *xp += v;}int square( int x ) { return x *x; }下面一个片段调用这些函数:for( i = min(x,y) ;i< max(x,y); incr(&i,1))t +=square(i) ;假设x等于10,y等于100.指出该片段中4个函数 min (),max(),incr(),square()每个被调用的次数一次为A.91 1 90 90B.1 91 90 90C.1 1 90 90D.90 1 90 90考虑下面函数:int min( int x , int y ) { return x < y x : y;}int max( int x , int y ){ return x < y y : x; }viod incr (int *xp ,int v) { *xp += v;}int square( int x ) { return x *x; }下面一个片段调用这些函数:for( i = max(x,y) -1;i >= min(x,y); incr(&i,-1))t +=square(i) ;假设x等于10,y等于100.指出该片段中4个函数 min (),max(),incr(),square()每个被调用的次数一次为A.91 1 90 90B.1 91 90 90C.1 1 90 90D.90 1 90 90考虑下面函数:int min( int x , int y ) { return x < y x : y;}int max( int x , int y ){ return x < y y : x; }viod incr (int *xp ,int v) { *xp += v;}int square( int x ) { return x *x; }下面一个片段调用这些函数:Int low = min(x,y);Int high = max(x,y);For(i= low;i<high;incr(&i,1)t +=square(i);假设x等于10,y等于100.指出该片段中4个函数 min (),max(),incr(),square()每个被调用的次数依次为A.91 1 90 90B.1 91 90 90C.1 1 90 90D.90 1 90 90假设某个函数有多个变种,这些变种保持函数的行为,又具有不同的性能特性,对于其中的三个变种,我们发现运行时间(以时钟周期为单位)可以用下面的函数近似的估计版本1:60+35n版本2:136+4n版本3:157+1.25n问题是当n=2时,哪个版本最快?A.1B.2C.3D.无法比较假设某个函数有多个变种,这些变种保持函数的行为,又具有不同的性能特性,对于其中的三个变种,我们发现运行时间(以时钟周期为单位)可以用下面的函数近似的估计版本1:60+35n版本2:136+4n版本3:157+1.25n问题是当n=5时,哪个版本最快?A.1B.2C.3D.无法比较假设某个函数有多个变种,这些变种保持函数的行为,又具有不同的性能特性,对于其中的三个变种,我们发现运行时间(以时钟周期为单位)可以用下面的函数近似的估计版本1:60+35n版本2:136+4n版本3:157+1.25n问题是当n=10时,哪个版本最快?A.1B.2C.3D.无法比较下面有一个函数:double poly( double a[] ,double x, int degree){long int i;double result = a[0];double xpwr =x;for(i=1 ; i<=degree; i++){result += a[i] *xpwr;xpwr =x *xpwr;}return result;}当degree=n,这段代码共执行多少次加法和多少次乘法?A.n nB.2n nC.n 2nD.2n 2n一名司机运送一车货物从A地到B地,总距离为2500公里。

(完整版)计算机系统结构考试题目及参考答案.doc

(完整版)计算机系统结构考试题目及参考答案.doc一:名词解释1:虚拟机:由软件实现的机器。

2:CPI :是衡量CPU 执行指令效率的重要标志,指执行每条指令所需的平均时钟周期数。

3:摩尔定律:当价格不变时,集成电路上可容纳的晶体管数目,约每隔18 个月便会增加一倍,性能也将提升一倍。

4:并发性:指两个或多个事件在同一时间间隔内发生的并行性。

5:程序局部性原理:是指程序在执行时呈现出局部性规律,即在一段时间内,整个程序的执行仅限于程序中的某一部分。

相应地,执行所访问的存储空间也局限于某个内存区域。

局部性原理又表现为:时间局部性和空间局部性。

6: CISC/RISC : CISC :即复杂指令系统计算机,指在系统中增加更多和复杂的指令,来提高操作系统效率的计算机。

RISC :即精简指令系统计算机,指在系统中选取使用一些频率最高的、长度固定的、格式种类少的简单指令的计算机。

7:计算机系统结构:指对机器语言计算机的软、硬件功能的分配和对界面的定义。

8:系列机:指先设计好一种系统结构,而后就按这种系统结构设计它的系统软件,按器件状况和硬件技术研究这种结构的各种实现方法,并按照速度、价格等不同要求,分别提供不同速度、不同配置的各档机器。

9:模拟:用机器语言程序解释实现程序移植的方法。

10:仿真:用微程序直接解释另一种机器的指令系统。

11:寻址方式:寻找操作数或指令的有效地址的方式。

12:替换算法:在存储体系中,当出现页面失效时或者主存的所有页面已经全部被占用而又出现页面失效时,按照某种算法来替换主存中某页。

[ 由于主存中的块比Cache 中的块多,所以当要从主存中调一个块到Cache 中时,会出现该块所映象到的一组(或一个)Cache 块已全部被占用的情况。

这时,需要被迫腾出其中的某一块,以接纳新调入的块。

]二:选择题1,直接执行微指令的是( C )A 汇编程序B 编译程序C 硬件D 微指令程序2,对汇编语言程序员不透明的是( C )A 程序计数器B 主存地址寄存器C 条件码寄存器D 指令寄存器3,最早的冯·诺依曼型计算机是以( B )为中心的A 运算器B 控制器C 存储器D I/O 设备4,计算机系统结构的角度的结构来看,机器语言程序员看到的机器属性是( C )A 计算机软件所要完成的功能B 计算机硬件的全部组成C 编程要用到的硬件组织D 计算机各部分硬件的实现5,不同系列计算机之间实现可移植性的途径,不包括( B )A 采用统一的高级语言B 采用统一的汇编语言C 模拟D 仿真6,利用时间重叠原理,实现并行处理的是( A )A 流水处理机B 多处理机C 阵列处理机D 集群系统7,多处理机实现的并行主要是(B)A 指令级并行B 任务级并行C 操作级并行D 操作步骤的级并行8 计算机系统结构不包括( B )A 信息保护B 存储速度C 数据表示D 机器工作状态9,不需要编址的数据存储空间( D )A CPU 通用寄存器B 主存储器C I/O 寄存器D 堆栈10, RISC 执行程序的速度比CISC 快的原因是( C )A RISC 指令系统中条数较少B 程序在 RISC 编译生成的目标程序较短C RISC 指令平均执行周期数较少D RISC 中只允许 LOAD 和 STORE 指令存储11,程序员在编写程序时,使用的访存地址是( B )A 主存地址B 逻辑地址C 物理地址D 有效地址12,虚拟存储器主要是为了( A )A 扩大存储器系统容量B 提高存储器系统速度C 扩大存储器系统容量和提高存储器系统速度D 便于程序的访存操作13,与全相联映像相比,组相联映像的优点是( B )A 目录表小B 块冲突概率低C 命中率高D 主存利用率高14,输入输出数据不经过CPU 内部寄存器的输入输出方式是( C )A 程序控制方式B 中断C DMA 方式D 上述三种方式15,在配置了通道的计算机系统中,用户程序需要输入输出时引起的中断是( A )A 访管中断B I/O 中断C 程序性中断D 外部中断16,当计算机系统通过执行通道程序,完成输入输出工作时,执行通道程序的是(B)A CPUB 通道C CPU 和通道D 指定的外设三:填空1,常见的计算机系统结构的分类法有两种:Flynn 分类法,冯氏分类法冯氏分类法是根据系统的最大并行度对计算机系统结构进行分类,大多数的位并行的单处理机属于字串位并的处理机方式2,由软件实现的机器称为:虚拟机3,在一个计算机系统中,低层机器的属性往往对高层机器的程序员是透明的。

计算机体系结构试题及答案

计算机体系结构试题及答案一、简答题1、请你简述冯·诺依曼结构的工作原理。

指出:它的结构特点是什么?冯·诺依曼结构是指计算机采用存储程序的工作方式,包含五个部分:算术逻辑单元(ALU)、控制单元(CU)、存储器(Memory)、输入/输出设备(I/O)、数据通路(Bus)。

它的工作原理是,程序从存储器中读取指令,指令分解成操作码和地址,控制单元根据操作码控制算术逻辑单元完成运算,然后将结果存储到存储器中或输出到I/O设备中。

其结构特点是:CPU与存储器采用同一总线,存储程序的方式,将数据和指令存储在同一存储器中,指令操作码和地址采用相同位数的二进制代码表示。

2、请你简述计算机的指令周期,以及每个阶段的作用。

指令周期是指计算机执行一条指令所经历的若干个阶段,一般包括取指令(Fetch)、指令译码(Decode)、执行指令(Execute)、存储结果(Write Back)四个阶段。

具体作用如下:取指令:从存储器中读取指令。

指令译码:对指令进行解析,确定指令的类型和操作数。

执行指令:根据指令类型和操作数进行相应的运算。

存储结果:将执行结果存储到指定的地址中,或者输出到I/O设备中。

3、请你简述计算机CPU的主要组成部分及其作用。

计算机CPU包含三个主要组成部分:算术逻辑单元(ALU)、控制单元(CU)、寄存器组。

具体作用如下:算术逻辑单元(ALU):执行算术和逻辑运算,例如加、减、乘、除、与、或、非等运算。

控制单元(CU):控制计算机的运行,包括指令译码、节拍发生、中断处理、目标跳转等操作。

寄存器组:存储一些特殊的数据,例如程序计数器(PC)、指令寄存器(IR)、通用寄存器等。

4、请你简述计算机的系统总线及其作用。

计算机的系统总线是一种用于传送信息的共享通信通路,分为三类:地址总线(Address Bus)、数据总线(Data Bus)、控制总线(Control Bus)。

其主要作用是实现各个组件之间的数据传输和控制信号传送,如CPU向存储器读写数据、I/O设备访问存储器等。

[整理版]计算机体系结构试题汇总

![[整理版]计算机体系结构试题汇总](https://img.taocdn.com/s3/m/dcb28ad90408763231126edb6f1aff00bed5704c.png)

计算机系统结构姓名:学号:一、简答题(每小题10分,共20分)1.简述使用物理地址进行DMA存在的问题,及其解决办法。

2.从目的、技术途径、组成、分工方式、工作方式等5个方面对同构型多处理机和异构型多处理机做一比较(列表)。

二、(60分)现有如下表达式:Y=a ×X其中:X和Y是两个有64个元素的32位的整数的向量,a为32位的整数。

假设在存储器中,X和Y的起始地址分别为1000和5000,a的起始地址为6000。

1.请写出实现该表达式的MIPS代码。

2.假设指令的平均执行时钟周期数为5,计算机的主频为500 MHz,请计算上述MIPS 代码(非流水化实现)的执行时间。

3.将上述MIPS代码在MIPS流水线上(有正常的定向路径、分支指令在译码段被解析出来)执行,请以最快执行方式调度该MIPS指令序列。

注意:可以改变操作数,但不能改变操作码和指令条数。

画出调度前和调度后的MIPS代码序列执行的流水线时空图,计算调度前和调度后的MIPS代码序列执行所需的时钟周期数,以及调度前后的MIPS流水线执行的加速比。

4.根据3的结果说明流水线相关对CPU性能的影响。

三、(20分)请分析I/O对于性能的影响有多大?假设:1.I/O操作按照页面方式进行,每页大小为16 KB,Cache块大小为64 B;且对应新页的地址不在Cache中;而CPU不访问新调入页面中的任何数据。

2.Cache中95%被替换的块将再次被读取,并引起一次失效;Cache使用写回方法,平均50%的块被修改过;I/O系统缓冲能够存储一个完整的Cache块。

3.访问或失效在所有Cache块中均匀分布;在CPU和I/O之间,没有其他访问Cache 的干扰;无I/O时,每1百万个时钟周期中,有15,000次失效;失效开销是30个时钟周期。

如果替换块被修改过,则再加上30个周期用于写回主存。

计算机平均每1百万个周期处理一页。

试题二计算机系统结构姓名:学号:一、名词解释(每题3分,共15分)1. Cache 2:1 经验规则3. 同构型多处理机5. 堆栈型机器2. 计算机体系结构4. 通道处理机二、填空(每空1分,共20分)1.设计I/O系统的三个标准是()、()和()。

深入理解计算机系统配套练习卷

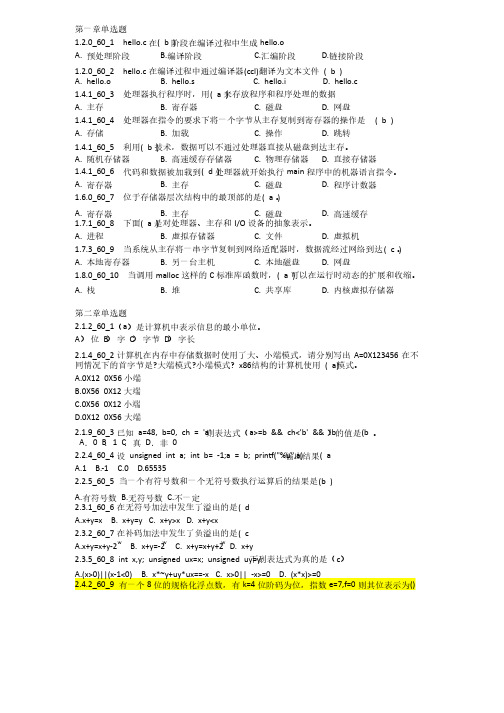

第一章单选题1.2.0_60_1 hello.c在( b )阶段在编译过程中生成hello.o A. 预处理阶段B.编译阶段C.汇编阶段D.链接阶段1.2.0_60_2 hello.c在编译过程中通过编译器(ccl)翻译为文本文件( b ) A. hello.o B. hello.s C. hello.i D. hello.c 1.4.1_60_3 处理器执行程序时,用( a )来存放程序和程序处理的数据A. 主存B. 寄存器C. 磁盘D. 网盘1.4.1_60_4 处理器在指令的要求下将一个字节从主存复制到寄存器的操作是( b ) A. 存储B. 加载C. 操作D. 跳转1.4.1_60_5 利用( b )技术,数据可以不通过处理器直接从磁盘到达主存。

A. 随机存储器B. 高速缓存存储器C. 物理存储器D. 直接存储器1.4.1_60_6 代码和数据被加载到( d )处理器就开始执行main程序中的机器语言指令。

A. 寄存器B. 主存C. 磁盘D. 程序计数器1.6.0_60_7 位于存储器层次结构中的最顶部的是( a )。

A. 寄存器B. 主存C. 磁盘D. 高速缓存1.7.1_60_8 下面( a )是对处理器、主存和I/O设备的抽象表示。

A. 进程B. 虚拟存储器C. 文件D. 虚拟机1.7.3_60_9 当系统从主存将一串字节复制到网络适配器时,数据流经过网络到达( c )。

A. 本地寄存器B. 另一台主机C. 本地磁盘D. 网盘1.8.0_60_10 当调用malloc这样的C标准库函数时,( a )可以在运行时动态的扩展和收缩。

A. 栈B. 堆C. 共享库D. 内核虚拟存储器第二章单选题2.1.2_60_1(a)是计算机中表示信息的最小单位。

A)位 B)字 C)字节 D)字长2.1.4_60_2计算机在内存中存储数据时使用了大、小端模式,请分别写出A=0X123456在不模式。

同情况下的首字节是大端模式?小端模式? x86结构的计算机使用( a)模式。

计算机体系结构试题及答案

计算机体系结构试题及答案计算机体系结构试题及答案【篇一:计算机体系结构习题(含答案)】1、尾数用补码、小数表示,阶码用移码、整数表示,尾数字长p=6(不包括符号位),阶码字长q=6(不包括符号位),为数基值rm=16,阶码基值re=2。

对于规格化浮点数,用十进制表达式写出如下数据(对于前11项,还要写出16进值编码)。

(1)最大尾数(8)最小正数(2)最小正尾数(9)最大负数(3)最小尾数(10)最小负数(4)最大负尾数(11)浮点零(5)最大阶码(12)表数精度(6)最小阶码(13)表数效率(7)最大正数(14)能表示的规格化浮点数个数2.一台计算机系统要求浮点数的精度不低于10-7.2,表数范围正数不小于1038,且正、负数对称。

尾数用原码、纯小数表示,阶码用移码、整数表示。

(1) 设计这种浮点数的格式(2) 计算(1)所设计浮点数格式实际上能够表示的最大正数、最大负数、表数精度和表数效率。

3.某处理机要求浮点数在正数区的积累误差不大于2-p-1 ,其中,p是浮点数的尾数长度。

(1) 选择合适的舍入方法。

(2) 确定警戒位位数。

(3) 计算在正数区的误差范围。

4.假设有a和b两种不同类型的处理机,a处理机中的数据不带标志符,其指令字长和数据字长均为32位。

b处理机的数据带有标志符,每个数据的字长增加至36位,其中有4位是标志符,它的指令数由最多256条减少到不到64条。

如果每执行一条指令平均要访问两个操作数,每个存放在存储器中的操作数平均要被访问8次。

对于一个由1000条指令组成的程序,分别计算这个程序在a处理机和b处理机中所占用的存储空间大小(包括指令和数据),从中得到什么启发?5.一台模型机共有7条指令,各指令的使用频率分别为35%,25%,20%,10%,5%,3%和2%,有8个通用数据寄存器,2个变址寄存器。

(1) 要求操作码的平均长度最短,请设计操作码的编码,并计算所设计操作码的平均长度。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

(d) Address translation

Parameter

VPN TLB Index TLB Tag TLB Hit? (Y/N) Page Fault? (Y/N) PPN

Value

(hex) (hex) (hex)

(d) ( ) When a client and a server connect each other through the Internet, they are uniquely identified by the MAC address and port pair.

(e) ( ) In different C compilers, we always see the same number of bytes allocated for long integer (long int) type.

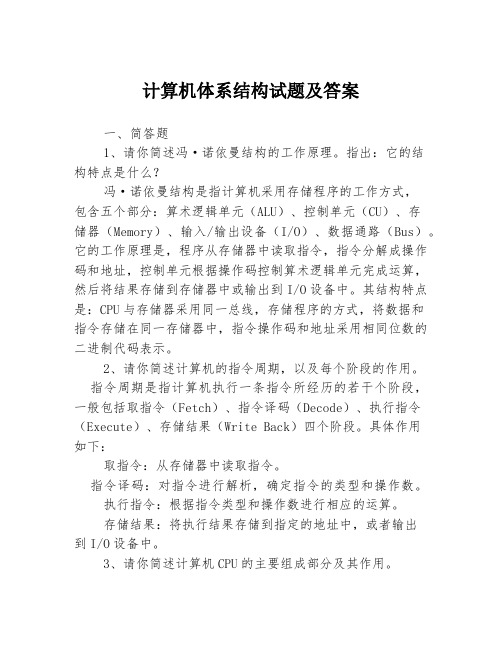

In the following tables, all numbers are given in hexadecimal. The contents of the TLB and the page table for the first 32 pages are as follows:

Index 0

.

(b) An approach is known as

whenever the memory perform

write-operations immediately after the cache updates its copy of a desired word

w.

(c) “CISC” is short for for

i “exam-sample” — 2009/6/15 — 0:15 — page 1 — #1

i i

úôÆ 200x-200x ÆcgGÆÏ

5OÅNX(¨6§Ï"ÁÁò (ò)

mƵ>íÆ Á/ªµmò #N áu<Ö7!)P!>f`; \|

Ámµ2006 c 6 x F ¤Imµ120 ©¨

i “exam-sample” — 2009/6/15 — 0:15 — page 3 — #3

i i

Computer Architecture Final Exam (Sample) (Page 3 of 8)

June. x, 2006

• The TLB is 4-way set associative with 16 total entries.

(a) The box below shows the format of a virtual address. Indicate (by labeling the diagram) the fields (if they exist) that would be used to determine the following: (If a field doesn’t exist, don’t draw it on the diagram.) VPO The virtual page offset VPN The virtual page number TLBI The TLB index TLBT The TLB tag

(f) ( ) Both threads and processes share their codes and data in Unix/Linux programs.

(g) ( ) The most commonly used hardware description languages are Verilog, having a syntax similar to the Ada language, and VHDL, having a syntax similar to C language.

(h) ( ) If we have a instruction pipeline with nonuniform stage delays, then the system throughput is determined by the speed of the fastest stage.

(i) ( ) We can say that “network byte order” is the same as “big-endian byte order” which is defined as the least significant byte has the lowest address.

, and “RISC” is short .

(d) In order to run myprog.c which begins with “include ‘‘csapp.h’’” in Linux

system, we should type a compiling command gcc -c myprog.c; and a linking

4(%eax) 9(%eax, %edx) 260(%ecx, %edx) 0xFC(, %ecx, 4) (%eax, %edx, 4)

Value

4. (20%) The following problem concerns the way virtual addresses are translated into physical addresses.

(j) ( ) When an arithmetic/logic instruction is executed, it always sets the condition codes.

i “exam-sample” — 2009/6/15 — 0:15 — page 2 — #2

i i

Computer Architecture Final Exam (Sample) (Page 2 of 8)

00 7 1 10 6 0 01 8 1 11 7 0 02 9 1 12 8 0 03 A 1 13 3 0 04 6 0 14 D 0 05 3 0 15 B 0 06 1 0 16 9 0 07 8 0 17 6 0 08 2 0 18 C 1 09 3 0 19 4 1 0A 1 1 1A F 0 0B 6 1 1B 2 1 0C A 1 1C 0 0 0D D 0 1D E 1 0E E 0 1E 5 1 0F D 1 1F 3 Valid

03 B 1 07 6 0 28 3 1 01 F 0 31 0 1 12 3 0 07 E 1 0B 1 1 2A A 0 11 1 0 1F 8 1 07 5 1 07 3 1 3F F 0 10 D 0 32 0 0

Page Table VPN PPN Valid VPN PPN Valid

(hex)

(e) Physical address format (one bit per box)

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

command

.

3. (8%) Assume the following values are stored at the indicated memory addresses and registers:

(a) Memory

Address Value 0x100 0xFF 0x104 0xAB 0x108 0x13 0x10C 0x11

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

For the given virtual addresses, indicate the TLB entry accessed and the physical address. Indicate whether the TLB misses and whether a page fault occurs.

i “exam-sample” — 2009/6/15 — 0:15 — page 4 — #4

i i

Computer Architecture Final Exam (Sample) (Page 4 of 8)

June. x, 2006

If there is a page fault, enter “-” for “PPN” and leave (e) blank. Virtual address: 7E37C (c) Virtual address format (one bit per box)

(b) ( ) In Unix/Linux system, all input/output devices such as disks, printer, keyboard, etc. are represented as files.

(c) ( ) If we are going to obtain executable file aaaa from the source file test.c we just type “gcc -o test.c” in the Linux system.

)6¶µ

ÆÒµ

;µ

̵ XXX

µKò©S< 1 2 3 4 5 6 7 8 o©

Zhejiang University Computer Architecture, Summer 2006

Final Exam

1. (10%) Determine whether the following statements are true or false. If it is true write a otherwise a × in the bracket before the statement.

June. x, 2006

2. (10%) Fill in the blanks.