四位序列检测器(完整版)

序列检测器原理

序列检测器原理

序列检测器是一种用来检测和识别输入序列中特定模式的设备或算法。

它能够根据事先给定的规则或模型对输入序列进行分析和判断,并输出相应的结果或响应。

序列检测器通常由以下几个组成部分构成:

1. 输入接口:用于接收输入序列的信号或数据。

2. 存储器:存储检测器的状态信息和输入序列的历史数据。

3. 状态机:用于根据输入序列的不同模式进行状态转换和控制。

4. 判决逻辑:根据当前状态和输入序列的特征,判断当前模式是否匹配。

5. 输出接口:根据判决的结果,输出相应的响应或结果。

序列检测器的工作原理如下:

1. 初始化:将序列检测器的状态设为初始状态,准备接收输入序列。

2. 接收输入:逐个接收输入序列的信号或数据。

3. 状态转换:根据当前状态和输入序列的特征,根据事先设定好的规则或模型进行状态转换。

4. 判决匹配:根据当前状态和输入序列的特征,判断当前模式是否匹配。

5. 输出结果:根据判决的结果,输出相应的响应或结果。

6. 循环操作:重复执行2-5步骤,直至所有的输入序列被处理完毕。

通过以上的工作原理,序列检测器可以有效地检测和识别输入序列中的特定模式。

它在许多应用中都有广泛的应用,如通信领域中的错误检测、模式识别等。

数字逻辑课程设计——111序列检测器

课程设计课程名称数字逻辑设计题目“1 1 1”序列检测器专业计算机科学与技术专业班级0706姓名孙禹指导教师巩晶2009 年06 月28 日课程设计任务书学生姓名孙禹学生专业班级计算机 0706指导教师巩晶学院名称计算机科学与技术学院一、题目:“1 1 1”序列检测器。

原始条件:使用D触发器( 74 LS 74 )、“与”门( 74 LS 08 )、“或”门( 74 LS 32 )、非门( 74 LS 04 ),设计“1 1 1”序列检测器。

二、要求完成设计的主要任务如下:1.能够运用数字逻辑的理论和方法,把时序逻辑电路设计和组合逻辑电路设计相结合,设计一个有实际应用的数字逻辑电路。

2.使用同步时序逻辑电路的设计方法,设计“1 1 1”序列检测器。

写出设计中的5个过程。

画出课程设计图。

3.根据74 LS 74、74 LS 08、74 LS 32、74 LS 04集成电路引脚号,在设计好的“1 1 1”序列检测器电路图中标上引脚号。

4.在试验设备上,使用74 LS 74、74 LS 08、74 LS 32、74 LS 04集成电路连接、调试和测试“1 1 1”序列检测器电路。

指导教师签名:2009 年6 月29 日系主任(责任教师)签名:2009 年月日一、实验目的:1、深入了解与掌握同步时序逻辑电路的设计过程;2、了解74LS74、74LS08、74LS32及74LS04芯片的功能;3、能够根据电路图连接好实物图,并实现其功能。

学会设计过程中的检验与完善。

二、实验内容描述:题目:“1 1 1”序列检测器。

原始条件:使用D触发器( 74 LS 74 )、“与”门( 74 LS 08 )、“或”门( 74 LS 32 )、非门( 74 LS 04 ),设计“1 1 1”序列检测器。

集成电路引脚图:D触发器( 74 LS 74 ) “与”门( 74 LS 08 )“或”门( 74 LS 32 ) 非门( 74 LS 04 )三、实验设计过程:第1步,画出原始状态图和状态表。

序列检测器实验报告

序列检测器设计实验内容:设计一个1110010序列检测器,即检测器检测到序列1110010时,输出为1,否则输出为0。

输入信号:一个时钟输入信号clk;一个输入端x以输入序列来检测;一个输入y用来选择是检测序列1110010或是检测自己输入的序列;一个输入k(7..0)用来输入想要检测器检测的序列;输出信号:一个7位输出信号q,用来输出正在检测的7位序列;一个1位输出信号unlk,当被检测序列符合时,输出unlk为1否则为0;中间信号:再定义两个7位的中间信号a和combination;执行操作:在上升的时钟沿时候,将从x输入的序列赋给7位a,在y等于1的情况下,令中间信号combination为1110010,否则,在y等于0的情况下,令中间信号combination为从k输入的七位长序列。

最后把a的值赋给q,如果a与combination输出unlk等于1否则等于0。

(1)序列检测器语言设计:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;USE IEEE.STD_LOGIC_ARITH.ALL;entity xulie2 isport (clk,x:in std_logic;y:in std_logic;k:in std_logic_vector(7 downto 1);unlk:out std_logic;q:out std_logic_vector(7 downto 1)); end xulie2;architecture art of xulie2 issignal a:std_logic_vector(7 downto 1);signal combination: std_logic_vector(7 downto 1);beginprocess(clk)beginif clk'event and clk='1' thena<=a(6 downto 1)&x;if y='1' thencombination<="1110010";else combination<=k;end if;end if;q<=a;end process;unlk<='1' when(a=combination) else '0';end art;序列检测器波形图:其中ENDTIME=10.0us GRIDSIZE=100.0ns波形图分析:如图,选择输入端y输入为1时,q对应着输出从x输入的7位序列,如果从x输入的待检测的7位序列为1110010时,unlk为1,否则为0,当选择输入端y输入为0时,q依旧对应着输出从x输入的待检测的当前7为序列,但是只有当从x输入的7为序列与从k输入的7位序列一致时,输出端unlk才为1,否则为0。

Verilog--序列检测器(采用移位寄存器实现)

Verilog--序列检测器(采⽤移位寄存器实现)Verilog --序列检测器(采⽤移位寄存器实现)序列检测器就是将⼀个指定序列从数字码流中识别出来。

本例中将设计⼀个“10010”序列的检测器。

设X为数字码流的输⼊,Z为检测出标记输出,⾼电平表⽰发现指定的序列10010.考虑码流为110010010000100101这篇博客,才发现原来使⽤移位寄存器可以如此简单,原理图如下:基本思路就是利⽤移位寄存器作为检测窗⼝,每进来⼀个数就跟⽬标序列进⾏⽐较,简单粗暴。

下⾯贴⼀下原帖的代码:module seqdet(input wire x,input wire clk,input wire rst,output wire z,output reg [4:0] q);//reg [4:0] q;assign z = (q == 5'b10010) ? 1'b1:1'b0;always @ (posedge clk,negedge rst)if(!rst)q <= 5'd0;elseq <= {q[3:0],x};endmoduletestbench:`timescale 1ns/1nsmodule seqdet_tb;localparam T =20;reg clk,rst;reg [23:0] data;wire z,x;wire [4:0] q;assign x = data[23];initialbeginclk =0;rst =1;#2 rst =0;#30 rst =1;data =20'b1100_1001_0000_1001_0100;#(T*1000) $stop;endalways #T clk = ~clk;always @ (posedge clk)#2 data = {data[22:0],data[23]};seqdet U1(.x(x),.z(z),.clk(clk),.q(q),.rst(rst));endmodule由于移位寄存器的赋值是在always块中,故⽽相对实际延迟了⼀个clk.由上⾯的⽅针结果可知,输出z相对x晚了⼀个时钟周期,因为由于移位寄存器的赋值是在always块中,故⽽相对实际延迟了⼀个clk.Note:跟⽤状态机实现的区别在于,使⽤移位寄存器需要存储所有的码字,因此如果序列长度为N,则该⽅法需要消耗的寄存器就是N个。

实验三_用状态机实现序列检测器的设计

实验三_用状态机实现序列检测器的设计引言:序列检测器是一类常用的电子设计电路,它在接收到特定的输入序列时,会产生特定的输出序列。

在许多应用场景中,如通信系统、数字信号处理和自动控制等领域,序列检测器都发挥着重要的作用。

本实验将利用状态机的概念,设计并实现一个简单的序列检测器。

一、序列检测器的设计原理序列检测器的设计原理基于状态机的思想。

状态机是一种抽象的计算模型,它由一组状态、一组输入和一组转移动作组成。

在序列检测器中,输入序列被连续地输入,状态也会根据输入进行不断变化。

当状态机检测到了预设的特定输入序列时,就会产生相应的输出序列。

二、序列检测器的设计步骤1.确定输入和输出序列:首先确定所需检测的输入序列和对应的输出序列,这将决定状态机的状态转移条件。

2.绘制状态转移图:根据输入和输出序列,绘制状态转移图,即用状态变量和状态转移条件表示状态转移关系。

3.设计状态机的状态转移表:根据状态转移图,将所有可能的状态转移关系整理为一个状态转移表。

4.实现状态机的代码逻辑:根据状态转移表,编写代码实现状态机的逻辑功能。

三、设计实例在本实验中,我们以一个简单示例为例,演示序列检测器的设计流程。

假设输入序列为0101,当检测到该输入序列时,输出序列为011.确定输入和输出序列:输入序列为0101,输出序列为012.绘制状态转移图:根据输入和输出序列,绘制状态转移图如下:0/00,S0,1/1/1说明:状态S0表示未检测到特定输入序列,状态S1表示检测到特定输入序列。

3.设计状态机的状态转移表:根据状态转移图,得到状态转移表如下:输当前状态,0,1S0,S0,S1S1,S0,S14.实现状态机的代码逻辑:根据状态转移表,编写代码实现状态机的逻辑功能,伪代码如下:if (当前状态 == S0)if (输入 == 0)当前状态=S0;输出=0;} else if (输入 == 1)当前状态=S1;输出=0;}} else if (当前状态 == S1)if (输入 == 0)当前状态=S0;输出=1;} else if (输入 == 1)当前状态=S1;输出=1;}}四、实验总结本实验利用状态机的思想,设计并实现了一个简单的序列检测器。

毕业设计(论文)-基于fpga的序列检测器的设计[管理资料]

![毕业设计(论文)-基于fpga的序列检测器的设计[管理资料]](https://img.taocdn.com/s3/m/0b99c5e176c66137ef06195d.png)

1 绪论序列检测是指将一个指定的序列从数字流中识别出来或在主串中查询相应子串,脉冲序列检测器广泛应用于现代数字通信系统中,在数字通信时,为了保证信息的可靠传输,一般需要在发送端加入固定的同步码组,而在接收端则需要检测该同步码组,保证信息的可靠接收。

接收端的同步码检测器就是用来检测同步码组的电路,中间用到的码型检测电路部分实际上就是一个脉冲序列信号检测器。

序列检测器广泛应用于数据通讯、雷达和遥测等领域。

传统的脉冲序列检测器,它的实现方法是把一个算法转化为一个实际数字逻辑电路的过程。

在这个过程中,我们所得到的结果大概一致,但是在具体设计方法和性价比上存在着一定的差异,存在电路设计复杂,体积大,抗干扰能力差以及设计困难、设计周期长等缺点。

而利用FPGA作为硬件电路,采用VHDL等硬件描述语言对硬件的功能进行编程,加快了系统的研发进程,采用数字化的控制方式,大幅度提高了逻辑控制的精确度,实时控制效果好,实践证明,FPGA芯片可以代替传统的复杂的电路,而且可以大比例地缩小了电路的硬件规模,提高了集成度,降低开发成本,提高系统的可靠性,为脉冲序列检测器电路的设计开辟了新的天地。

脉冲序列检测器在现代数字通信系统中发挥着重要的作用,通过中小规模的数字集成电路构成的传统脉冲序列检测器电路往往存在电路设计复杂、体积大、抗干扰能力差以及设计困难、设计周期长等缺点。

因此脉冲序列检测器电路的模块化、、重量减轻且功耗降低,同时可使系统的可靠性大大提高。

随着电子技术的发展,特别是专用集成电路(ASIC)设计技术的日趋完善,数字化的电子自动化设计(EDA)工具[1]给电子设计带来了巨大变革,尤其是硬件描述语言的出现,解决了传统电路原理图设计系统工程的诸多不便。

随着ASIC技术、EDA技术的不断完善和发展以及VHDL、HDL等通用性好、移植性强的硬件描述语言的普及,FPGA等可编程逻辑器件必将在现代数字应用系统中得到广泛的应用,发挥越来越重要的作用。

verilog设计一四位计数器

学院:信息技术学院班级:专业:电子信息科学与技术姓名:日期:学号:1、熟悉行为级语法;2、熟悉有限状态机设计一四位计数器,进行仿真,并检测输出结果;提示:在时钟上升沿,如果复位信号有效,则复位为0,如果复位信号无效,则计数器需要加一。

完成一个序列信号电路检测器,检测信号为10010,当检测到此序列时输出端口输出高电平,其余时间输出低电平。

提示:先画出状态转换图或写出状态转换表,根据状态表或者状态图完成代码的设计;编写测试模块对该功能模块进行仿真。

要求实验报告包括完整的状态转化图或者转化表。

序列信号电路检测器:module mian (z, x, clock, clear);output z;reg z;input clock, clear;input x;parameter s0 = 3'd0,s1 = 3'd1,s2 = 3'd2,s3 = 3'd3,s5 = 3'd5,s4 = 3'd4;reg [2:0] state;reg [2:0] next_state;always @(posedge clock) if(clear)state <= s0;elsestate <= next_state;always @(state)begincase(state)s0: show = 0;s1: show = 0;s2: show = 0;s3: show = 0;s4: show = 0;s5: show = 1; endcaseendalways @(x or state) begincase(state)s0: if(x == 0)next_state = s0;elsenext_state = s1;s1: if(x == 0)next_state = s2;elsenext_state = s1;s2: if(x == 0)next_state = s3;elsenext_state = s1;s3: if(x == 0)next_state = s0;elsenext_state = s4;s4: if(x == 0)next_state = s5;elsenext_state = s1;s5: if(x == 0)next_state = s0;elsenext_state = s1;endcaseendendmodulemodule stimulus_mv;wire z;reg x;reg clock, clear; mianMVP(z, x, clock, clear);initialbegin clock = 0;forever #5 clock = ~clock;endinitialbeginclear = 1;repeat(2)@(negedge clock);clear = 0;endinitialbegin#30 x = 1;#10 x = 0;#10 x = 0;#10 x = 1;#10 x = 0;endendmodule1.输出:四位计数器3.1功能块代码module counter(out, clock, clear);output out;input clock, clear;reg [3:0] out;always @(posedge clock or negedge clear) beginif(clear)out <= 4'd0;elseout <= out + 1;endendmodule3.2测试模块代码module counter_stimulus;reg clock, clear;wire [3:0] out;initial$monitor($time, "count = %b , clear = %b", out[3:0], clear); counter MVP(out, clock, clear);alwaysbeginclear = 1'b1;#15 clear = 1'b0;#200 clear = 1'b1;#50 clear = 1'b1;endinitialbeginclock = 1'b0;forever #5 clock = ~clock;endinitialbegin#400 $Finish;endendmodule4分析总结4.1遇到的问题及解决方法4.2实验心得及存在的问题。

序列检测器

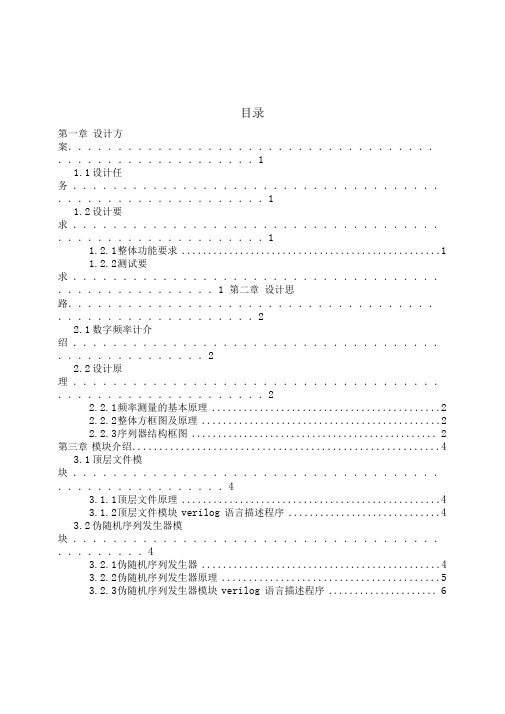

目录第一章设计方案.........................................................11.1设计任务..........................................................11.2设计要求..........................................................11.2.1整体功能要求.................................................11.2.2测试要求.....................................................1 第二章设计思路.........................................................22.1数字频率计介绍....................................................22.2设计原理..........................................................22.2.1频率测量的基本原理...........................................22.2.2整体方框图及原理.............................................22.2.3序列器结构框图...............................................2 第三章模块介绍.........................................................43.1顶层文件模块......................................................43.1.1顶层文件原理.................................................43.1.2顶层文件模块verilog 语言描述程序.............................43.2伪随机序列发生器模块..............................................43.2.1伪随机序列发生器.............................................43.2.2伪随机序列发生器原理.........................................53.2.3伪随机序列发生器模块verilog 语言描述程序.....................63.3序列检测器模块....................................................73.3.1序列检测器原理...............................................73.3.2序列检测器模块verilog 语言描述程序...........................7 第四章序列检测器的实现.................................................84.1序列检测器的verilog 语言程序描述及仿真............................84.1.1序列检测器的verilog 语言程序描述.............................84.1.2序列检测器的波形仿真.........................................94.2设计中遇到的问题与解决方法.......................................104.2.1设计中遇到的问题.............................................104.2.2解决方法.....................................................10 第五章设计小结.........................................................115.1心得体会..........................................................11第一章设计方案1.1设计任务在掌握常用数字电路功能和原理的基础上,根据 EDA 技术课程所学知识,利用硬件描述语言 Verilog HDL、EDA软件Quartus II 和硬件平台 Cyclone/Cyclone II FPGA 进行电路系统的设计。