SPI串行总线接口的Verilog实现

SPI_I2S

应用笔记487利用MAX II CPLD 实现SPI 至I 2S 的接口引言本应用笔记介绍怎样使用Altera ®MAX ®II CPLD 来实现协议转换,通过串行外设接口(SPI)控制inter-IC 声音(I 2S)总线上的音频设备数据流。

I 2S 和SPI 接口I 2S 是3线半双工串行接口,常用于通过被称为I 2S 总线的3线总线来连接系统中的音频设备。

I 2S 设备和总线使用3条线:串行数据(SDA ),承载了对应于每一个音频通道的两路时分复用音频数据;串行时钟(SCK )和字选择(WS ),控制数字音频数据在I 2S 总线上不同设备之间的传输。

I 2S 系统能够处理和串行时钟分开的串行音频数据,以消除抖动。

SPI 是4线全双工串行接口,常用于连接系统内部和外部的系统处理器(主机)和外设(从机)。

SPI 利用单独的数据输出信号线(主机输出从机输入,即MOSI )和数据输入信号线(主机输入从机输出,即MISO ) 以及时钟(SCLK )和从机选择或者片选信号(CS )来进行通信。

本设计支持SPI 接口主机对其他设备的数据流控制,包括A/D 转换器、数字信号处理器、数字滤波器、音频处理器、PC 多媒体音频转换器等 I 2S 总线设备。

有的嵌入式系统并没有为音频数据通信提供I 2S 接口,但是有SPI 接口。

您可以在和这些接口相似的环境中有效地使用本设计。

利用MAX IICPLD 实现SPI 至I 2S 的接口SPI 主机的桥接接口是SPI 从机,它有四条信号线(CS , SCLK , MISO 和MOSI )。

I 2S 总线一侧接口是I 2S 主机,它有三条信号线(I2S_ SCK , I2S_SDA 和I2S_WS )。

CLK 是主机时钟,位于I 2S 主机外部。

图1所示为采用 MAX II CPLD 来实现SPI 至I 2S 接口。

2007年12月,1.0版图1.利用MAX II CPLD实现SPI至I2S接口本设计提供协议转换功能,通过SPI 接口(更常用的4线串行接口,用于连接串行外设接口和微处理器或者主机)来控制I2S 总线(带宽相对较窄的协议,用于连接系统中的数字音频设备)上音频设备的数据流。

基于LabVIEW的SPI串行总线接口的实现

基于LabVIEW的SPI串行总线接口的实现作者:赵骁周斌赵华来源:《现代电子技术》2014年第14期摘要:为了便于具有SPI串行总线接口设备的调试,使用美国国家仪器公司(NI)的标准模块化设备模拟SPI串行总线接口信号;采用图形化编程语言LabVIEW得到数字波形格式的SPI信号,并设计程序对此格式的信号进行解析,利用NI公司的硬件设备实现该信号的输入与输出。

经过实验测试,输出SPI接口信号的频率范围是0.5 Hz~500 kHz,输入的频率范围是0.5 Hz~900 kHz,误差小于10 ns,该方法可以用于SPI串行总线接口设备的调试中。

关键词: SPI接口;串行总线接口; LabVIEW;测试中图分类号: TN710⁃34; TP319 文献标识码: A 文章编号: 1004⁃373X(2014)14⁃0138⁃04Implementation of SPI serial bus interface based on LabVIEWZHAO Xiao1, ZHOU Bin2, ZHAO Hua2(1. Nanjing University of Aeronautics and Astronautics, Nanjing 210016, China; 2. National Space Science Center, Beijing 100190, China)Abstract: In order to debug the device with SPI serial bus interface conveniently, the standard modular device of National Instruments (NI) was used to simulate SPI serial bus interface signals, LabVIEW was used to get the SPI signals in digital waveform format, a program was designed to analysis these signals, and the hardware equipments of NI was utilized to realize the input and output of these signals. The experimental testing result shows that the frequency range of the output signal from the SPI interface is 0.5 Hz to 500 kHz, the input frequency range is 0.5 Hz to 900 kHz, the error is less than 10 ns. This method can be used to debug SPI serial bus interface device.Keywords: SPI interface; serial bus interface; LabVIEW; testingSPI(Serial Peripheral Interface)[1]总线技术是Motorola公司提出的一种同步串行外设接口,是接线简单、通信效率高、全双工、同步的通信总线。

[FPGA][Verilog][SPI]简单的读写SPI接口EEPROM-93C46程序

![[FPGA][Verilog][SPI]简单的读写SPI接口EEPROM-93C46程序](https://img.taocdn.com/s3/m/1221e485ec3a87c24028c428.png)

Write19: begin mo <= 0; cs <= 0; end

Read0: cs <= 0; Read1://110+add(7bit) begin cs <= 1; mo <= 1; end Read2: mo <= 1; Read3: mo <= 0;//110 Read4: mo <= 0; Read5: mo <= 1; Read6: mo <= 1; Read7: mo <= 1; Read8: mo <= 1; Read9: mo <= 1; Read10: mo <= 1; Read11: begin mo <= 0; led[7] <= mi; end Read12: led[7] <= mi; Read13: led[6] <= mi; Read14: led[5] <= mi; Read15:

从开始读数据手册,到研究时序,到编写 Verilog 程序,到仿真调试时序,整整 花了有 3-4 天时间。 最后时序已经完全正确, 却读不出任何数据,经过一个晚上的排查才发现是开发 板上的 DI DO SK CS 标号标错了,泪奔~~ 本来我想写一个完整的 SPI 接口出来,想了几天都没有头绪,最后还是写了一个 最简单的写数据读数据的小程序,如果做成接口也勉强可以用。 程序的功能很简单,往地址 0111111 的位置写了 00001111 的数据,地址都还没 有做成接口,固定在程序里面的。 具体用了一个状态机共 53 个状态,每一个状态都是一个 SCK 信号的处理,当然 有分为三个大状态,分别为 ENWR、WRITE、READ 93C46 要首先写 ENWR 信号才能写入数据,具体还得研究数据手册 通过这次 93C46 和上次写 18B20 的经历, 我感觉到数据手册的确是相当的重要的, 需要仔细推敲,分析每一个时序图!下次要做 I2C 接口的 24C02,1、2、3 线就 都学过拉。 当然作为初学者程序是写的那是超级的烂,欢迎拍砖

CRC校验在SPI接口设计中的实现

CRC校验在SPI接口设计中的实现强小燕;史兴强;刘梦影【摘要】串行外设接口(SPI,serial peripheral interface)以其高速的传输性能和灵活简单的配置,广泛应用于扩展外设及其数据交换.由于串行通信传输的不确定性以及干扰等原因,通信经常会出现异常情况.为提高SPI通信传输的可靠性,在SPI接口设计中增加循环冗余校验(CRC,cyclic Redundancy Check)功能.运用硬件描述语言Verilog HDL设计并实现了具有CRC校验功能的SPI接口.仿真结果表明,该SPI 接口不仅可以高速高效地工作于多种工作模式,且CRC校验功能能够保证通信传输的可靠性.【期刊名称】《电子与封装》【年(卷),期】2018(018)011【总页数】6页(P30-35)【关键词】CRC;串行;SPI;可靠性【作者】强小燕;史兴强;刘梦影【作者单位】中科芯集成电路股份有限公司,江苏无锡214072;中科芯集成电路股份有限公司,江苏无锡214072;中科芯集成电路股份有限公司,江苏无锡214072【正文语种】中文【中图分类】TN4021 引言为适应复杂的通信环境和高速的通信速率要求,能够快速可靠地完成大量数据交换的数据总线是极其重要的,因此设计一个高效可靠的通信接口就十分重要。

SPI接口技术是一种高速高效的串行接口技术[1],其接口连线简单、配置灵活、传输效率高[2],广泛应用于扩展外设和进行数据交换[3]。

随机噪声和干扰等因素存在于串行通信传输中,可能导致数据传输错误。

通过采用硬件措施进而加强通信传输的可靠性可检测这类错误,或在设计中增加校验功能,通过该方法检测数据在传输过程中是否发生错误[4]。

CRC是由分组线性码的分支而来[5],该算法简单易实现,能够同时检测和抗干扰,是一种高效可靠的差错校验法[6]。

该方法导致数据的冗余量增加,发送端不仅发送数据,最后还需将CRC码发送给接收端。

SPI协议的Verilog 实现

// //接收数据存入 out_data

6

begin case(addr) 1'b0: begin in_buffer = in_data; busy = 1'b1; end 转入工作状态 1'b1: begin busy = 1'b0;end endcase end end else begin if(cs) begin clkcount = clkcount + 1'b1; if(clkcount >= 8'b10) // 控制 SCK 周期 begin clkcount = 0; if((count % 2) == 0) //待发数据存入缓存区,

DataPort[5]-DataPort[0] : busy、sdo 、addr、cs、wr、rd DataPort[21]-DataPort[14] :待发送 8bit 数据 DataPort[13]-DataPort[6] : 接收的 8bit 数据

3

� 总结

完成时间:12.4--12.12 前期:该阶段主要是熟悉 SPI 工作原理,进一步掌握和认识 SPI 通信协议。Chipscore 的使 用之前未曾接触, 在这一阶段, 我先通过简单编程结合开发板抓取数据进行分析达到 对其的基本掌握。 中期:在熟悉 SPI 的工作原理之后,开始尝试编写代码。写了两三次代码,效果均不理想, 很多问题在编写代码的时候没有考虑清楚,导致到了仿真阶段结果与预期有所差距, 且代码冗长复杂。参考了一些资料,效果也不是很好,特别是数据传输暂停部分, 很 多都省略了。不过借鉴别人写的代码也让我收获了不少编写的经验,有些情况下, 运 用不同的逻辑思维可以让代码更简洁、 更具有健壮性。 当然期间也遇到了一些自己无 法解决的问题,非常感谢福星学长耐心的指导,让我学到了不少知识和经验。 后期:该阶段主要是对代码进行再修改、波形仿真以及抓数据调试。 问题及分析: 小问题遇到不少,不过大多都通过 error 的提示,或者上网搜索,找到了问题的原因, 并予以解决。也有软件上的原因,比如:第一次装 ISE 的时候可能没有安装好,上板调试的 时候,cable 不能识别。经过测试分析发现 ISE 里的 drive 没有装上。考虑到这样一个问题的 出现可能还会附带有一些软件上的漏洞,重装了一遍 ISE,问题解决。 使用 chipscope 的时候,芯片配置不对连接失败,查阅该电路板的资料,重新配置,问 题解决。在 chipscope 里面有些触发信号找不到,经分析是被优化了,通过简单修改代码避 免它被优化后,问题解决。运行 chipscope 后发现 waveform 始终没反应,经过一番分析, 认 为时钟线的引脚配置有问题,重换一个时钟信号线 I/O 引脚,问题解决。解决后发现抓取的 波形没有明显的高低跳变,经分析可能是参考时钟选取不对,重选后问题解决。

FPGA和单片机串行通信接口的实现

FPGA和单片机串行通信接口的实现FPGA(Field-Programmable Gate Array)和单片机(Microcontroller)是两种常用的数字电子设备,它们在串行通信接口方面有不同的实现方式。

首先,我们需要了解串行通信是一种将数据以位的形式逐个传输的通信方式。

常见的串行通信协议包括UART(Universal Asynchronous Receiver/Transmitter)、SPI(Serial Peripheral Interface)和I2C (Inter-Integrated Circuit)等。

对于FPGA和单片机之间的串行通信,我们可以基于以下几种方式进行实现:1. UART:UART是一种常见的串行通信协议,可以实现全双工的通信。

在FPGA和单片机之间建立UART通信,需要在FPGA中实现UART模块,并将其与单片机的UART接口连接。

在FPGA中,我们可以使用硬件语言(如Verilog或VHDL)来实现UART模块,该模块负责将FPGA内部的数据通过UART协议进行封装和解封装。

单片机与FPGA之间通过TX(发送)和RX (接收)引脚建立连接。

单片机可以通过串口发送数据给FPGA,FPGA接收到数据后进行处理,然后再通过串口将处理后的数据发送给单片机。

2.SPI:SPI是一种用于片上外设之间通信的串行通信协议,常用于FPGA与外部设备(例如传感器、显示器等)之间的通信。

在FPGA和单片机之间建立SPI通信,需要在FPGA中实现SPI控制器,并将其与单片机的SPI接口连接。

FPGA通过把数据写入SPI发送缓冲区或从SPI接收缓冲区读取数据来实现与单片机的通信。

单片机通过控制SPI接口的时钟、数据和使能信号来与FPGA进行数据传输。

3.I2C:I2C是一种双线制串行总线,常用于连接多个设备的系统,例如FPGA、单片机和其他外部设备之间的通信。

在FPGA和单片机之间建立I2C通信,需要在FPGA中实现I2C控制器,并将其与单片机的I2C接口连接。

基于UVM的SPI接口IP核的设计与验证

基于UVM的SPI接口IP核的设计与验证SPI(Serial Peripheral Interface)是一种常用的串行外设接口,广泛应用于数字系统中。

为了实现SPI接口的功能,需要设计和验证相应的IP核。

本文将介绍基于UVM(Universal Verification Methodology)的SPI接口IP核的设计与验证。

首先,我们需要了解SPI接口的基本原理。

SPI接口由一个主设备和一个或多个从设备组成。

主设备通过时钟信号控制数据的传输,同时使用片选信号选择从设备。

主设备通过一个数据线发送数据,并通过另一个数据线接收从设备返回的数据。

SPI接口的主要特点是数据传输速度快、灵活性高,适用于多种外设连接。

在设计SPI接口的IP核时,我们需要考虑以下几个方面。

首先,IP核需要支持不同的SPI模式,包括不同的时钟极性和相位设置。

其次,IP核需要能够处理不同的数据位宽,并支持全双工和半双工传输模式。

此外,IP核还需要支持多个从设备的片选信号,并能够处理中断请求。

为了验证SPI接口的IP核,我们采用了UVM方法。

UVM 是一种基于SystemVerilog的验证方法学,提供了一套丰富的验证库和方法。

我们可以利用UVM提供的功能,建立一个完整的验证环境,并编写验证测试用例。

在验证SPI接口的IP核时,我们需要分别验证其主设备和从设备的功能。

对于主设备,我们可以编写测试用例来验证其发送数据的正确性、时序和时钟控制的准确性。

对于从设备,我们可以编写测试用例来验证其接收数据的正确性和片选信号的选择准确性。

通过使用UVM方法,我们可以模拟SPI接口的IP核,并在仿真平台上验证其功能和性能。

通过编写一系列的测试用例,我们可以确保IP核在不同的工作场景下都能正常工作。

综上所述,本文介绍了基于UVM的SPI接口IP核的设计与验证。

通过设计一个支持多种模式、不同数据位宽和多个从设备的IP核,并利用UVM方法进行验证,我们可以确保IP核在实际应用中的正确性和可靠性。

【CPLD+Verilog】CPLD实现SPI接口

CPLD 实现SPI 接口1 实现原理CPLD 实现SPI 接口模块,通过对寄存器的操作,实现SPI 接口功能,对外部SPI 设备进行访问。

CPLD 内部SPI 模块逻辑框图如下所示。

CLK_DIVRX_SHIFT_REGSTATUS LOGICspi_clkspi_cs spi_dospi_tx_data_we_pulsereset_n spi_tx_data spi_rx_data spi_clk_div spi_rx_data_rd_pulsespi_dispi_tx_data_we_busy spi_rx_data_rd_ready spi_data_tx_we_overflow spi_data_rx_rd_nop spi_data_rx_rd_overtime cpld_clkCONTROL LOGICCOUNT LOGIC通过对主时钟分频,得到的SPI 接口时钟,其分频值可通过spi_clk_div 值设定,最小为6分频,当设置分频值低于6分频时,默认6分频。

SPI 接口的片选信号spi_cs 在写数据传输寄存器spi_tx_data 时,通过自动产生写脉冲spi_tx_data_we_pulse ,逻辑综合生成。

spi_rx_data_rd_pulse 在读取接收数据spi_rx_data 的数据时自动产生。

spi_di 和spi_do 分别由数据移位寄存器通过数据移位产生和接收。

spi_clk 由内部分频时钟和传输状态逻辑综合输出,在有数据时输出,无数据时保持高电平。

状态逻辑spi_tx_data_we_busy 信号分别表示数据正在传输,无法写入spi_tx_data 寄存器; spi_rx_data_rd_ready 信号表示数据接收完成,可读取spi_rx_data 寄存器的值。

错误状态逻辑spi_data_tx_we_overflow 信号表示在spi_tx_data 寄存器中写入了待传输值后,还未传输就又写入新的传输数据,表示写数据溢出。

基于APB总线的SPI接口设计与实现

基于APB总线的SPI接口设计与实现刘梦影;王芬芬【摘要】基于高性能外设总线(APB,Advance Peripheral Bus)接口,设计了一个支持多样化工作模式和通信格式的SPI接口.为实现高速通信,该SPI采用一个复用移位寄存器.用硬件描述语言Verilog HDL设计并实现了SPI模块.仿真结果表明,该SPI接口能够支持多种工作模式和通信方式,同时确保数据传输有效.【期刊名称】《电子与封装》【年(卷),期】2018(018)005【总页数】5页(P28-32)【关键词】SPI;APB总线;多样化;复用【作者】刘梦影;王芬芬【作者单位】中国电子科技集团公司第五十八研究所,江苏无锡214072;中国电子科技集团公司第五十八研究所,江苏无锡214072【正文语种】中文【中图分类】TN4021 引言现如今,数字技术高速发展,许多芯片或作为核心器件用于数据交换,具有承上启下的数据交换枢纽作用,或用于集成电路之间进行数据存储和显示等[1]。

为适应通信环境和高速的通信速率要求,通常使用多个微处理器完成信号的收发处理,因此需要一种高效的数据总线快速有效地完成它们之间大量的数据交换。

因此,设计一个高效快速的通信接口是至关重要的[2]。

串行外围设备接口SPI总线技术是Motorola公司推出的一种微处理器、微控制器以及外设间的串行数据接口标准[3],主要用于扩展外设和进行数据交换[4]。

SPI接口连线简单,配置灵活,传输效率高[5],因此应用广泛,很多器件如E2PROM、FLASH、实时时钟、A/D转换器等都用到了SPI接口[6]。

郭艾华[7]设计了一种可灵活配置为主/从设备,设置传输速率,支持DMA功能并适用于多种时钟模式的SPI协议IP核,但从机片选信号只可由主机输出,存在一定的局限性。

李琦、贺明等[8]以微处理器S3C2440和嵌入式Linux操作系统组成的嵌入式系统作为开发平台,设计了一款基于ARM嵌入式系统的SPI驱动程序,该设计存在两组8位移位寄存器,支持传输8位数据,但未有效地运用硬件资源。

SPI总线接口的verilog的实现

十二SPI总线接口的verilog的实现1.实验目的项目中使用的许多器件需要SPI接口进行配置,比如PLL:ADF4350,AD:AD9627,VGA:AD8372等,本实验根据SPI协议,编写了一个简单的SPI读写程序,可以进行32位数据的读写,可以设置SPI SCLK相对于主时钟的分频比。

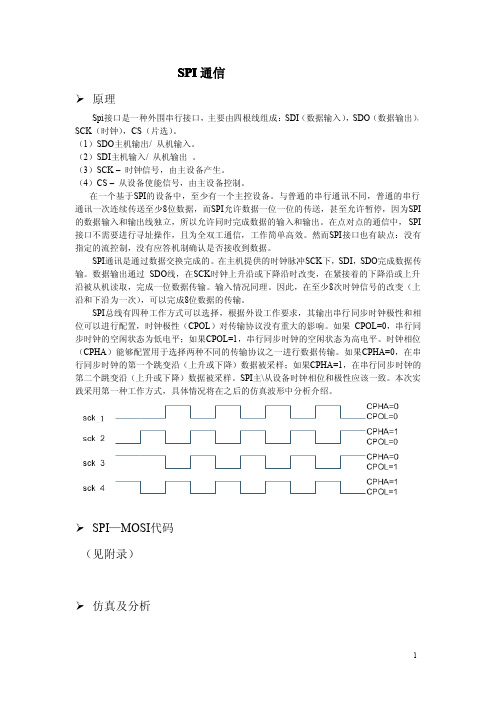

2.实验原理SPI总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息。

外围设置FLASHRAM、网络控制器、LCD显示驱动器、A/D转换器和MCU等。

SPI总线系统可直接与各个厂家生产的多种标准外围器件直接接口,该接口一般使用4条线:串行时钟线(SCK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOST和低电平有效的从机选择线SS(有的SPI接口芯片带有中断信号线INT、有的SPI接口芯片没有主机输出/从机输入数据线MOSI)。

SPI的通信原理很简单,它以主从方式工作,这种模式通常有一个主设备和一个或多个从设备,需要至少4根线,事实上3根也可以(单向传输时)。

也是所有基于SPI的设备共有的,它们是SDI(数据输入),SDO(数据输出),SCK(时钟),CS(片选)。

(1)MOSI –主设备数据输出,从设备数据输入(2)MISO –主设备数据输入,从设备数据输出(3)SCLK –时钟信号,由主设备产生(4)CS –从设备使能信号,由主设备控制其中CS是控制芯片是否被选中的,也就是说只有片选信号为预先规定的使能信号时(高电位或低电位),对此芯片的操作才有效。

这就允许在同一总线上连接多个SPI设备成为可能。

接下来就是负责通讯的3根线了。

通讯是通过数据交换完成的,这里先要知道SPI是串行通讯协议,也就是说数据是一位一位的传输的。

这就是SCK时钟线存在的原因,由SCK 提供时钟脉冲,SDI,SDO则基于此脉冲完成数据传输。

数据输出通过 SDO线,数据在时钟上升沿或下降沿时改变,在紧接着的下降沿或上升沿被读取。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SPI串行总线接口的Verilog实现摘要:集成电路设计越来越向系统级的方向发展,并且越来越强调模块化的设计。

SPI(Serial Peripheral Bus)总线是Motorola公司提出的一个同步串行外设接口,容许CPU 与各种外围接口器件以串行方式进行通信、交换信息。

本文简述了SPI总线的特点,介绍了其4条信号线,SPI串行总线接口的典型应用。

重点描述了SPI串行总线接口在一款802.11b芯片中的位置,及该接口作为基带和射频的通讯接口所完成的功能,并给出了用硬件描述语言Verilog HDL 实现该接口的部分程序。

该实现已经在Modelsim 中完成了仿真, 并经过了FPGA 验证, 最后给出了仿真和验证的结果。

在SOC设计中,利用EDA 工具设计芯片实现系统功能已经成为支撑电子设计的通用平台.并逐步向支持系统级的设计方向发展。

而且,在设计过程中,越来越强调模块化设计。

SPI总线是Motorola公司提出的一个同步串行外设接口,具有接口线少、通讯效率高等特点。

本文给出的是利用Verilog HDL实现的SPI总线模块,该模块是802.11b无线局域网芯片中一个子模块,该模块完成了芯片中基带(base band)与RF的通讯工作.1 SPI总线接口概述SPI(Serial Parallel Bus)总线是Motorola公司提出的一个同步串行外设接口,允许CPU 与各种外围接口器件(包括模/数转换器、数/模转换器、液晶显示驱动器等)以串行方式进行通信、交换信息。

他使用4条线:串行时钟线(SCK)、主机输入/从机输出线(MISO)、主机输出/从机输入线(MOSI)、低电平有效的使能信号线(CS)。

这样,仅需3~4根数据线和控制线即可扩展具有SPI接口的各种I/O 器件其典型结构如图1所示。

SPI总线具有以下特点:(1)连线较少,简化电路设计。

并行总线扩展方法通常需要8根数据线、8~16根地址线、2~3根控制线。

而这种设计,仅需4根数据和控制线即可完成并行扩展所实现的功能。

(2)器件统一编址,并与系统地址无关,操作SPI独立性好。

(3)器件操作遵循统一的规范,使系统软硬件具有良好的通用性。

2 SPI总线接口的设计与实现该模块是802.1lb无线局域网芯片中的一子模块,其在芯片中的位置如图2所示。

其中base band(基带)为SPI的主控器(master),RF(射频)为SPI的受控器(sl ave)。

SPI interface作为baseband与RF的通讯接口,主要完成以下工作:(1)将从base band接收到的16位的并行数据,转换为RF所能接收的串行数据,并将该数据根据SPI协议送给RF。

(2)产生RF所需的时钟信号SCLK,使能信号CSB。

(3)接收从RF传回的串行数据,并将其转换为并行数据。

(4)将base band发送的数据,与RF返回的数据进行比较,并把比较结果传给base band。

下面给出用Verilog HDL语言实现前两项功能的关键程序,相关变量的声明在此略去。

//generate a counteralways@ (posedge clock or negedge reset)beginif(!reset)counter<= 0;else if(enable)beginif(counter< 53)counter="counter" + 1;endend//generate signal "csb"always@ (posedge clock or negedge reset)beginif(!reset)csb <=1;else if(counter>= 1 && counter <= 50)csb = 0;elsecsb = 1;end//Generate "sclk"always@ (posedge clock or negedge reset)begincase(counter)6'd02: sclk = 1;6'd05: sclk = 1;6'd08: sclk = 1;6'd11: sclk = 1;6'd14: sclk = 1;6'd17: sclk = 1;6'd20: sclk = 1;6'd23: sclk = 1;6'd26: sclk = 1;6'd29: sclk = 1;6'd32: sclk = 1;6'd35: sclk = 1;6'd38: sclk = 1;6'd41: sclk = 1;6'd44: sclk = 1;6'd47: sclk = 1;default sclk = 0; endcaseendalways@ (counter or csb) beginif(csb == 0)case(counter)6'h00,6'h01,6'h02,6'h03:mosi_index = 5'h00;6'h04,6'h05,6'h06:mosi_index = 5'h01;6'h07,6'h08,6'h09:mosi_index = 5'h02;6'h0A,6'h0B,6'h0C:mosi_index = 5'h03;6'h0D,6'h0E,6'h0F:mosi_index = 5'h04;6'h10,6'h11,6'h12:mosi_index = 5'h05;6'h13,6'h14,6'h15:mosi_index = 5'h06;6'h16,6'h17,6'h18:mosi_index = 5'h07;6'h19,6'h1A,6'h1B:mosi_index = 5'h08;6'h1C,6'h1D,6'hlE:mosi_index = 5'h09;6'h1F,6'h20,6'h21:mosi_index = 5'h0A ;6'h22,6'h23,6'h24:mosi_index = 5'h0B;6'h25,6'h26,6'h27:mosi_index = 5'h0C ;6'h28,6'h29,6'h2A:mosi_index = 5'h0D ;6'h2B,6'h2C,6'h2D:mosi_index = 5'h0E;6'h2E,6'h2F,6'h30:mosi_index = 5'h0F;default:mosi_index = 5'h00;endcaseelsemosi_index = 5'h00:endassign mosi="spi"_data[mosi_index3];(声明:以上程序已经过修改,只供借鉴,不可用作商业用途)用Verilog HDL实现的SPI总线接口模块,在ModelSim 中编译、调试,并做了前仿真。

前仿真通过后,又在Altera公司的EPXA10 Develop Board上做了FPGA验证,结果与在ModelSim 中的仿真结果一致。

最后在base band与RF的联合调试过程中,该SPI总线接口模块达到了预期的要求。

参考文献[1] 任志斌,车长征.串行外设接口SPI的应用[J].电子技术应用,2002,29(10):20-22.[2] 易志明.SPI串行总线接口及其实现[j].自动化与仪器仪表,2002,(6):45-48.[3] 夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2003. 系统分类: CPLD/FPGA | 用户分类: 单片机 | 来源: 转贴 | 【推荐给朋友】 | 【添加到收藏夹】可复用SPI模块IP核的设计与验证摘要:SoC是超大规模集成电路的发展趋势和新世纪集成电路的主流。

其复杂性以及快速完成设计、降低成本等要求,决定了系统级芯片的设计必须采用IP (Intellectual Property)复用的方法。

本文介绍以可复用IP设计方法,设计串行外设接口SPI(Serial Peripheral Interface)模块IP核的思路,用Verilog语言实现,并经FPGA验证,通过TSMC(台湾集成电路制造公司)的0.25μm 工艺生产线流水实现,完成预期功能。

关键词:SoC 可复用IP SPI AMBA总线引言随着集成电路设计技术和深亚微米制造技术的飞速发展,集成电路的规模越来越大,出现了片上系统SoC(System on Chip,又称之为系统级芯片)。

由于其在速度、功耗和成本方面的优势,发展势头迅猛。

SoC芯片是一个复杂的系统,为了在规定时间完成设计,并提高设计的可靠性,只有依赖基于IP复用的SoC设计方法。

如何为SoC设计提供可复用的IP核,成为SoC设计的基础和难点。

东南大学ASIC系统工程技术研究中心针对AMBA(Advanced Microcontroll er Bus Architecutre,先进微控制器)总线规范开发了一款代号为Garfield的嵌入式微处理器。

此微处理器除采用ARM公司ARM7TDMI内核的硬IP外,其余模块采用了自己开发的软IP。

本文以串行外设接口SPI为例,介绍基于复用的I P设计与验证的一些经验。

此SPI模块基于AMBA的APB(Advanced Periphe ral Bus,先进外设总线)规范,可以不作修改地应用在任何符号AMBA总线规范的微处理器设计中。

1 可复用IP核的SoC设计方法系统级芯片设计中,IP特指经过验证的各种超级宏单元模块电路。

VSIA(虚拟器件接口联盟)根据设计层次,将IP划分为三个层次:硬IP、软IP和介于两者之间的固IP。

硬IP性能最优但适应性较差,软IP灵活性大、可移植性好。

I P核必须具有以下特征:①可读性;②设计的衍展性和工艺适应性;③可测性;④端口定义标准化;⑤版板保护。

代码编写规则和可综合的书写规范是实现IP核的基础,可保证IP软核在任何EDA工具下编译和综合的正确性。