DSP第四章

合集下载

《DSP系统设计及应用》第四章

22

4.4 指令简介

4.4.1 内存寻址方式 C3x系列支持 组寻址方式。 系列支持4 ‘C3x系列支持4组寻址方式。每种寻址方式又支持两种或两种以上 的寻址类型。 的寻址类型。 (1)通用指令寻址方式 指令中包括2个操作数(1 ,1目的 通用指令寻址方式: (1源 目的) (1)通用指令寻址方式:指令中包括2个操作数(1源,1目的) 寄存器寻址:操作数是CPU的寄存器。 CPU的寄存器 寄存器寻址:操作数是CPU的寄存器。 立即数寻址:操作数是16位或24位的立即数。 16位或24位的立即数 立即数寻址:操作数是16位或24位的立即数。 直接寻址:操作数是24位地址指向的内容, 24位地址是由 24位地址指向的内容 位地址是由8 直接寻址:操作数是24位地址指向的内容,这24位地址是由8位的数 据页指针和16位的操作数连接而成。 16位的操作数连接而成 据页指针和16位的操作数连接而成。 间接寻址:通过一个辅助寄存器指示出操作数的地址。 间接寻址:通过一个辅助寄存器指示出操作数的地址。 (2)三操作数指令寻址方式 指令中包括3个操作数(2 ,1目的 三操作数指令寻址方式: (2源 目的) (2)三操作数指令寻址方式:指令中包括3个操作数(2源,1目的) 。 寄存器寻址:同通用指令寻址方式中的寄存器寻址。 寄存器寻址:同通用指令寻址方式中的寄存器寻址。 间接寻址:同通用指令寻址方式中的间接寻址。 间接寻址:同通用指令寻址方式中的间接寻址。 (3)并行指令寻址方式 两条指令并行绝对地址的寻址方式。 并行指令寻址方式: (3)并行指令寻址方式:两条指令并行绝对地址的寻址方式。 寄存器寻址:操作数是增强精度寄存器。 寄存器寻址:操作数是增强精度寄存器。 间接寻址:同通用指令寻址方式中的间接寻址。 间接寻址:同通用指令寻址方式中的间接寻址。 (4)分枝指令寻址方式 根据操作数特定位不同值执行不同操作。 分枝指令寻址方式: (4)分枝指令寻址方式:根据操作数特定位不同值执行不同操作。 寄存器寻址。同通用指令寻址方式中的寄存器寻址。 寄存器寻址。同通用指令寻址方式中的寄存器寻址。 程序记数器相对寻址:在程序计数器指针的基础上加上16位或32 16位或32位 程序记数器相对寻址:在程序计数器指针的基础上加上16位或32位 的偏移量。 的偏移量。

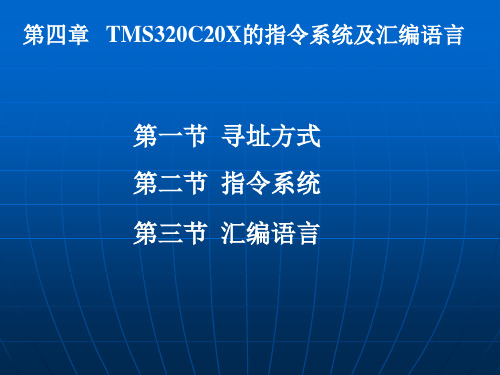

DSP第四章 TMS320C20X系列的寻址方式及汇编指令

LT *0+

执行指令前: ARP=1, (AR1)=100H,(AR0)=3 执行操作: 用AR1所指的数据存储器100H内 容装载暂时寄存器; 执行指令后: ARP=1,(AR1)=103H

⑤减去索引量

方法

举例

指令使用AR内容作

LT *0-

为数据存储器地址,

执行指令后AR内容 执行指令前:

自动减去ARO的内容。 ARP=1, (AR1)=100H,(AR0)=3

执行操作:

用AR1所指的数据存储器100H内

容装载暂时寄存器;

执行指令后:

ARP=1,(AR1)=FEH

⑥加上索引量,反向进位

方法

举例

指令使用AR内容作为 数据存储器地址,执 行指令后AR内容自动 加上AR0的内容,该 加法采用反向进位方 法。 注:主要用于FFT算 法

LT *BR0+

把AR0加到辅助寄存器中时,地址以位倒序的方 式产生,即进位是从左向右,而不是从右向左进位。

LTP ind [,ARn]

MAC MAC pma , dma

乘且累加

MAC pma, ind [ , ARn]

MACD MACD pma, dma

乘且累加,并将被寻址数据移至下一单元

MACD pma, ind [, ARn]

MPY MPY dma

MPY ind [, ARn]

MPYA/MPYS

累加前次乘积,再将TREG与被寻址数相乘

PAC PAC

PREG转入累加器ACC

SPH

存储PREG高16位,直接或间接寻址

SPL

存储PREG低16位,直接或间接寻址

例1:MAC

0FF00H,02H ;DP=6,地址300H~37FH,PM=0, CNF=1

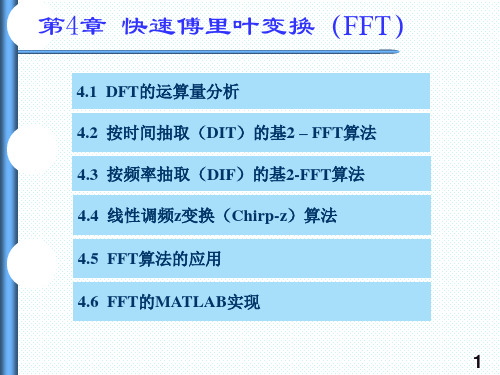

数字信号处理DSP第4章

G[3] 1

k 0,1, , N 1

2

13

4.2 按时间抽取(DIT)的基2–FFT算法

将系数统一为 WNk 2 WN2k ,则可得

x[0]

N 4点

x[4]

DFT

G[0]

X [0]

G[1]

X [1]

x[2]

N 4点

WN0

x[6]

DFT

WN2

G[2]

1 G[3]

1

X [2] X [3]

x[1]

N 4点

X m1[i] WNr X m1[ j] , X m1[i] WNr X m1[ j]

m 1, 2 ,

每一个蝶形需要一次复数乘法和两次复数加法。

17

4.2 按时间抽取(DIT)的基2–FFT算法

N点的DIT-FFT计算量为

复数乘法:

1

N 2

log2

N

N 2

复数加法:

2

N 2

log2

N

N

例: 如果每次复数乘法需要100us,每次复数加法需要20us,来 计算N=1024点DFT,则需要

12

4.2 按时间抽取(DIT)的基2–FFT算法

同理

( N 4)1

( N 4)1

G[k] DFT[g[r]]

g[2l]WN2lk2

g[2l 1]WN(22l1)k

l 0

l 0

( N 4)1

( N 4)1

g[2l]WNlk 4 WNk 2

g[2l 1]WNlk 4 ,

l 0

l 0

k 0,1,

(3) WN0 WN4 WN8 WN12 WN16 WN20 WN24 WN28

或 WN4i i 0,1, 2, 3, 4, 5, 6, 7 (dm 1)

k 0,1, , N 1

2

13

4.2 按时间抽取(DIT)的基2–FFT算法

将系数统一为 WNk 2 WN2k ,则可得

x[0]

N 4点

x[4]

DFT

G[0]

X [0]

G[1]

X [1]

x[2]

N 4点

WN0

x[6]

DFT

WN2

G[2]

1 G[3]

1

X [2] X [3]

x[1]

N 4点

X m1[i] WNr X m1[ j] , X m1[i] WNr X m1[ j]

m 1, 2 ,

每一个蝶形需要一次复数乘法和两次复数加法。

17

4.2 按时间抽取(DIT)的基2–FFT算法

N点的DIT-FFT计算量为

复数乘法:

1

N 2

log2

N

N 2

复数加法:

2

N 2

log2

N

N

例: 如果每次复数乘法需要100us,每次复数加法需要20us,来 计算N=1024点DFT,则需要

12

4.2 按时间抽取(DIT)的基2–FFT算法

同理

( N 4)1

( N 4)1

G[k] DFT[g[r]]

g[2l]WN2lk2

g[2l 1]WN(22l1)k

l 0

l 0

( N 4)1

( N 4)1

g[2l]WNlk 4 WNk 2

g[2l 1]WNlk 4 ,

l 0

l 0

k 0,1,

(3) WN0 WN4 WN8 WN12 WN16 WN20 WN24 WN28

或 WN4i i 0,1, 2, 3, 4, 5, 6, 7 (dm 1)

DSP完整课件第4章

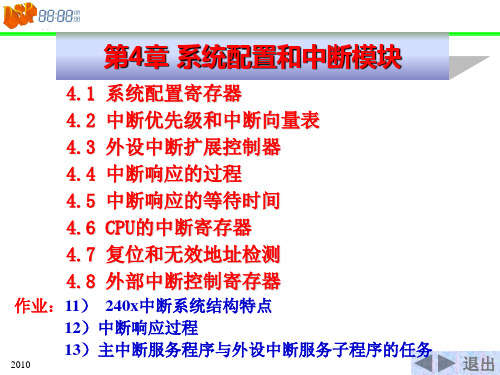

第4章 系统配置和中断模块

4.1 4.2 4.3 4.4 4.5 4.6 4.7 4.8 系统配置寄存器 中断优先级和中断向量表 外设中断扩展控制器 中断响应的过程 中断响应的等待时间 CPU的中断寄存器 复位和无效地址检测 外部中断控制寄存器

作业:11) 240x中断系统结构特点 12)中断响应过程 13)主中断服务程序与外设中断服务子程序的任务

2010退出Βιβλιοθήκη 4.2 中断优先级和中断向量表

CPU级中断向量表及优先级

K值 0 1 2 3 4 5 6 7 8 9 16 17 18 19 ... 31

2010

CPU中断向量 0000h 0002h 0004h 0006h 0008h 000Ah 000Ch 000Eh 0010h ... 0020h 0022h 0024h 0026h ... 003Eh

2010

退出

中断系统

240x的2级(层次)中断结构。

(1) CPU内核级(顶层)中断(INT1~INT6)

(2) 外设级(底层)中断 利用6个内核级中断扩展38个外设级中断。

(2) 外设级(底层)中断 每级可屏蔽的CPU级中断(INT1~6)又对应多个外设级中 断源,每个外设级中断源具有唯一的中断入口地址向量,它 们构成了外设级中断向量表。 • 外设中断向量表 用来获取响应外设中断服务子程序。一般存放跳转到外 设中断服务子程序的跳转指令。 • 外设中断服务子程序 完成具体中断要实现的功能。

优先级 1 4 5 6 7 8 9

中断名称 RS INT1 INT2 INT3 INT4 INT5 INT6

INT8

INT16 TRAP NMI ... INT31

3 2

说明 硬件上电复位中断(不可屏蔽) 1号可屏蔽中断 2号可屏蔽中断 3号可屏蔽中断 4号可屏蔽中断 5号可屏蔽中断 6号可屏蔽中断 保留 用户自定义软件中断 .... 用户自定义软件中断 陷阱软件中断 NMI软件中断 保留 ... 用户自定义软件中断

4.1 4.2 4.3 4.4 4.5 4.6 4.7 4.8 系统配置寄存器 中断优先级和中断向量表 外设中断扩展控制器 中断响应的过程 中断响应的等待时间 CPU的中断寄存器 复位和无效地址检测 外部中断控制寄存器

作业:11) 240x中断系统结构特点 12)中断响应过程 13)主中断服务程序与外设中断服务子程序的任务

2010退出Βιβλιοθήκη 4.2 中断优先级和中断向量表

CPU级中断向量表及优先级

K值 0 1 2 3 4 5 6 7 8 9 16 17 18 19 ... 31

2010

CPU中断向量 0000h 0002h 0004h 0006h 0008h 000Ah 000Ch 000Eh 0010h ... 0020h 0022h 0024h 0026h ... 003Eh

2010

退出

中断系统

240x的2级(层次)中断结构。

(1) CPU内核级(顶层)中断(INT1~INT6)

(2) 外设级(底层)中断 利用6个内核级中断扩展38个外设级中断。

(2) 外设级(底层)中断 每级可屏蔽的CPU级中断(INT1~6)又对应多个外设级中 断源,每个外设级中断源具有唯一的中断入口地址向量,它 们构成了外设级中断向量表。 • 外设中断向量表 用来获取响应外设中断服务子程序。一般存放跳转到外 设中断服务子程序的跳转指令。 • 外设中断服务子程序 完成具体中断要实现的功能。

优先级 1 4 5 6 7 8 9

中断名称 RS INT1 INT2 INT3 INT4 INT5 INT6

INT8

INT16 TRAP NMI ... INT31

3 2

说明 硬件上电复位中断(不可屏蔽) 1号可屏蔽中断 2号可屏蔽中断 3号可屏蔽中断 4号可屏蔽中断 5号可屏蔽中断 6号可屏蔽中断 保留 用户自定义软件中断 .... 用户自定义软件中断 陷阱软件中断 NMI软件中断 保留 ... 用户自定义软件中断

DSP第四章6概论

七、双线性变换法

1、变换原理 使数字滤波器的频率响应

与模拟滤波器的频率响应相似。

冲激响应不变法、阶跃响应不变法:时域模仿逼近 缺点是产生频率响应的混叠失真

:[,]

1

:

T

,

T

tg 1T 2

z es1T

tg 1T 2

sin 1T 2

cos 1T 2

j 1T

j 1T

e 2 e 2

2 j j 1T

c tg 1T 2

s

c

1 1

z z

1 1

z cs cs

2、变换常数c的选择

1)低频处有较确切的对应关系: 1

1

c

tg

1T 2

c

1T 2

c 2 T

2)某一特定频率严格相对应: c c

c

c tg

1cT 2

c tg c

2

c

cctg

Байду номын сангаас

c

2

特定频率处频率响应严格相等,可以较准确地 控制截止频率位置

4、优缺点

优点:避免了频率响应的混迭现象

c tg

2 s 平面与 z 平面为单值变换

0 0 0 0

缺点:除了零频率附近, 与 之间严重非线性

1)线性相位模拟滤波器 非线性相位数字滤波器

2)要求模拟滤波器的幅频响应为分段常数型,不 然会产生畸变

分段常数型模拟滤波器 经变换后仍为分段常数 型数字滤波器,但临界 频率点产生畸变

j 1T

e 2 e 2

2

j 1T

j 1T

s1T

s1T

s

j

e2

j 1T

e 2

j 1T

1、变换原理 使数字滤波器的频率响应

与模拟滤波器的频率响应相似。

冲激响应不变法、阶跃响应不变法:时域模仿逼近 缺点是产生频率响应的混叠失真

:[,]

1

:

T

,

T

tg 1T 2

z es1T

tg 1T 2

sin 1T 2

cos 1T 2

j 1T

j 1T

e 2 e 2

2 j j 1T

c tg 1T 2

s

c

1 1

z z

1 1

z cs cs

2、变换常数c的选择

1)低频处有较确切的对应关系: 1

1

c

tg

1T 2

c

1T 2

c 2 T

2)某一特定频率严格相对应: c c

c

c tg

1cT 2

c tg c

2

c

cctg

Байду номын сангаас

c

2

特定频率处频率响应严格相等,可以较准确地 控制截止频率位置

4、优缺点

优点:避免了频率响应的混迭现象

c tg

2 s 平面与 z 平面为单值变换

0 0 0 0

缺点:除了零频率附近, 与 之间严重非线性

1)线性相位模拟滤波器 非线性相位数字滤波器

2)要求模拟滤波器的幅频响应为分段常数型,不 然会产生畸变

分段常数型模拟滤波器 经变换后仍为分段常数 型数字滤波器,但临界 频率点产生畸变

j 1T

e 2 e 2

2

j 1T

j 1T

s1T

s1T

s

j

e2

j 1T

e 2

j 1T

DSP原理及应用第四章

9

常用的汇编命令:

汇编命令 .title .end 作 用 .title "example.asm" 放在汇编语言源程序的最后 .text段是源程序正文。经汇编后,紧随.text后的是可执 行程序代码 有两种数据形式:.int和.word Table: .word 1,2,3,4 .word 8,6,4,2 表示在程序存储器标号为table开始的8个单元中存放初 始化数据1、2、3、4、8、6、4和2 .bss x,4表示在数据存储器中空出4个存储单元存放变 量x1,x2,x3和x4 .sect " vectors "定义向量表,紧随其后的是复位向量 和中断向量,名为vectors STACK .usect "STACK",10H在数据存储器中留出16 个单元作为堆栈区,名为STACK .def 举 例 紧跟其后的是用双引号括起的源程序名 结束汇编命令,汇编程序将忽略此后的任何源 语句,所以它应是程序的最后语句 紧跟其后的是汇编语言程序正文

分段的优点:在目标文件中将放置程 序、数据、变量的代码分开,便于在链 接时作为一个单独的部分分配存储器。 由于大多数系统都有好几种形式的存储 器,通过对各个段重新定位,可以使目 目标文件中的段与目标存 标存储器得到更为有效的利用。 储器之间的关系

17

2.外部符号的概念

外部符号 在一个模块中定义,可在另 一个模块中引用的符号。

25

段命令应用举例

汇编语言源程序: .data coeff .word 044h,055h,066h .bss buffer,8 prt .word 0456h .text add: LD 0Dh,A aloop:SUB #1,A BC aloop,AGEQ .data ivals .word 0CCh,0DDh,0EEh

DSP_第四-八章演示文档

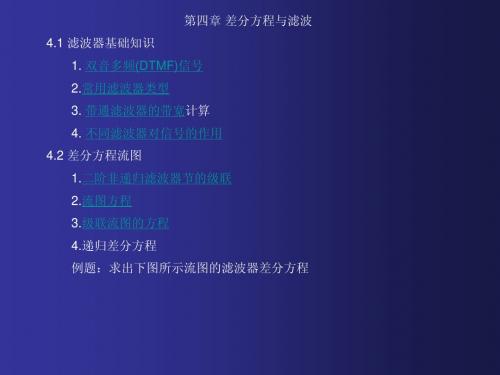

第四章 差分方程与滤波 4.1 滤波器基础知识 1. 双音多频(DTMF)信号 2.常用滤波器类型 3. 带通滤波器的带宽计算

4. 不同滤波器对信号的作用

4.2 差分方程流图 1.二阶非递归滤波器节的级联 2.流图方程 3.级联流图的方程 4.递归差分方程 例题:求出下图所示流图的滤波器差分方程

例:写出下图所示脉冲响应的滤波器差分方程

5.4 数字图像滤波

1. 数字图像及其灰度 2. 数字图像的滤波 ห้องสมุดไป่ตู้. 低通滤波的文字

第六章 z变换 6.1 常用z变换表 z变换的性质 1.举例 5.3 滑动平均滤波器

1. 举例

5.4 数字图像滤波 1. 数字图像及其灰度 2. 数字图像的滤波 3. 低通滤波的文字

第七章 傅立叶变换与滤波器形状 7.3.2 幅度相应和相位相应 1. 脉冲通过梳状滤波器 2. ‘hello’通过梳状滤波器 例:把数字信号x[n]=0.5cos(pi/4*n)加到如下数字滤波器上,求输出信号。

例:数字频率为1.5弧度的余弦波通过滤波器,在此频率下,滤波器增益为21dB,相位差为86度,如果输入幅度为20,相位为12度,则输出幅度和相 位是多少。 对于n=10和n=20求出y[n]的值。

推断滤波器形状:H(z)=1/(z-0.45)

第八章 数字信号频谱 8.1 频谱的意义 1. 正弦波合成方波 2. 非周期数字信号 3. 非周期数字信号及其频谱

z 2 z cos() z 2 2 z cos 1

z sin( ) z 2 z cos 1

2

z 2 z cos() z 2 2 z cos 2

z sin() z 2 z cos 2

2

z变换的性质 性质 时间反转 线形 时移 序列 g[-n] ag[n]+bh[n] g[n-m]

4. 不同滤波器对信号的作用

4.2 差分方程流图 1.二阶非递归滤波器节的级联 2.流图方程 3.级联流图的方程 4.递归差分方程 例题:求出下图所示流图的滤波器差分方程

例:写出下图所示脉冲响应的滤波器差分方程

5.4 数字图像滤波

1. 数字图像及其灰度 2. 数字图像的滤波 ห้องสมุดไป่ตู้. 低通滤波的文字

第六章 z变换 6.1 常用z变换表 z变换的性质 1.举例 5.3 滑动平均滤波器

1. 举例

5.4 数字图像滤波 1. 数字图像及其灰度 2. 数字图像的滤波 3. 低通滤波的文字

第七章 傅立叶变换与滤波器形状 7.3.2 幅度相应和相位相应 1. 脉冲通过梳状滤波器 2. ‘hello’通过梳状滤波器 例:把数字信号x[n]=0.5cos(pi/4*n)加到如下数字滤波器上,求输出信号。

例:数字频率为1.5弧度的余弦波通过滤波器,在此频率下,滤波器增益为21dB,相位差为86度,如果输入幅度为20,相位为12度,则输出幅度和相 位是多少。 对于n=10和n=20求出y[n]的值。

推断滤波器形状:H(z)=1/(z-0.45)

第八章 数字信号频谱 8.1 频谱的意义 1. 正弦波合成方波 2. 非周期数字信号 3. 非周期数字信号及其频谱

z 2 z cos() z 2 2 z cos 1

z sin( ) z 2 z cos 1

2

z 2 z cos() z 2 2 z cos 2

z sin() z 2 z cos 2

2

z变换的性质 性质 时间反转 线形 时移 序列 g[-n] ag[n]+bh[n] g[n-m]

第4章TMS320x28xx系列DSP综述

电气工程学院

DSP应用技术

帧同步和数据时钟的极性都是可编程的;可编程的内部

时钟和同步帧; 能同CODEC、AIC(Analog Interface Chips)等标准 串行A/D和D/A器件接口; 两个16× 16深度的发送通道FIFO; 两个16× 16深度的接收通道FIFO。

20

盐城工学院

电气工程学院

DSP应用技术

4.3.1 事件管理器(281x处理器)

在281x DSP上有EVA和EVB两个事件管理器,它们 是数字电机控制应用所使用的非常重要的外设,能够实 现机电设备控制的多种必要功能。 每个事件管理器模块包括定时器、比较器、捕捉单 元、PWM逻辑电路、正交编码脉冲电路以及中断逻辑电 路等。

4. 专门的分支跳转(Branch-look-)硬件减少了条件指令执行的 反应时间,条件存储操作更进一步提高了28xx的性能。 5. 28xx控制器具有许多独特的功能,如可在任何内存位置进 行单周期读一修改一写操作供了高性能和代码高效编程,还提

供了许多其他原始指令。

6. F28xx系列控制器在1个闪存上可以提供150 MIPS的性能。 7. F2808、F2806和F2801可以提供经济高效的基于闪存的数 字信号控制器,并且运行速度达100 MIPS。

27

盐城工学院

电气工程学院

DSP应用技术

4.3.6 CAN总线通信模块

CAN总线是一种串行通信协议,具有较强的抗干扰能力,

可以应用在电磁噪声比较大的场合。 F281x的CAN总线接口模块是增强型的CAN接口,完全支 持CAN2.0B总线规范。它有32个可配置的接收/发送邮箱, 支持消息的定时邮递功能。最高通信速率可以达到1Mbps, 可以使用该接口构建高可靠的CAN总线控制或检测网络。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

位8:保留 位7:ADC CLKEN,ADC模块时钟使能控制位 0-禁止ADC模块时钟(节能) 1-使能ADC模块时钟,且正常运行 位6:SCICLKEN,SCI模块时钟使能控制位 0-禁止SCI模块时钟(节能) 1-使能SCI模块时钟,且正常运行

位5:SPICLKEN, SPI模块时钟使能控制位 0-禁止SPI模块时钟(节能) 1-使能SPI模块时钟,且正常运行 位4:CANCLKEN, CAN模块时钟使能控制位 0-禁止CAN模块时钟(节能) 1-使能CAN模块时钟,且正常运行 位3:EVBCLKEN, EVB模块时钟使能控制位 0-禁止EVB模块时钟(节能) 1-使能EVB模块时钟,且正常运行

如这些引脚作I/O使用,则不使用输入时钟限定电路

位5:WD保护位,该位可用来禁止WD工作。该位 是-个只能清除的位,复位后=1。通过向该位写 1对其清0。

0-保护WD,防止WD被软件禁止。 1-复位时的默认值,能够通过软件禁止WD工作 位4:XMIF HI-Z。该位控制外部存储器接口信号 (XMIF)。 0-所有XMIF信号为正常驱动模式(非高阻态)。 1-所有XMIF信号处于高阻态。

外设中断请求寄存器和外设中断应答寄存器 都属于外设中断扩展模块用来向CPU产生INT1INT6中断请求的内部寄存器。这些寄存器用于测 试目的,编程时可以忽略。用户只能对其读。 1.外设中断向量寄存器(PIVR) 外设中断向量寄存器(PIVR)映射在数据存储 器空间中的地址为701Eh,该寄存器的16位V15- V0,为最近一次被应答的外设中断的地址向量。

中断请求(PIRQ)标志位一直保持到中断应答自动 清除或用软件将其清除。 在高层次中断,或逻辑运算的多个外设中断请求 INTn产生一个到CPU的中断请求,它是2个CPU时 钟脉冲宽的低电平脉冲。 当多个外设同时发出中断请求时,CPU总是响应 优先级高的中断请求。 注意:外设中断请求标志位是在CPU响应中断时 自动清除,即在高层次中断时清0,而不是在低层 次中断时,清0。

(4)IFR和IMR控制的是核心级的中断, 所有外设在它们各自的配置/控制寄存器都 有相应的中断屏蔽和标志位。

4.4.2 CPU中断屏蔽寄存器(IMR) IMR映射在数据存储器空间中的地址为0004h

位15-6:保留位。 位5-0:分别为INT6-INT1中断的屏蔽位。 0-中断INTn被屏蔽。 1-中断INTn被使能。

0: DSP设置为微控制器方式,片内FLASH映射 到程序存储器空间,地址为0000h-7FFFh。

1: DSP设置为微处理器方式,程序空间 0000h-7FFFh被映射到片外程序存储器空 间(必须外扩外部程序存储器) 位1-0:SARAM的程序/数据空间选择 DON PON SARAM状态 0 0 地址空间不被映射,该空间被分配到 外部存储器 0 1 SARAM 被映射到片内程序空间 1 0 SARAM 被映射到片内数据空间 1 1 SARAM 被映射到片内程序空间,又 被映射到片内数据空间

下图为外设中断扩展模块图。

4.3.1 中断请求层次和结构 外设中断个数很多,用一个两级中断结构来扩展 可响应的中断个数。 DSP的中断请求/应答硬件逻辑和中断服务程序软 件都有两级层次的中断。 在低层次中断,从几个外设来的外设中断请求 (PIRQ)在中断控制器处进行或运算,产生一个 INTn(n=1~6)中断请求。

在对IFR操作时应注意以下几点: (1)要想清除某一IFR位,必须向该位写1,而 不是0; (2)当一个可屏蔽中断被响应时,只有IFR位 被清除,而相应的外设控制寄存器中的中断请 求标志位不会被清除。如果需要清除这些标志 位,应该使用软件来清除。

(3)当通过INTR指令来请求中断,且相应 的IFR位被置1时,CPU不会自动清除该位, 该位必须由软件来清除。

在高层次中断,从INTn中断请求产生一个到CPU 的中断请求。 如果一个引起中断的外设事件发生且相应的中断 使能位被置1,则会产生一个外设到中断控制器的 中断请求。 如果一个外设既可产生高级的中断请求,又可产 生低级中断请求(如SCI、SPI、ADC等),对应 的中断优先级位的值也被送到PIE来进行判断。

00-进入IDLE1(LPM0)模式; 01-进入IDLE2(LPM1)模式; 1x-进入HALT(LPM2)模式。 位11-9:CLK PS2-CLK PS0,(PLL)时钟预定 标选择位,选择输入时钟频率fin的倍频系数,如 表4.1所示。

CLKPS2 CLKPS1 CLKPS0 系统时钟 频率 0 0 0 4× fin 0 0 0 1 1 1 1 0 1 1 0 0 1 1 1 0 1 0 1 0 1 2× fin 1.33× fin 1× fin 0.8× fin 0.66× fin 0.57× fin 0.5× fin

第4章系统配置和中断模块

本章介绍LF240x DSP的系统配置寄存器和 中断模块。

系统配置:用来对DSP片内的功能模块进行用户配 置,根据具体用途来进行模块定制。 中断模块:主要包括-中断优先级和中断向量表 、外设中断扩展控制器(PIE)、中断向量、中断响 应的流程、中断响应的时间、CPU中断寄存器、 外设中断寄存器、复位、无效地址检测、外部中 断控制寄存器。

位3:(BOOT使能位)。这位反映了BOOTEN* 引脚在复位时的状态。

0-使能引导ROM。地址0000h-00FFhROM块 占用。禁止用FLash存储器。 1-禁止引导ROM。LF2407片内Flash程序 存储器映射地址范围为0000h-7FFFh。 位2:MP/MC*(微处理器/微控制器选择)。

位2:EVACLKEN, EVA模块时钟使能控制位 0-禁止EVA模块时钟(节能) 1-使能EVA模块时钟,且正常运行

位1:保留

位0:ILLADR, 无效地址检测位 检测到无效地址时,该位置1。置1后需软件来 清0,向该位写1可将其清零。复位时该位为0。

注意:任何无效的地址会导致不可屏蔽中断 (NMI)事件发生。

2.系统控制和状态寄存器2(SCSR2) SCSR2被映射到数据存储器空间7019h

位15-7:保留位 位6:I/P QUAL,时钟输入限定。它限定输入到 LF240x的CAP1-6、XINT1-2、ADCSOC、 PDPINTA*/PDPINTB*引脚上的最小脉冲宽度。 脉冲宽度只有达到这个宽度之后,内部的输入状 态才会改变。 0-锁存脉冲至少需要5个时钟周期; 1-锁存脉冲至少需要11个时钟周期;

(2) 当外设发出中断请求,但是其INTn标志位却在 CPU应答请求之前已经被清0。 在上述两种情况下,并没有外设中断请求送到中 断控制器,因此中断控制器不知道哪个外设中断 向量装入到PIVR,此时向PIVR中装入假中断向量 0000h。从而避免程序进入中断死循环中。 2.软件结构

中断服务子程序有两级:通用中断服务子程序 (GISR)和特定中断服务子程序(SISR)。 在GISR中保存必要的上下文,从外设中断向 量寄存器(PIVR)中读取外设外设中断向量,这个 向量用来产生转移到SISR的地址入口。 程序一旦进入特定中断服务子程序后,所有 的可屏蔽中断都被屏蔽。 外设中断扩展(PIE)不包括象复位和NMI这样的 不可屏蔽中断。

4.3.2 中断向量 当CPU接受中断请求时,它并不知道是哪一 外设事件引起的中断请求。 为了使CPU能够区别不同外设引起的中断事 件, 需经PIE译码,决定哪个中断请求被响应。 某个外设的中断请求有效时,都会产生唯一的外 设中断向量,被装载到外设中断向量寄存器(PIVR) 。

CPU应答外设中断请求时,从PIVR中读取相应的 中断向量,并产生一个转到该中断服务子程序 (GISR)入口的向量。

4.4.3 外设中断寄存器 外设中断寄存器包括如下几种:

外设中断向量寄存器(PIVR) 外设中断请求寄存器0(PIRQR0)

外设中断请求寄存器1(PIRQR1) 外设中断请求寄存器2(PIRQR2) 外设中断应答寄存器0(PIACKR0) 外设中断应答寄存器1(PIACKR1) 外设中断应答寄存器2(PIACKR2)

LF240x有两个中断向量表, CPU向量表和外设向量 表。 CPU向量表用来得到响应中断请求的一级通用中 断服务子程序(GISR)。

外设向量表用来获取响应某外设事件的特定中断 服务子程序(SISR)。

在一级通用中断服务子程序GISR中可读出 PIVR中的值,保护现场后,用PIVR中的值来产生 一个转到SISR的向量。例如,可屏蔽中断XINT1( 高级模式级别为INT1,优先级为7)产生一个中断 请求,CPU对其响应。这时,0001h(XINT1的外 设中断向量)被装载到PIVR中,CPU获取被装载 到PIVR中的值之后,用这个值来判断是哪一个外 设引起的中断,接着转移到相应的SISR。

位15-6:保留位。 位5-0:分别为INT6~INT1的中断标志位。 0-无INTn(n=1-6)的中断挂起, 1-表示有INTn(n=1-6)的中断挂起。 中断标志寄存器包含了所有可屏蔽中断INT6-INT1 的标志位。

当一个外设发出可屏蔽中断请求时,中断标志寄 存器的相应标志位被置1。如果该外设对应中断屏 蔽寄存器中的中断使能位也为1,则该中断请求被 送到CPU,此时该中断正被挂起或等待响应。 读取IFR可以识别挂起的中断,向相应的IFR位 写1将清除已挂起的中断。 CPU响应中断或复位都能将IFR标志清除。

4.1 系统配置寄存器

4.1.1 系统控制和状态寄存器 1.系统控制和状态寄存器1(SCSR1) SCSR1映射到数据存储器空间的KSRC,为CLKOUT引脚输出时钟源的选择位

0-CLKOUT引脚输出CPU时钟; 1-CLKOUT引脚输出WDCLK时钟。 位13、12:LPM1,LPM0,低功耗模式选择,指 明在执行IDLE 指令后进入哪一种低功耗模式。

3.不可屏蔽中断 LF240x DSP 无NMI引脚,在访问无效的地址 时,不可屏蔽中断(NMI)就会发出请求。当NMI被 响应后,程序将转到不可屏蔽中断向量入口地址 0024h处。