基于CMOS全差分运算放大器的全集成有源滤波器的设计_解读

全差分套筒式共源共栅放大器及其共模反馈电路解读

一 毕业设计(论文)进展情况运算放大器是许多模拟系统和混合数字信号系统中的一个完整部分,也是构成这些系统的基本单元. 因而设计高性能的运算放大器可以使系统的总体性能得到提高。

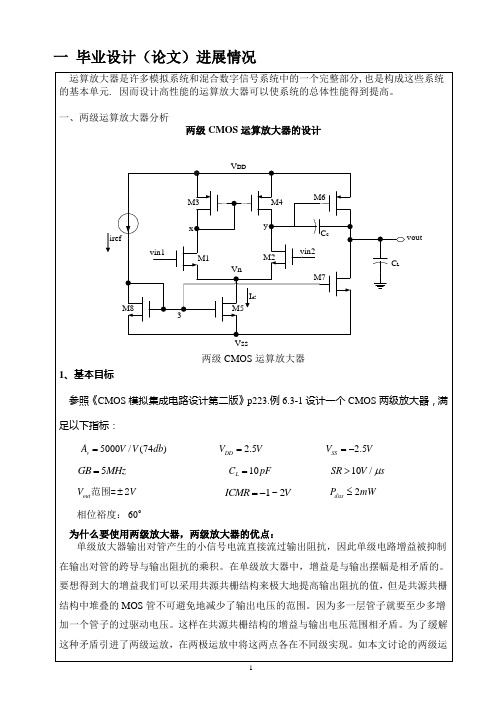

一、两级运算放大器分析两级CMOS 运算放大器的设计V DDV SSM1M2M3M4M5M6M7M8VnC LC cvoutvin1vin2irefxy3I d5两级CMOS 运算放大器1、基本目标参照《CMOS 模拟集成电路设计第二版》p223.例6.3-1设计一个CMOS 两级放大器,满足以下指标:5000/(74)v A V V db = 2.5DD V V = 2.5SS V V =-5GB MHz = 10L C pF = 10/SR V s μ>out V V ±范围=2 1~2ICMR V =- 2diss P mW ≤ 相位裕度:60为什么要使用两级放大器,两级放大器的优点:单级放大器输出对管产生的小信号电流直接流过输出阻抗,因此单级电路增益被抑制在输出对管的跨导与输出阻抗的乘积。

在单级放大器中,增益是与输出摆幅是相矛盾的。

要想得到大的增益我们可以采用共源共栅结构来极大地提高输出阻抗的值,但是共源共栅结构中堆叠的MOS 管不可避免地减少了输出电压的范围。

因为多一层管子就要至少多增加一个管子的过驱动电压。

这样在共源共栅结构的增益与输出电压范围相矛盾。

为了缓解这种矛盾引进了两级运放,在两极运放中将这两点各在不同级实现。

如本文讨论的两级运放,大的增益靠第一级与第二级相级联而组成,而大的输出电压范围靠第二级这个共源放大器来获得。

典型的无缓冲CMOS 运算放大器特性 边界条件要求工艺规范 见表2、3电源电压 %105.2±±V电源电流 100Μa 工作温度范围0~70°特性要求增益 dB 70≥增益带宽 ≥5MHz建立时间 s μ1≤ 摆率 s /5μV ≥ICMR ≥V 5.1± CMRR ≥60dB PSRR ≥60dB 输出摆幅 ≥V 5.1±输出电阻 无,仅用于容性负载失调 mV 10±≤噪声 ≤100Hz nV (1kHz 时) 版图面积≤50002)(最小沟道长度⨯ 表1 典型的无缓冲CMOS 运算放大器特性2、两级放大电路的电路分析图1中有多个电流镜结构,M5,M8组成电流镜,流过M1的电流与流过M2电流1,23,45/2d d d I I I ==,同时M3,M4组成电流镜结构,如果M3和M4管对称,那么相同的结构使得在x ,y 两点的电压在Vin 的共模输入范围内不随着Vin 的变化而变化,为第二极放大器提供了恒定的电压和电流。

EMC基础之有源滤波器

EMC基础之滤波三、有源滤波器[ 录入者:admin | 时间:2007-11-16 13:34:16 | 作者: | 来源:采集所得 | 浏览:602次 ]中国电磁兼容网第三节有源滤波器1.一、有源滤波器的特性有源滤波器是由有源器件(例如晶体管、集成运算放大器等)和阻容等元件组成的一类滤波器。

近年来,成运算放大器发展十分迅速,一些有源滤波器中的有源器件,几乎都是采用了集成运放。

与无源滤波器相比,有源滤波器一般具有下列特点:(1)由于使用了有源器件,信号在无源器件(例如电阻)上的损失可口在有源器件中得到补充。

因而,有可能在电路中优先采用损耗耗较大而体积较小的电阻来代替无源滤波器中的电感器件。

这样不仅可以使滤波器的重量和体积大大缩小,而且可以避免由电感所带来的非线性、参数调整困难以及制造成本高等缺点。

另外从抑制干扰的角度考虑,这样就从根本上排除了电感所具有的对电磁场敏感、易检取外界噪声和本身易向外界施放电磁干扰噪声的弊端。

(2)由于运算放大器具有输入阻抗高、输出阻抗低以及高增益、高稳定性和闭环增益等参数调整灵活的一系列优点,从而为有源滤波器的设计提供了很大的方便。

(3)有源滤波器频率精度高,一般可达到±3%~±0.5%;频率稳定性好,通常可做到10-3~10-5/℃;低频滤波特性好,例如用集成运放和阻容元件组成的有源滤波器可使滤波频率范围低达10ˉ3H Z,并且具有较好的频率稳定性。

这些指标,都是无源滤波器难以达到的。

(4)有源滤波器的上限频率由于受有源器件(主要是集成运放)本身带宽的限制,一般只用在几十千赫以下的频率范围内,其最高频率也只接近1M H Z,因而在更高的频率范围内一般均采用无源滤波器。

这是有源滤波器的最大缺点。

有源滤波器按其工作性质,仍可分为低通滤波器、高通滤波器、带通滤波器和带阻滤波器四种基本类型。

此外,还有移相滤波器和开关电容滤波器以及跟踪滤波器等类型。

2.二、低通滤波器低通滤波器是一种用于通过某一频率以下的低频信号,抑制或衰减该频率以上的高频信号的滤波电路。

基于斩波技术的CMOS运算放大器失调电压的消除设计

图 3 斩波调制电路

由互补相位的时钟信号来控制放大电路的输入及输 出以实现信号的斩波放大功能。其中,电容 C in 表 示主放大器的差分输入电容, V T +和 V T -代表差分 输入信号, R S 是输入信号源的内阻。 这种电路简单且易于控制,但会因 M O S 开关 管的时钟馈通效应额外引入残余失调电压。这里, 时钟馈通效应是指当开关闭合时MOS管沟道中存储 的电荷将注入到源漏端的寄生电容中, 它会导致主 放大器输入端有尖峰电压 V spike出现。 由这种尖峰电 压所引入的放大器输入失调电压称为残余失调电 压。时域下的尖峰信号如图 4,这里 τ 表示尖峰信 62

Hale Waihona Puke 60半导体技术第 28 卷第 8 期

二 O O 三年八月

EDA 技术专栏

技术主要有三种:自动调零(A Z ) 、相关双采样 技术(C D S )和斩波技术(C H S ) 。其中,自 动调零技术是先采样和保持失调电压, 再从信号中 减去失调电压部分 ; 相关双采样技术是自动调零技 术的一个特殊例子, 它能实质性地减少低频 1/ f 噪 声, 却会增加放大器的热噪声, 且还会残余下由于 开关管的时钟馈通效应所引入的失调电压 [3] ;斩波 技术则是通过把输入信号和开关型方波信号耦合,

Design of CMOS operating amplifier for eliminating DC offset based on chopper technology

WU Sun-tao, LIN Fan, GUO Dong-hui, LI Jing

( Pen-Tung Sah MEMS Research Center, Physics Department, Xiamen University, Xiamen , 361005, China )

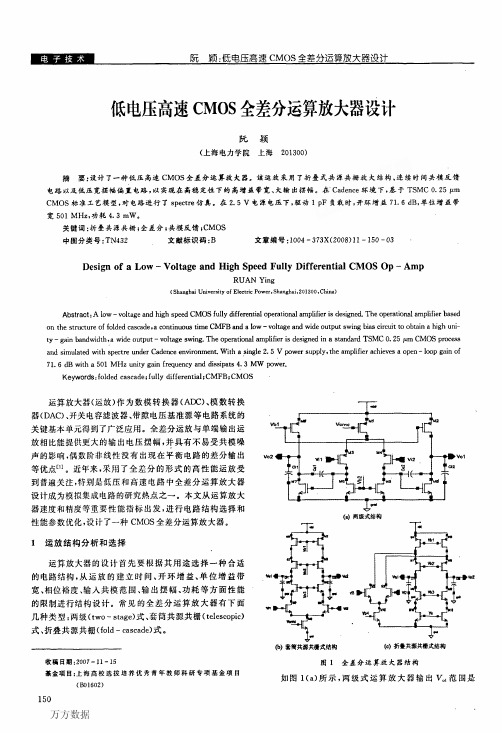

低电压高速CMOS全差分运算放大器设计双

运算放大器的设计首先要根据其用途选择一种合适 的电路结构,从运放的建立时问、开环增益、单位增益带 宽、相位裕度、输入共模范围、输出摆幅、功耗等方面性能 的限制进行结构设计。常见的全差分运算放大器有下面 几种类型:两级(two—stage)式、套筒共源共栅(telescopic) 式、折叠共源共栅(fold—cascade)式。

4‘结语

本文使用TSMC公司的CM025工艺

设计并实现了一个低压高速全差分运算放

大器。采用折叠共源共栅结构,在达到较高

的带宽同时,增大了输出摆幅。连续时间共

模反馈电路以及低压宽摆幅偏置电路,实现

(1)信置电路OO半电路小信号等效模型

图3偏置电路及半电路小信号等效模型

了电路的高稳定性。该运放在2.5 V电源 电压下,’单位增益带宽可以达到501 MHz, 直流增益71.6 dB,相位裕度51。,功耗

P。《P,,更接近于原点,因此P2为折叠共源共栅运放的 主极点,P。为次极点。

要提高开环增益A。,可以采取增加M8,M9的跨导和

1 5】

沟逝长度,但将引起其源极寄生电容的增加和漏源饱和电 正减小,从而降低运放的次极点频率。同样增加M10, M11的沟道长度,会使A。增加而次极点频率减小。考虑 到M4,M5,M6,M7不在信号通路上,因此可以增加其沟 道长度球增加输出阻抗,而不降低工作速度。

△gM9(r2//rlo)r9 R。。“M7一r4+r7[1+(gM7+gM7b)^]

△gM7 r7 r4 r为MOS管的小信号输出电阻。负载电容C。远大于MOS 管各端的寄生电容,CL△cD瞰+CD曲+CD酊。。

节点1对应的极点P。:

P-=一石万勿习丽i1冠i而△一等

节点2对应的极点P。:

模拟cmos集成电路设计第二版知识点总结

模拟cmos集成电路设计第二版知识点总结《模拟CMOS集成电路设计》第二版是由Behzad Razavi编写的一本关于模拟集成电路设计的经典教材。

本书主要介绍了模拟集成电路设计的基本原理、技术和方法,包括以下几个方面的知识点:1.CMOS技术基础:介绍CMOS技术的发展历程、基本概念和特点,以及MOSFET器件的工作原理、特性和参数。

2.单级放大器:讨论了单级放大器的基本结构、设计方法和性能指标,包括共源放大器、共栅放大器和共漏放大器等。

3.差分放大器:介绍了差分放大器的工作原理、性能指标和设计方法,以及如何利用差分放大器实现信号放大、电压参考和电流镜等功能。

4.运算放大器:详细阐述了运算放大器的设计原理、性能指标和实际应用,包括折叠式Cascode放大器、套筒式Cascode放大器和两级放大器等。

5.数据转换器:介绍了模数转换器(ADC)和数模转换器(DAC)的基本原理、结构和设计方法,包括逐次逼近型ADC、闪存型ADC、Σ-Δ型ADC和R-2R梯形DAC等。

6.滤波器和振荡器:讨论了模拟滤波器的基本原理、设计和实现方法,包括有源RC滤波器、Gm-C滤波器和开关电容滤波器等;同时介绍了振荡器的工作原理、性能指标和设计方法,包括环形振荡器、LC振荡器和晶体振荡器等。

7.电源管理:阐述了线性稳压器、开关稳压器和电荷泵等电源管理电路的工作原理、性能指标和设计方法。

8.频率响应和稳定性:介绍了频率响应的基本概念、分析方法和设计技巧,以及如何利用频率补偿技术提高电路的稳定性。

9.噪声分析:讨论了噪声的来源、类型和影响因素,以及如何降低噪声对电路性能的影响。

10.非线性效应:介绍了非线性效应的基本原理、产生原因和影响,以及如何利用非线性效应实现特定的功能,如混频器、乘法器和倍频器等。

通过学习这些知识点,读者可以掌握模拟CMOS集成电路设计的基本原理、技术和方法,为进一步深入研究和实际应用打下坚实的基础。

基于0.6μm CMOS工艺的限幅放大器设计

缸n T sl t ma ie  ̄ p sdo a hp b f la pl e el o p el n f e a ol t n cr t hi hi i 瞻 ni pl ri cm oe f n ut u e: n i r l ut c l a do s t n c l i i uiW l t f s i f c s ut s C ao c e

o e i a s6 : b/ ti i 唐 w pl rak ip y  ̄ c I ̄e o 7 B d rvd s a o s nto tut p mt g t i 2 n  ̄4 s hs ni l n  ̄ l  ̄s a n utd n ni t f4 d a p ie c n  ̄ up n ir n o

关键 词 : 接 收机 : 放大 器 ; 光 主 限幅放 大器 ; l O I 艺 Cl S V 中图分类 号 :I 2 " 4 N9 文献 标识码 : A 文 章编 号 :17 .0 02 0 )0 0 &0 6 36 6 (0 6 Z0 5 4

A i iig Am fe e in asn n CM S T c L t n n Pl rD sg ofB ig o i t 0 e hnis c

维普资讯

第 3卷 4

第 2 期

河 南 科 技 学 院 学 报 ( 科 学版 ) 自然

一种高性能CMOS集成运算放大器的研究与设计

中折 叠式 功耗大 、 噪声 较高 , 所 以第 一级 电路 使用 了

套筒式 的共源共 栅结构 。 同时, 由 于 NMOS管 比

噪 比以及 解析 度等 。 设计 电路 要 同时兼顾 相位 裕 度 、

线性 度 、 带宽、 噪声 、 增益 等多 种指标 非 常 困难 , 要 依 据实 际情 况有 取有 舍 。本文设 计 的运算 放大 器考 虑 噪声 性 能及保 持一 定 的线性 度 ; 同时 , 考虑带 宽 及增

一

种高性 能 C MO S集成运算放大器的研究与设计

李 冰冰 , 杨 明

1 . 淮北职 业技 术学 院 电子信息 系 , 安徽 淮北 , 2 3 5 0 0 0 ; 2 . 亳州 师 范高等 专科 学校 理化 系 , 安徽 亳州 , 2 3 6 8 0 0

摘要 : 利 用 微机 电技 术 , 使用 0 . 1 8微 米 的 C MO S工 艺 , 实现 了一 种 新 型 的 全 差 分 结 构低 噪 声 运 算放 大 器 , 供 电 电压

V D D

放 大 电路 的输 出发 生偏 差 , 造 成 测量 误 差 或使 系统

发送 错误 动 作 。这 些影 响多 为噪声 , 因此 , 在 特定 条 件下( 如 高灵 敏 度 ) , 噪 声 干扰 仍 然是 一 个 不 可 回避 的问题 , 本 文采 用 C M0 S工 艺设计 了一个 低 噪声 运 算 放大 器 。 主要对 噪声 进行 优化 。

况下, 若 要带 动 小负 载 , 选 择 共 源 级 已可满 足 , 其 另

一

益 。基于 以上 分析 , 设计 采用 两级 运放 比较 合适 , 初

步 的主 电路 如 图 1所示 。 . 由于电路 的 等效输 入噪 声是输 出 噪声 比上 运放 的增 益 , 因而 运用 共 源 共栅 结 构 可大 大 提 高运 放 的

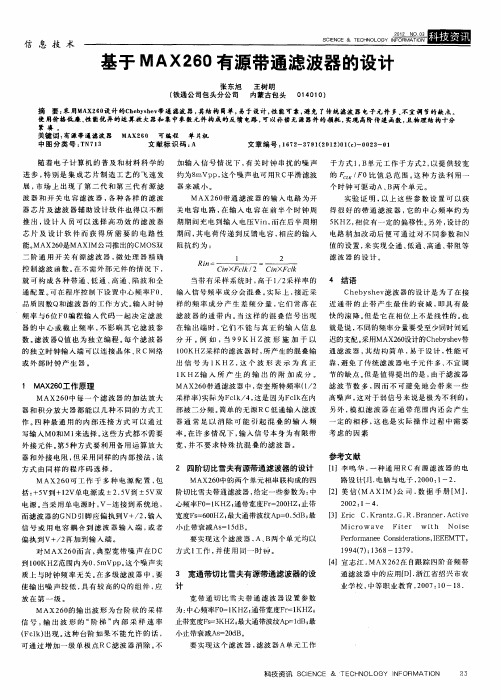

基于MAX260有源带通滤波器的设计

SC TNG CE EOY I &CL E HO. N

匪圈

基于 MAX2 0有源带通滤波器的设计 6

张东 旭 王树 明 ( 铁通 公司包 头分 公司 内蒙 古包头 0 O ) 1 1 4 0 摘 要 : 用M X 6  ̄ 计 的C ey h v 采 A Z0t h b s e 带通 滤波 器 , 其结构 简单 , 易于设 计, 能可靠 , 免 了 统滤波 器电子元 件 多 不 宜调 节的缺 点。 性 避 传 使 用价格低 廉 , 能优异 的运 算放 大器和集 中参 数元件 构成的反馈 电路 , 以补偿 无源器件 的损耗 , 性 可 实现 高阶 传递函数 , 物理 结构十分 且

滤 波 节数 多 , 因而 不 可 避 免 地 会 带 来一 些 高 噪 声 , 对 于 弱信 号 来 说 是极 为 不 利 的 ; 这 另外 , 拟 滤 波 器在 通 带 范 围 内还 会 产 生 模

一

MAx2 O 每 一 个 滤 波 器 的 加 法 放 大 采 样 率 ) 际 为F l / , 是 因 为F l 在 内 6中 实 ck 4 这 ck

简单 的 无 源RC低通 输 入 滤 波 器 和 积 分 放 大 器都 能 以几 种 不 同的 方式 工 部 被 二 分 频 。

M AX 6 带 通 滤 波 器 的输 入 电路 为开 20 关 电容 电 路 , 输 入 电容 在 前 半 个 时 钟 周 在

期 期 间 充 电到 输 入 电压 V n, i 而在 后 半 周 期 5 KHz 相 位 有一 定 的偏 移性 。 , 另外 , 计的 设

芯 片 及 设 计 软 件 而 获 得 所 需 要 的 电路 性 期 间 , 电荷 传 递 到 反 馈 电容 , 应 的输 入 其 相

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于CMOS全差分运算放大器的全集成有源滤波器的设计

_解读

全集成有源滤波器是一种基于CMOS全差分运算放大器的滤波器设计,通过集成电路的方式实现滤波器的功能。

CMOS全差分运算放大器具有低

功耗、高增益、高输入阻抗和低输出阻抗的特点,适合用于滤波器设计。

在全集成有源滤波器的设计中,首先需要确定滤波器的类型和性能要求,包括截止频率、通带增益、阻带衰减等。

选择合适的滤波器类型可以

根据实际应用需求,常见的有低通滤波器、高通滤波器、带通滤波器和带

阻滤波器等。

以设计一个低通滤波器为例,设计流程如下:

首先确定滤波器的截止频率。

截止频率是滤波器的特征参数之一,决

定了滤波器的频率响应。

根据实际需求选择合适的截止频率。

然后确定滤波器的阶数。

滤波器的阶数决定了滤波器对信号的衰减速度。

一般而言,阶数越高,滤波器的陡峭度越高,但相应的设计复杂度也

增加。

根据实际需求选择合适的阶数。

接下来根据截止频率和阶数的要求,可以利用标准滤波器设计方法进

行设计。

常用的设计方法有巴特沃斯法、切比雪夫法、椭圆法等。

每种方

法的特点和性能各有不同,根据实际需求选择合适的设计方法。

设计完成后,需要根据选择的CMOS全差分运算放大器,进行电路图

设计和电路参数计算。

CMOS全差分运算放大器的电路图包括输入级、差

动放大级和输出级等。

通过合理的设计和参数选择,实现所需的滤波器增

益和频率特性。

最后,进行电路模拟和性能分析。

利用仿真工具对设计的滤波器进行

电路模拟和分析,验证滤波器的性能是否符合预期要求。

如果需要,可以

进行电路参数的微调和优化。

总结起来,基于CMOS全差分运算放大器的全集成有源滤波器的设计

是一个系统性的工程,包括滤波器类型选择、截止频率和阶数的确定、设

计方法选择、电路图设计和电路参数计算等。

通过合理的设计和参数选择,可以实现满足实际应用需求的滤波器。