SoC架构

存算一体芯片 电路 架构设计

存算一体芯片电路架构设计

存算一体芯片(SoC)是一种集成了存储和计算功能的芯片,它

的设计架构对于实现高性能和低功耗至关重要。

在存算一体芯片的

电路架构设计中,需要考虑如何有效地集成存储和计算单元,以及

如何优化其性能和功耗。

首先,存算一体芯片的电路架构设计需要考虑存储和计算单元

之间的紧密集成。

这意味着存储单元(如内存)需要与计算单元

(如处理器)之间建立高速、低延迟的连接,以便实现快速的数据

传输和处理。

在电路设计中,可以采用高速总线、片上互连(interconnect)等技术来实现存储和计算单元之间的高效通信。

其次,电路架构设计还需要考虑如何优化存算一体芯片的性能

和功耗。

为了提高性能,可以采用多核处理器设计、硬件加速器等

技术来加速计算任务。

同时,还可以采用高效的存储器层次结构、

数据预取技术等来提高存储访问性能。

而为了降低功耗,可以采用

动态电压调节(DVFS)、低功耗设计技术等来实现节能。

此外,存算一体芯片的电路架构设计还需要考虑安全性和可靠性。

在设计中可以采用硬件加密、安全启动技术等来保护数据安全,

同时还需要考虑容错设计、错误检测与纠正技术等来提高芯片的可靠性。

综上所述,存算一体芯片的电路架构设计需要综合考虑存储和计算单元的紧密集成、性能和功耗的优化,以及安全性和可靠性的需求。

通过合理的电路架构设计,可以实现高性能、低功耗、安全可靠的存算一体芯片,满足日益增长的计算需求。

soc设计知识点总结

soc设计知识点总结SOC(System on Chip)指的是在一个芯片上集成了一系列功能模块,包括处理器、存储器、I/O接口等,使得整个系统可以在一个单一的芯片上完成。

SOC设计是现代集成电路设计的重要领域,本文将对SOC设计的关键知识点进行总结。

一、SOC设计概述SOC设计是一项综合性工程,涉及到多个学科和技术领域。

在SOC设计过程中,需要考虑以下几个核心要素:1. 系统架构设计:确定系统的功能需求和整体结构,包括处理器的选择、总线结构、存储器层次结构等。

2. IP核集成:选择合适的IP核并进行集成,对SOC的功能和性能起到关键作用。

IP核可以是自己设计的,也可以是从第三方获取的。

3. 性能优化:通过对系统进行优化,提升其性能表现。

优化可能涉及到处理器架构、存储器等方面。

4. 功耗管理:SOC设计中功耗管理是一个重要的问题,需要采取适当的手段减少功耗,以实现低能耗的设计。

5. 验证和调试:验证设计的正确性和性能是否满足需求,并进行调试修复问题。

二、SOC设计中的关键技术1. 处理器架构:SOC设计中处理器的选择和架构设计是一个重要的决策。

常见的处理器架构有ARM、MIPS等,选择适合应用场景的处理器架构可以提高系统性能。

2. 存储器层次结构:SOC设计中存储器的选择和层次结构的设计对系统性能有着重要影响。

常见的存储器包括寄存器、高速缓存、SDRAM等,通过合理的存储器层次结构设计可以提高系统的存取速度。

3. 总线设计:SOC中各个模块之间的通信需要通过总线来实现。

总线设计需要关注带宽、延迟、支持的传输协议等方面,合理的总线设计可以提高系统的性能。

4. 通信接口设计:SOC设计中的I/O接口设计对于系统的外部通信起到重要作用。

常见的接口包括UART、SPI、I2C等,通过设计高效的接口可以提高系统的数据传输速率。

5. 时钟和时序设计:SOC设计中需要考虑各个模块之间的时钟同步和时序关系。

合理的时钟和时序设计可以确保系统正常工作,避免由于时序问题而引起的故障。

TI推出面向通信基础局端设备的新型多核SoC架构

Wi X、WCD MA MA 以及最 新 开发 的 L E技术 。今 年 2月 T

推出以来 ,基于新型多内核 、多层 S C 架构的产 品系列 已 o

在开发 工具上也投 入了很 多。一方面为客 户带来了业 界效 经在全球被超过 4 0多项设计采用 ,其 中仅 基于新型架构 的

率最 高的编译器 ,因而能够提供 更高价值 的产品 ; 另一方 4核基站器件就有 2 0多项设计被采纳 ,这些设计有 的是在

面还提供 调试工具 的支持 ,使开 发人 员能够 深入到程序 的 样片还没有 出来之前就被 设计进 去了 ,这可以看出 T 芯片 I 具体执 行内部发现 问题 、找 出问题。可实现跨 越式起步 的 的被认可度。 圆

L … … 一 ∞ m

T 多 内核 S C架构 I o

对于市场对 T 芯片 的认可情况 ,K tyB o I ah rwn表示 ,

术: 多核 导航器 , 它支持 内核与存储器存取之问的直接通信 , 目前 T 每 个季度 有关 WCD I MA的芯 片发货 量基本 上都超

从而解放外设存取 ,充分释放多核性能 ; 片上 交换架构—— 过 1 0万片 ,第 1代器件 ( O 采用 9 n 0 m工艺 )和第 2代器

现今 ,无 线网络数据 的增长对通信基础局端 设备产生

了许多新的需求 : 一是降低功耗。基站设备是 7天 2 4小时

运 行的 ,能源 消耗 较大 ,白天繁忙时 与晚上相对空 闲时对

功 率 的 要 求 不 同 ; 是 异 构 网 络 。 因 存在 不 问形 式 的基 站 , 二

大 大小小的基站 ; 三是 需要 MI MO功能 、优化 的矩 阵处理 环境 的接收机 ; 四是频谱效 率要 高 ; 五是投 资成本与运 营 成本 的降低。正是基于 这样的趋 势和挑战 ,T 开发 了面向 l 通信基础局端设备的新型多核 S C架构。 o K tyB o ah rwn女 士 介绍 说 ,新 S C采 用 C x内核 , o 6 无线基站层 1 、层 2、层 3协处理器 ,和 丰富 的独立片 内连 接层 的技术 。此 外更重要的是 T 有 支持 无线基站领先的技 l

2023年集成电路系统级芯片SoC设计企业组织架构和部门职能

2023 年集成电路系统级芯片SoC 设计企业组织架构和部门职能17、市场工程部 (6)18、综合行政部 (6)19、综合行政中心 (6)20、人力资源部 (6)21、财务部 (6)22、行政部 (6)23、客服部 (6)24、网络部 (7)25、商务部 (7)26、生产部 (7)27、工程进展部 (7)28、证券事务部 (7)29、内审部 (7)一、公司组织架构二、部门主要职能股东大会为公司的最高权力机构,董事会对股东大会负责,总经理对董事会负责,监事会是公司的监视机构,对公司董事、总经理及其他高级治理人员行使监视职能;公司设董事会秘书,执行三会决策事项及工作,对董事会负责。

董事会下设战略委员会、提名委员会、薪酬与考核委员会、审计委员会。

总经理下设IC 设计中心、应用设计中心、市场中心、综合行政中心等职能部门,担当研发治理、市场营销、综合治理等职能。

1、IC 设计中心统筹和治理规律设计部、模拟设计部等下属部门的工作。

2、规律设计部负责芯片的全部数字规律电路设计工作。

3、专利事务部负责公司的制造、有用型等专利申请及维护工作。

4、预研部负责公司芯片算法争论。

5、模拟设计部负责芯片的全部模拟电路设计。

6、后端设计部负责集成电路物理设计。

7、应用设计中心统筹和治理嵌入式软件部、软件工具部等各下属部门的工作。

8、嵌入式软件部负责公司芯片应用开发、软件开发、软件系统架构设计等。

9、软件工具部负责公司软件工具的研发。

10、硬件部负责公司全部产品、样机、工具的原理图及印制电路板设计。

11、技术部负责公司产品技术实现的算法设计研发。

12、核心工具部负责公司开发工具、编译器的研发。

13、应用测试部负责公司全部产品、工程、软件开发工具包的功能及性能测试。

14、移动平台软件部负责公司APP移动平台软件研发。

15、市场中心统筹和治理市场营销部、市场工程部等各下属部门。

16、市场销售部负责公司产品销售及客户维护。

17、市场工程部负责公司客户方案支持及效劳。

基于DVFS 技术的SOC 架构分析

1低功耗概述随着IC设计规模越来越大,芯片的功能也越来越强大;同时芯片的功耗问题也成为了芯片设计的重点问题:如何降低在芯片正常工作时的功耗,如何降低芯片在不同工作场景中的功耗,成为了越来越多设计人员棘手的问题。

低功耗技术对当今终端芯片的成功至关重要。

从器件到整机、从模块到芯片、从系统架构到软硬件实现、从前端设计到后端实现,人们一直在坚持不懈地改进低功耗技术。

无论采取什么样的低功耗技术,最终的目的都是:1)在模块、芯片、器件、整机工作的时候,降低基于DVFS技术的SOC架构分析段维虎,卢海涛(广州众诺电子技术有限公司)摘要:本文概述了低功耗设计技术在芯片设计中的重要地位,并且对主要关键技术动态电压频率调整(DVFS)进行了简要介绍,并对基于DVFS技术的芯片的片上系统(SOC)架构实现做了实例分析。

关键词:低功耗,DVFS,电源分区,电压分区SOC architecture analysis based on DVFS technologyDUAN Wei-hu,LU Hai-tao(Guangzhou zhono electronic technology co.,LTD)Abstract:In this paper,the important position of low power design technology in chip design is summarized,and the main key technology DVFS is briefly introduced.keywords:lowpower;DVFS;powerdomain;voltagedomain它们的工作功耗(也称为动态功耗)2)在模块、芯片、器件、整机不工作的时候,降低它们的漏电功耗(也称为静态功耗)。

芯片功耗发展趋势如图1所示,从图1中可知,芯片功耗增加基本是指数级,而目标功耗基本是保持不变,或者需要更低;芯片的各部分功耗都在增加,但静态功耗增加的更快。

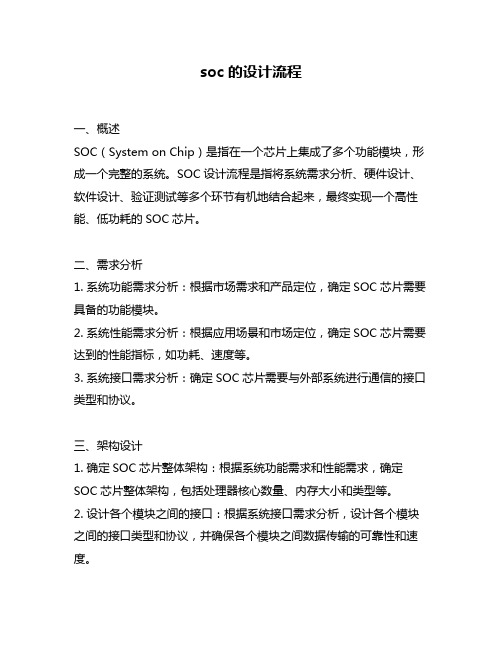

soc的设计流程

soc的设计流程一、概述SOC(System on Chip)是指在一个芯片上集成了多个功能模块,形成一个完整的系统。

SOC设计流程是指将系统需求分析、硬件设计、软件设计、验证测试等多个环节有机地结合起来,最终实现一个高性能、低功耗的SOC芯片。

二、需求分析1. 系统功能需求分析:根据市场需求和产品定位,确定SOC芯片需要具备的功能模块。

2. 系统性能需求分析:根据应用场景和市场定位,确定SOC芯片需要达到的性能指标,如功耗、速度等。

3. 系统接口需求分析:确定SOC芯片需要与外部系统进行通信的接口类型和协议。

三、架构设计1. 确定SOC芯片整体架构:根据系统功能需求和性能需求,确定SOC芯片整体架构,包括处理器核心数量、内存大小和类型等。

2. 设计各个模块之间的接口:根据系统接口需求分析,设计各个模块之间的接口类型和协议,并确保各个模块之间数据传输的可靠性和速度。

3. 选择合适的IP核:选择已经存在并且经过验证测试的IP核,并对其进行修改或优化以满足系统需求。

四、芯片设计1. 电路设计:根据架构设计,对各个模块进行电路设计,包括时钟、功耗、噪声等。

2. 物理布局:将电路设计转换为实际的物理布局,包括芯片大小和引脚分配。

3. 物理验证:通过模拟和仿真等方法验证物理布局的正确性和可靠性。

五、软件设计1. 驱动程序编写:编写各个模块的驱动程序,以保证系统的正常运行。

2. 操作系统移植:将操作系统移植到SOC芯片上,并进行适当修改以满足系统需求。

3. 应用程序开发:根据用户需求开发相应的应用程序。

六、验证测试1. 仿真验证:通过仿真工具对SOC芯片进行功能验证和性能评估。

2. 硬件验证:通过硬件测试工具对SOC芯片进行实际测试,包括功耗测试、时序测试等。

3. 软件验证:通过软件测试工具对驱动程序和应用程序进行测试。

七、封装与生产1. 封装设计:将SOC芯片封装成符合标准的封装形式,如BGA或QFP等。

soc芯片开发方法

soc芯片开发方法随着科技的快速发展,soc(System On Chip)芯片已成为现代电子设备中不可或缺的核心部件。

它集成了多种功能模块,为各类电子产品提供了强大的处理能力。

本文将详细介绍soc芯片的开发方法,帮助读者了解这一领域的相关知识。

一、soc芯片概述soc芯片,即系统级芯片,是将多种功能模块集成在一块芯片上的高度集成化产品。

它具有高性能、低功耗、小尺寸等特点,广泛应用于智能手机、平板电脑、可穿戴设备等领域。

二、soc芯片开发流程1.需求分析在soc芯片开发初期,首先要进行需求分析,明确芯片的应用场景、性能指标、功耗要求等。

需求分析是整个开发过程的基础,对后续设计工作具有指导意义。

2.架构设计根据需求分析,设计soc芯片的架构。

这包括处理器核心、内存、外设接口、电源管理模块等。

架构设计要充分考虑性能、功耗、面积等多方面因素,力求实现最优的平衡。

3.逻辑设计在架构设计的基础上,进行逻辑设计。

逻辑设计主要包括各功能模块的详细设计、接口定义、时序分析等。

这一阶段需要使用硬件描述语言(如Verilog、VHDL等)进行描述。

4.仿真验证在逻辑设计完成后,需要进行仿真验证,确保设计的正确性和可靠性。

仿真验证主要包括功能仿真、时序仿真和功耗仿真等。

5.物理设计物理设计是将逻辑设计转化为实际电路的过程,主要包括布局、布线、版图绘制等。

这一阶段要考虑信号完整性、电源噪声、热效应等因素,确保芯片的性能和可靠性。

6.制造与测试将设计好的soc芯片发送至晶圆代工厂进行制造。

制造完成后,进行封装、测试,确保芯片的质量和性能符合预期。

三、soc芯片开发方法1.模块化设计模块化设计是soc芯片开发的核心方法。

通过将复杂的功能划分为多个独立的模块,降低设计复杂度,提高开发效率。

2.面向复用设计面向复用设计是指在设计过程中,充分考虑已有资源的复用。

这有助于缩短开发周期,降低成本。

3.高级综合高级综合是将高级描述语言(如C、C++等)转化为硬件描述语言的过程。

soc设计知识点总结

soc设计知识点总结一、芯片架构设计1. 总线结构设计总线是芯片内各个功能模块间进行数据传输和通信的基础设施,是整个系统的“血管”系统。

在设计SOC时,需要考虑总线的带宽、延迟、复用性等因素,以满足各个功能模块之间的数据传输需求。

2. 存储器系统设计存储器系统包括内存子系统、缓存子系统和存储控制器等部分。

在SOC设计中,需要考虑存储器系统的容量、访问速度、数据一致性、功耗等因素,确保系统具有良好的性能和低功耗。

3. 电源管理电源管理是SOC设计中非常重要的一个方面,它涉及到芯片的功耗控制、电源分配和管理、时钟管理等。

在SOC设计中,需要考虑如何设计有效的电源管理方案,以降低芯片的功耗,并提高系统的稳定性和可靠性。

4. 硬件安全硬件安全是SOC设计中一个非常重要的方面,它涉及到如何设计安全的硬件结构,如何保护系统不受恶意攻击和非法访问。

在SOC设计中,需要考虑如何设计安全的存储器结构、综合电路结构、加密解密和安全存储等功能,以提高SOC系统的安全性。

5. 集成测试在SOC设计中,集成测试是非常重要的一个环节,它涉及到如何验证各个功能模块的正确性和功能完整性,以及各个功能模块之间的协同工作。

在SOC设计中,需要设计有效的集成测试方案,包括逻辑仿真、时序仿真、功能仿真、硬件验证和验证等环节,以确保SOC系统具有良好的稳定性和可靠性。

二、处理器设计1. CPU核心设计CPU核心是SOC设计中的核心部分,它负责控制整个系统的运行和数据处理。

在SOC设计中,需要考虑如何设计高性能的CPU核心,包括指令集架构、流水线结构、指令级并行执行、分支预测等技术,以提高CPU核心的性能和效率。

2. 浮点运算单元设计浮点运算单元是处理器设计中的另一个重要部分,它负责处理浮点运算指令。

在SOC设计中,需要考虑如何设计高性能的浮点运算单元,包括浮点运算指令集、寄存器文件、乘法器、除法器等功能部件,以提高浮点运算单元的运算速度和精度。

到底什么是Cortex、ARMv8、arm架构、ARM指令集、soc?一文帮你梳理基础概念【科普】

到底什么是Cortex、ARMv8、arm架构、ARM指令集、soc?⼀⽂帮你梳理基础概念【科普】前⾔有粉丝问我到底什么是ARM,搞不清楚Cortex、arm内核、arm架构、ARM指令集、soc这些概念都是什么关系,下⾯⼀⼝君给⼤家整理⼀下关于ARM相关的⼀些概念。

1、ARM既可以认为是⼀个公司的名字,也可以认为是对⼀类微处理器的通称,还可以认为是⼀种技术的名字。

2、ARM公司是专门从事基于RISC技术芯⽚设计开发的公司,作为知识产权供应商,本⾝不直接从事芯⽚⽣产,⽽是转让设计许可,由合作公司⽣产各具特⾊的芯⽚。

3、ARM处理器的内核是统⼀的,由ARM公司提供,⽽⽚内部件则是多样的,由各⼤半导体公司设计,这使得ARM设计嵌⼊式系统的时候,可以基于同样的核⼼,使⽤不同的⽚内外设,从⽽具有很⼤的优势。

下⾯我们针对这些概念,给⼤家逐⼀介绍。

ARM公司ARM⾸先是⼀个公司,即Advanced RISC Machines的缩写。

但是他本来并不叫这个名字,来看看ARM公司的成长历史。

1978年,⼀个名叫Hermann Hauser的奥地利籍物理学博⼠,还有他的朋友,⼀个名叫Chris Curry的英国⼯程师成⽴了⼀家名字叫“CPU”的公司。

这家CPU公司的全称,是Cambridge Processor Unit,字⾯意思是“剑桥处理器单元”。

CPU公司成⽴之后,主要从事电⼦设备设计和制造的业务。

他们接到的第⼀份订单,是制造赌博机的微控制器系统。

这个微控制器系统被开发出来后,称之为Acorn System 1。

之所以叫Acorn,就是因为他们想在电话黄页⾥排在Apple(苹果)公司的前⾯。

在Acorn System 1之后,他们⼜陆续开发了System 2、3、4,还有⾯向消费者的盒式计算机——Acorn Atom。

到了1981年,公司迎来了⼀个难得的机遇——英国⼴播公司BBC打算在整个英国播放⼀套提⾼电脑普及⽔平的节⽬,他们希望Acorn能⽣产⼀款与之配套的电脑。

专用SoC安全控制架构的研究与设计

芯片安全性影响重要程度和信息技术安全性评估准则口 ,

引 言

为 了满 足智 能 卡 和可 信 计 算 应 用 需 求 , 计 实 现 了 一 设

款 专 用 S C芯 片 … 。该 芯 片 由微 处 理 器 、 序 和 数据 存 储 o 程 器 及 管 理模 块 、 全 逻 辑 模 块 、 码 服 务 模 块 、 助 功 能模 安 密 辅 块 、/ 接 口组 成 , 为 各 种 安 全 应 用 提 供 机 密 性 、 整 性 I0 能 完

=

:

I

麓 曩 _ 嚣一 。 ¨ 嚣 … 。 煮 _鬻秘 - - 鬻黔 溅嬲 _ — _ 一 l 。一 譬

薯

一

专 用 S C 安 全 控 制 架 构 的研 究 与 设 计 o

杨 先 文 , 鲁 国 , 志 刚 张 田

( 放 军 信 息 工程 大学 电子 技 术 学 院 , 州 4 0 O ) 解 郑 5O 4

*

摘 要 :针 对 专 用 S C芯 片 的 安 全 问题 , o 在描 述 芯 片威 胁 模 型 与 部 署 模 型 的 基 础 上 , 划 了芯 片 资 源 的 安 全 等 级 , 计 了 规 设 芯 片的 3 作 状 态及 状 态转 移 之 间 的 约束 条 件 和 实现 机 制 , 出 了芯 片运 行 时 的 安 全 工 作 流 程 。对 芯 片 的 安 全 性 分 析 表 - 给

Ya i ng X anwe , Zha n ng Lug uo, Ti n a Zhi ng ga ( ns iu eofEl cr ni e h l y,PLA n or a i I tt t e t o cT c noog I f m ton Engne rn nve st i e i g U i r iy,Zhe gz u 4 00 n ho 50 4,Ch n i a) Ab tac :A i ig a e urt e e n o e so pe ilS sr t m n ts c iy r lva tpr bl m fs ca oC hi c p,ba e h hr a o la it i to od loft e c i i n, s d on t e t e tm de nd d s rbu in m e h h p gve c p r s r e r i d d it if r nts c iy lv l hi e ou c s a e dvie n o dfe e e urt e e s,a d t hi S wo kig s a ቤተ መጻሕፍቲ ባይዱ n m p e e a in o hec nsr i on to n hec p’ r n t t s a d i l m ntto ft o t antc diinsof

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SEP0718

系统与时钟控制

ARM11 RTC GPU

多媒体系统

VPU

VIC

TIMER

LCDC

HDMI

PMU

DMAC

MULTI-LAYER BUS

I2S

CODEC

外设与接口

SPI TOUCH

GPS系统

SDIO

PWM

存储系统

DDR2 NOR/SRAM/ SDRAM

UART

USB OTG

I2C

GPIO

– 指令长度可变 – 编译简单 – Intel

• RISC(Reduced Instruction Set Computer)

– 采用固定长度的指令格式,指令归整、简单、基本寻址方式有2~3种。 – 使用单周期指令,便于流水线操作执行。 – 大量使用寄存器,数据处理指令只对寄存器进行操作,只有加载/ 存储指 令可以访问存储器,以提高指令的执行效率。 – 编译复杂 – ARM、MIPS、PowerPC

31

SIMD、MIMD和向量处理器

• MIMD(Multiple Instruction Multiple Data):可以编写独立的程序并 运行在不同的处理器上,而且这些程序可以协同完成一个共同的大型 目标。 • SIMD(Single Instruction Multiple Data):对向量数据进行操作。例 如,一个单一的SIMD指令可以把64个数相加,只需要把64个数据流 发送到64个ALU,就可以在一个时钟周期内得到64个和。SIMD的优 点是所有并行执行单元都是同步的,它们都对同意指令作出响应。 • SIMD的一个更加古老和优雅的称呼是向量体系结构。

什么是SOC

• 片上系统(SoC:System-on-a-chip)指的是在单个芯片上集成一个 完整的系统,对所有或部分必要的电子电路进行包分组的技术。所谓 完整的系统一般包括中央处理器(CPU)、存储器、以及外围电路等。 • 片上系统技术通常应用于小型的,日益复杂的客户电子设备。例如, 声音检测设备的片上系统是在单个芯片上为所有用户提供包括音频接 收端、模数转换器(ADC)、微处理器、必要的存储器以及输入输出 逻辑控制等设备。此外系统芯片还应用于单芯片无线产品,诸如蓝牙 设备,支持单芯片WLAN和蜂窝电话解决方案。 • 由于空前的高效集成性能,片上系统是替代集成电路的主要解决方案 。SoC 已经成为当前微电子芯片发展的必然趋势。

20

指令集ISA要完成哪些工作?

• 以ARM为例

– 分支指令 – 数据处理指令

• • • • • 寄存器传送 算术运算 逻辑运算指令 比较指令 乘法指令

– 存储器访问指令

• Load/Store内存访问指令 • 批量Load/Store内存访问指令 • SWP操作指令

– SWI系统调用指令 – 状态寄存器访问指令

21

控制和数据通路

22

CPU基本概念

• • • • • • CISC与RISC 流水线技术 分支预测技术 乱序执行技术 标量与超标量处理器 SISD、MIMD、SIMD、SPMD和向量处理 器 • VLIW处理器

23

CISC与RISC

• CISC(Complex Instruction Set Computer)

PHY

13

Samsung 6410

14

Telechips 8900

15

Samsung S5PV210

16

芯片设计环境

SUN 大型服务器 工作站 ×14

深亚微米EDA软件

瘦客 户机 ×30

矢量信号源

逻辑分析系统

HP server×20

网络分析仪 频谱分析仪 可编程电源

6GHZ混合信号测试

17

芯片量产流程

SoC

1

目录

• • • • 1、什么是SOC 2、CPU 3、总线 4、系统控制模块

2

什么是SoC

Die裸片

PAD

逻辑单元

CPU 内核

Analog 静态RAM

3

几款SoC芯片的版图

SEP0718 65nm TSMC

累计流片20余 次10多种SoC芯 片 65nm,千万门 级设计经验

4

• 片上系统:SoC (System on Chip) • 具有知识产权的内核: IP核(Intellectual Property Core ) • 专用集成电路:ASIC(Application Specific Integrated Circuit)

•

• • •

•

•

CPU基本概念

• • • • • • • CISC与RISC 流水线技术 分支预测技术 乱序执行技术 标量与超标量处理器 SIMD、MIMD和向量处理器 VLIW处理器

28

分支预测技术

• 分支预测(Branch Prediction):是解决处理分支指令(if-then-else)导 致流水线失败的数据处理方法,由CPU来判断程序分支的进行方向,能够 加快运算速度。当包含流水线技术的处理器处理分支指令时就会遇到一个 问题,根据判定条件的真/假的不同,有可能会产生跳转,而这会打断流水 线中指令的处理,因为处理器无法确定该指令的下一条指令,直到分支执 行完毕。流水线越长,处理器等待的时间便越长,因为它必须等待分支指 令处理完毕,才能确定下一条进入流水线的指令。分支ห้องสมุดไป่ตู้测技术便是为解 决这一问题而出现的。分支预测技术包含编译时进行的静态分支预测和硬 件在执行时进行的动态分支预测。 • 最简单的静态分支预测方法就是任选一条分支。这样平均命中率为50%。 更精确的办法是根据原先运行的结果进行统计从而尝试预测分支是否会跳 转。任何一种分支预测策略的效果都取决于该策略本身的精确度和条件分 支的频率。 • 动态分支预测是近来的处理器已经尝试采用的技术。最简单的动态分支预 测策略是分支预测缓冲区(Branch Prediction Buff)或分支历史表( branch history table)。

什么是SOC

• IP核——(intellectual property core)全称知识产权核。 是指某一方提供的、形式为逻辑单元、芯片设计的可重用 模块。IP核通常已经通过了设计验证,设计人员以IP核为 基础进行设计,可以缩短设计所需的周期。[1]IP核可以通 过协议由一方提供给另一方,或由一方独自占有。IP核的 概念源于产品设计的专利证书和源代码的版权等。设计人 员能够以IP核为基础进行专用集成电路或现场可编程逻辑 门阵列的逻辑设计,以减少设计周期。 • ASIC——(Application Specific Integrated Circuit)特定 应用集成电路 让我们从特定应用集成电路(ASIC)开 始。这是因特定目的而创建的设备。这是一个完全或主要 部分是数字性质的芯片,任何模拟和混合信号功能是沿着 物理接口线(物理层)或锁相回路(PLL)的。ASIC通常 被设计和使用在特定系统中的单个公司。开发ASIC非常 昂贵、耗时、资源密集的,但ASIC确实能提供低功耗的 高性能。

24

处理器位宽

• 当前高性能嵌入式系统SoC的处理器多为32位处理器。所谓32位处理 器,即处理器内部的寄存器(包括地址寄存器与数据寄存器)位宽最 大为32位。低性能的嵌入式系统SoC一般多采用16位微控制器( micro-controllers),然而,随着工作负载的增加,此类系统逐渐开 始使用32位处理器。可以预见,在不久的将来,伴随高性能及超大存 储空间的需求,64位处理器将逐渐成为主流。

30

标量与超标量处理器

• 根据处理器的微架构设计,处理器可以分为标量(scalar)处理器与超标量( superscalar)处理器。 • 超标量处理器是指在处理器内核中实现了指令级的并发处理。这种技术能够 在相同的CPU主频下实现更高的CPU吞吐率(throughput)。处理器的内核 中一般有多个执行单元(或称功能单元),如算术逻辑单元、位移单元、乘 法器等等。未实现超标量体系结构时,CPU在每个时钟周期仅执行单条指令 ,因此仅有一个执行单元在工作,其它执行单元空闲。超标量处理器在一个 时钟周期可以同时分派多条指令在不同的执行单元中被执行,这就实现了指 令级的并行。超标量体系结构可以视作MIMD(多指令多数据)。

什么是SOC

CPU IP IP IP 系统控制 IP IP IP 接口外设 IP 总线 存储区域

IP

IP IP IP

SoC整体架构

CPU o BUS

外部存储器 控制器 EMI

系统控制模块

各种接口

9

CPU

一个CPU的外部端口都会有地址总线和数据总线,我们选择一种总线,把CPU和 这些外围IP连起来,让CPU可以和这些IP进行通讯,完成数据的计算和输入输出,这 样就变成了一个具有实际意义的系统了。 在这一点上,不同的厂商做法不同。 对于Intel而言,他是有晶圆的老大,也就是说,它的CPU由他自己设计好后入场 流片,生产好之后就诞生一个正方形的下面有很多针脚的东西,就是你们口中的CPU 了。它的内存控制器在主板上的北桥里面,而硬盘控制器网络控制器啥的都在主板上 的南桥。从这里可以看出,它的CPU和各类控制器都是分开的,因而面积大,功耗高 ,性能强。 ARM就不一样,首先ARM属于无晶圆。什么意思?就是ARM自己不会去流片,想用 ARM的CPU怎么办?直接购买授权,而后ARM就直接把它的CPU的源代码发给你了。我们 实验室就有ARM7和ARM11的源代码,这些代码我也读过不少。从这点来说,ARM的确胆 子很大。 ARM的功耗较低面积较小,所以各大厂商通常会把它的CPU和各类外围IP都放到一 起,然后自己拿着图纸去流片,生产出来的也是一个正方形,下面有很多引脚,这个 东西不仅包含了CPU,还包含了其他的控制器,这个东西就叫做SOC(system on chip) 。因特尔绝对不会给你看它的RTL代码,只会给你他芯片的spec。 所以目前各大厂商所做的事情,就是买来ARM的授权,得到ARM处理器的源代码, 而后自己搞一些外围IP(或者买或者自己设计),组成一个SOC后,去流片。不同的SOC ,架构不同(就是CPU如何和IP联系起来,有的以总线为核心,有的以DDR为核心), 当然,厂商会对SOC里面的ARM核做一些小的修改。