数字电路2

数电讲义--2章

1.0

VOL(max)0.5

输入标 准低电

平

0.4V

VNL

D VNH

E

V V 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0

SL VOFF VON

SH

Vi (V)

输入标准

高电平

2. 输入特性

+VCC

1) 输入伏安特性

iI

R1 3kΩ

1

-1.6 mA

<50 uA vI A

31

B

T1

1.4 V

和边沿,T4放大。 VO随iOH变化不大。 当由i于Oi以OHH受↑:线时功性,R耗变4上的化压限。降制增,大i0,H过T大3 、会T4烧饱毁和T,4管V,O随所

功耗 1mW IOH 400 A

输出高电平时的扇出系数 3.6V

R2 750Ω 2T3 Vc2 1 3 R4

VO

+VCC

R 4 +5V 100Ω

抗干扰能力越强。 高电平噪声容限

VNH= VSH ¯ VON 。

VNH越大,输入为1态下

抗干扰能力越强。

Vo (V)

4.0 A B

3.5

3.0

VOH(min)2.5 2.4V

C

2.0

1.5

A(0V, 3. 6V) B(0.6V, 3.6V) C(1.3V, 2.48V) D(1.4V, 0.3V) E(3.6V, 0.3V)

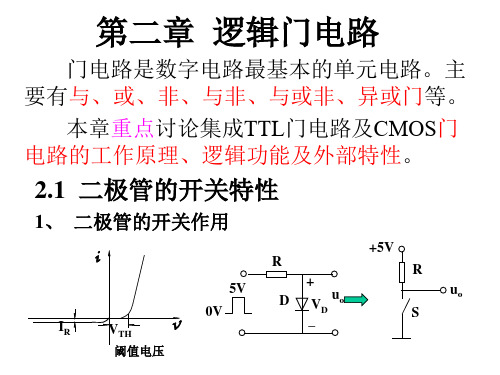

• 导通(VD>VTH) • 2、二极管的开关时间

截止5V(VDR<VT+H)

0V

D VD

uo

_

VF Vi

二极管开关状态的转换需要时间:

t1 t2

数字电路与逻辑设计(第二版)章图文 (2)

第2章 组合逻辑电路

2.1 集成门电路 2.2 组合逻辑电路的分析和设计 2.3 组合逻辑电路中的竞争-冒险

第2章 组合逻辑电路

2.1 集成门电路

2.1.1 TTL门电路 TTL门电路由双极型三极管构成,它的特点是速度

快、抗静电能力强、集成度低、功耗大,目前广泛应用 于中、小规模集成电路中。TTL门电路有74(商用) 和54(军用)两大系列,每个系列中又有若干子系列,例 如,74系列包含如下基本子系列:

4)传输延时tP 传输延时tP指输入变化引起输出变化所需的时间,它 是衡量逻辑电路工作速度的重要指标。传输延时越短, 工作速度越快,工作频率越高。tPHL指输出由高电平变 为低电平时,输入脉冲的指定参考点(一般为中点)到 输出脉冲的相应指定参考点的时间。tPLH指输出由低电 平变为高电平时,输入脉冲的指定参考点到输出脉冲的 相应指定参考点的时间。标准TTL系列门电路典型的 传输延时为11ns;高速TTL系列门电路典型的传输延时 为3.3ns。HCT系列CMOS门电路的传输延时为7ns;AC 系列CMOS门电路的传输延时为5ns;ALVC系列CMOS 门电路的传输延时为3ns。

第2章 组合逻辑电路

图2―2和图2―3分别给出了TTL电路和CMOS电 路的输入/输出逻辑电平。

当输入电平在UIL(max)和UIH(min)之间时,逻辑电路可 能把它当作0,也可能把它当作1,而当逻辑电路因所接 负载过多等原因不能正常工作时,高电平输出可能低于 UOH(min),低电平输出可能高于UOL(max)。

第2章 组合逻辑电路

74AC和74ACT:先进CMOS(Advanced CMOS)。 74AHC和74AHCT:先进高速CMOS(Advanced High speed

电子科大数字电路课件2-2补码chenyu

Diminished Radix – Complement Representation

[ 基数减1补码表示法(反码)]

The Diminished Radix – Complement of an n-digit number is obtained by subtracting it from r n -1 [ n位数的反码等于从 r n – 1 中减去该数] Example : Table 2-4 ,2-5 P.36 (r-1)’s Complement = r

1、1011100010112= 5613

8=

B8B

16

2、 ( 156 )10 = ( 10011100

)2

3、将0.3910转换为二进制数,要求精度达到10%。 0.3910转换为二进制数 要求精度达到10% 转换为二进制数, 10%。

0.01102

Review of the last lesson

(若约定字长是一个字节,试求-11910的补码表示。)

• +11910=011101112,as formula(公式): • 2n-D= (2n-1-D)+1 • 28-1: 11111111 subtract(减去)+119; -0 1 1 1 0 1 1 1 • 1 0 0 01 0 0 0 • plus(加)1: + 1 • -11910: 1 0 0 0 1 0 0 12

Binary to Decimal Based on definitions:

00110110 2 = 25 + 2 4 + 2 2 + 21 = 5410

0.00110110 2 = 2 + 2 + 2 + 2 = 0.210937510

电子线路基础数字电路试验2TTL与非门逻辑功能及参数测试

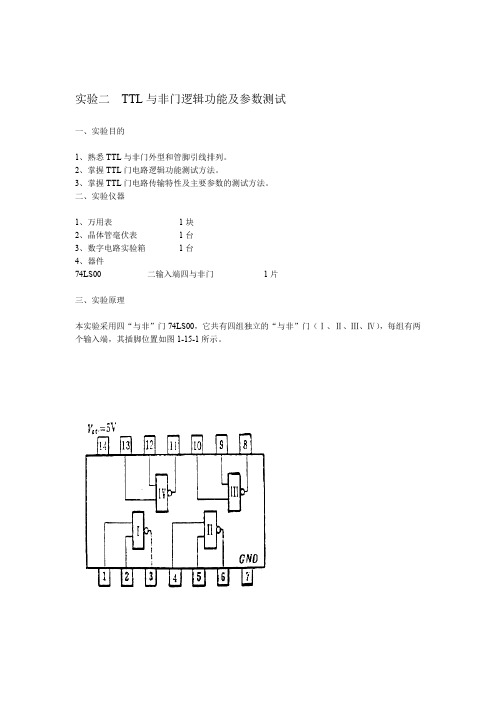

实验二TTL与非门逻辑功能及参数测试一、实验目的1、熟悉TTL与非门外型和管脚引线排列。

2、掌握TTL门电路逻辑功能测试方法。

3、掌握TTL门电路传输特性及主要参数的测试方法。

二、实验仪器1、万用表1块2、晶体管毫伏表1台3、数字电路实验箱1台4、器件74LS00 二输入端四与非门1片三、实验原理本实验采用四“与非”门74LS00,它共有四组独立的“与非”门(Ⅰ、Ⅱ、Ⅲ、Ⅳ),每组有两个输入端,其插脚位置如图1-15-1所示。

图1-15-1 74LS00引线排列图1-15-2 74LS00与非门(一组)每组的构造和逻辑功能相同。

现以其中一组说明如下:TTL与非门电路如图1-15-2所P AB “与非”TTL。

为输出端。

逻辑功能为P为“与非”门的二个输入端,B和A示。

.门的主要参数有:1、扇入系数N和扇出系数N:能使电路正常工作的输入端数目称为扇入系数N,电i0i路正常工作时能带动的同类门的数目称为扇出系数N。

02、输出高电平V:一般V≥3V。

OHOH3、输出低电平V:一般V≤0.3V。

OLOL4、电压传输特性曲线,开门电平V和关门电平V:图1-15-3所示之V~V关系曲0ONOFFi线称为电压传输特性曲线。

使输出电压V刚刚达到低电平V时的最低输入电压V称为开i0OL门电平V。

使输出电压V刚刚达到高电平V时的输入电压V称为关门电平V。

OFFOHON0i图1-15-3 电压传输特性曲线图1-15-4 输出波形延迟于输入波形5、输入短路电流I:一个输入端接地,其它输入端悬空时,流过该接地输入端的电流RD为输入短路电流I。

RD6、空载导通功耗P:指输入全部为高电平输出为低电平时的功率损耗。

ON7、空载截止功耗P:指输入为低电平输出为高电平时的功率损耗。

OFF8、抗干扰噪声容限:电路能够保持正确的逻辑关系所允许的最大干扰电压值,称为噪声容限。

其中输入低电平时的噪声容限为V=V-V,而输入高电平时的噪声容限为ILNLOFF V=V-V。

数字电子技术 (2)

杂质硅的原子图象和能带图 a) N型半导体 b) P型半导体

半导体 N型 P型

所掺杂质 施主杂质 受主杂质

多数载流子 (多子) 电子 空穴

少数载流子 (少子) 空穴 电子

特性

电子浓度nn≥空 穴浓度pn

电子浓度np≤空 穴浓度pp

PN结

1. PN结的形成

—— 空穴

—— 电子 —— 受主离子 —— 施主离子

Vbe

Vbc

截止 反偏 反偏, ib=ic =0,开关断开。 放大 正偏 反偏, ic = βib, 线性放大。 饱和 正偏 正偏, ib >Ibs , 开关闭合。

Vcc Vces ib I bs RC

,

Vces 0.7V

双极型三极管开关等效电路(理想情况下)

开关 闭合

当VI为高电平VIH时, T饱和

v1 VEE v B v1 R1 R1 R2

总结: 1. V1=V1L=0V 时 ,Vbe= -2V, 此时加在b-e结上的是反向电压,T可靠截止; ic=0, Vo= Vcc =VoH=5V

2. V1=V1H=5V 时 , Vbe=1.8V>VON , T导通,

是否深度饱和? V VON ib cc 0.44 mA RB

(2) 关闭时间toff 三极管从饱和到截止所需的时间。 toff = ts +tf ts :存储时间(几个参数中最长的;饱和越深越长) tf :下降时间

toff > ton 。 开关时间一般在纳秒数量级。高频应用时需考虑。 四. MOS管的开关特性(调到3.5节前讲)

§3—3 最简单的与、或、非门电路

0V 5V

D2 D 1

+VCC (+5V) R 3kΩ

数字逻辑与数字集成电路第2版

CATALOGUE

06

平均无故障时间、平均修复时间、可用性等,这些指标用于衡量数字系统的可靠性水平。

采用冗余设计、容错技术、故障检测与恢复机制等手段,提高数字系统的可靠性,确保系统稳定运行。

设计方法

可靠性指标

故障诊断

通过监控系统的运行状态、分析异常数据等方式,快速定位故障原因,为故障排除提供依据。

详细描述

总结词

可编程逻辑器件是一种可以通过编程实现各种数字逻辑功能的集成电路。

详细描述

可编程逻辑器件是一种可以通过编程实现各种数字逻辑功能的集成电路。它由可编程的逻辑门电路组成,用户可以通过编程来配置这些门电路的连接和参数,从而实现所需的数字逻辑功能。常见的可编程逻辑器件包括可编程逻辑阵列(PLA)、可编程门阵列(FPGA)和复杂可编程逻辑器件(CPLD)等。由于其灵活性高、可重复编程的特点,可编程逻辑器件被广泛应用于数字系统设计、数字信号处理和嵌入式系统等领域。

数字系统设计

CATALOGUE

03

将数字系统设计分为逻辑抽象、功能抽象和行为抽象三个层次,以便更好地理解和设计复杂的数字系统。

抽象化设计

从系统总体功能和行为出发,逐步细化设计,直至完成每个最小单元的设计。

自顶向下设计

将复杂的数字系统划分为若干个相对独立、功能明确的模块,便于设计、调试和维护。

模块化设计

数字逻辑与数字集成电路第2版

contents

目录

数字逻辑基础数字电路基础数字系统设计数字信号处理数字通信与网络数字系统安全与可靠性

数字逻辑基础

CATALOGUE

01

03

逻辑表达式的化简

通过逻辑代数的基本定理和运算规则,将复杂的逻辑表达式化简为简单的形式,便于分析和理解。

数字电子技术 第2章 逻辑门

2

2.1

主要内容:

基本逻辑门

与、或、非三种基本逻辑运算

与、或、非三种基本逻辑门的逻辑功能

41

标准TTL门的输入 / 输出逻辑电平 :

42

CMOS门的输入 / 输出逻辑电平(+5V电源时) :

4.4V

0.33V

43

传输延迟时间tpd

t pd 1 (tPHL tPLH ) 2

tPHL和tPLH的定义(下图为非门的输入和输出波形) :

44

输入/输出电流 (1)“拉电流”工作状态 (2)“灌电流”工作状态

9

2.1.2 或门

实现“或”运算的电路称为或逻辑门,简称或门 。 逻辑或运算可用开关电路中两个开关相并联的例 子来说明

真 值 表

A 0 0 1 1

B 0 1 0 1

F A B

0 1 1 1

10

“或”运算的逻辑表达式为: F = A+B “或”逻辑的运算规律为:

一般形式

000 0 1 1 0 1 11 1

A

一般形式

A A A A 1 A A 0

14

非门的逻辑符号:

74LS04(六非门)

例2-5 : 向非门输入图示的波形,求其输出波形F。 解:

15

2.2 复合逻辑门

主要内容:

与非、或非、异或、同或的复合逻辑运算 与非门、或非门的逻辑功能 异或门、同或门的逻辑功能 各种复合逻辑门的真值表及输出波形

数字电子电路第二版电子课件第一章数字电路基础

§1—1 数字信号与数字电路

4

第一章 数字电路基础

当人们在超市购物结账付款时,收银员只要把条形码扫描器对准货物上 的条形码一扫,计算机屏幕上立刻就会显示该物品的价格。这是因为条形 码经扫描器扫描后,会产生相应的“数字信号”,经计算机处理后就可以 显示为货物的名称及价格等信息,进而可刷卡付款,打印付款收据。超市 自动收款设备如图所示。

非逻辑开关电路

44

第一章 数字电路基础

图所示为非门逻辑符号。非门真值表见表。 非门的逻辑功能可概括为“有0出1,有1出0”。非门的逻辑表达式为:

该表达式读作Y等于A非。

非门真值表

非门逻辑符号

45

28

第一章 数字电路基础

几种常见的BCD码

29

第一章 数字电路基础

(1)8421BCD码 最常用的BCD码是8421BCD码。 (2)5421BCD码 5421BCD码也是一种有权码,从高位到低位分别是5、4、2、1。 (3)2421BCD码 2421BCD码也是一种有权码,从高位到低位的权分别是2、4、2、1。 (4)余3码 这是一种无权码,它是在相应的8421BCD码上加0011(3)得到的。

15

第一章 数字电路基础

用数字电路测量电动机转速的原理框图

16

第一章 数字电路基础

2. 四人抢答器 四人抢答器原理框图如图所示。

四人抢答器原理框图

17

第一章 数字电路基础

从以上两个电路的工作过程可以看出,数字电路大致包含数字信号的产 生与整形、编码、寄存、译码、显示等典型单元数字电路。

此外,为了将传感器转换而来的模拟信号转换成控制系统所需要的数字 信号,必须采用模数转换器(A/D Converter)。数字信号被处理后,通常 还要经过数模转换器(D/A Converter)恢复成模拟信号,去驱动执行元件, 如图所示。

数字电路第二版张俊涛第六章习题答案

数字电路第二版张俊涛第六章习题答案一、选择题1、脉冲整形电路有。

A、多谐振荡器B、单稳态触发器C、施密特触发器D、555定时器2、多谐振荡器可产生。

A、正弦波B、矩形脉冲C、三角波D、锯齿波3、石英晶体多谐振荡器的突出优点是。

A、速度高B、电路简单C、振荡频率稳定D、输出波形边沿陡峭4、TTL单定时器型号的最后几位数字为。

A、555B、556C、7555D、75565、555定时器可以组成。

A、多谐振荡器B、单稳态触发器C、施密特触发器D、JK触发器6、用555定时器组成施密特触发器,当输入控制端CO外接10V电压时,回差电压为。

A、3、33VB、5VC、6、66VD、10V7、以下各电路中,可以产生脉冲定时。

A、多谐振荡器B、单稳态触发器C、施密特触发器D、石英晶体多谐振荡器二、判断题(正确打√,错误的打×)1、施密特触发器可用于将三角波变换成正弦波。

()2、施密特触发器有两个稳态。

()3、多谐振荡器的输出信号的周期与阻容元件的参数成正比。

()4、石英晶体多谐振荡器的振荡频率与电路中的R、C成正比。

()5、单稳态触发器的暂稳态时间与输入触发脉冲宽度成正比。

()6、单稳态触发器的暂稳态维持时间用tW表示,与电路中RC成正比。

()7、采用不可重触发单稳态触发器时,若在触发器进入暂稳态期间再次受到触发,输出脉宽可在此前暂稳态时间的基础上再展宽tW。

()8、施密特触发器的正向阈值电压一定大于负向阈值电压。

()三、填空题1、555定时器的最后数码为555的是产品,_________为7555的是产品。

2、施密特触发器具有_________ 现象,又称__________特性;单稳触发器最重要的参数为。

3、常见的脉冲产生电路有__________ ,常见的脉冲整形电路有____________ 、_______________ 。

4、为了实现高的频率稳定度,常采用 ______________振荡器;单稳态触发器受到外触发时进入 ______________态。

数电实验二 组合逻辑电路

实验二 组合逻辑电路一、实验目的1、熟悉组合逻辑电路的一些特点及一般分析、设计方法。

2、熟悉中规模集成电路典型的基本逻辑功能和简单应用设计。

二、实验器材1、直流稳压电源、数字逻辑电路实验箱、万用表、示波器2、74LS00、74LS04、74LS10、74LS20、74LS51、74LS86、74LS138、74LS148、74LS151、 74LS153三、实验内容和步骤 1、组合逻辑电路分析(1)图2-1是用SSI 实现的组合逻辑电路。

74LS51芯片是“与或非”门(CD AB Y +=), 74LS86芯片是“异或”门(B A Y ⊕=)。

建立实验电路,三个输入变量分别用三个 逻辑开关加载数值,两个输出变量的状态分别用两只LED 观察。

观察并记录输出变 量相应的状态变化。

整理结果形成真值表并进行分析,写出输出函数的逻辑表达式, 描述该逻辑电路所实现的逻辑功能。

(2)图2-2和2-3是用MSI 实现的组合逻辑电路。

图2-2中的74LS138芯片是“3-8译码 器”,74LS20芯片是“与非”门(ABCD Y =)图2-3中的74LS153芯片是四选一 数据选择器。

建立实验电路,对两个逻辑电路进行分析,列出真值表,写出函数的逻 辑表达式,描述逻辑电路所实现的功能。

图2-1:SSI 组合逻辑电路图2-2 :MSI 组合逻辑电路(74LS138)2、组合逻辑电路设计(1)SSI 逻辑门电路设计——裁判表决电路举重比赛有三名裁判:一个主裁判A 、两个副裁判B 和C 。

在杠铃是否完全举起裁 决中,最终结果取决于至少两名裁判的裁决,其中必须要有主裁判。

如果最终的裁决 为杠铃举起成功,则输出“有效”指示灯亮,否则杠铃举起失败。

(2)MSI 逻辑器件设计——路灯控制电路用74LS151芯片和逻辑门,设计一个路灯控制电路,要求能够在四个不同的地方都 能任意的开灯和关灯。

四、实验结果、电路分析及电路设计方案1、组合逻辑电路分析 (1)图2-1: 逻辑表达式:)()(11i i i i i i i i i i B A C S B A C B A C ⊕⊕=⊕+=--逻辑功能:实现A i 、B i 、C i-1三个一位二进制数 的加法运算功能,即全加器。