基于三角函数内插法的Gardner位定时同步环的FPGA实现

FPGA实现信号延时的方法_2003

FPGA实现信号延时的方法_2003FPGA实现信号延时的方法_2003FPGA是一种灵活可编程的集成电路,可用于实现各种数字电路和信号处理算法。

信号延时是指在电路中引入一定的延迟时间,用于控制信号到达目的地的时间,从而满足电路设计的需求。

下面介绍几种FPGA实现信号延时的方法。

1.时钟分频时钟分频是一种常见的实现信号延时的方法。

FPGA中的时钟信号可以通过分频电路进行分频,从而获得不同的时钟周期。

通过改变时钟周期,可以实现信号的不同延时。

分频电路通常由计数器和比较器组成,计数器根据预设的分频比例进行计数,当计数达到比较器设置的值时,输出一个分频后的时钟信号。

2.时钟插入时钟插入是指在FPGA中的信号路径上插入一个或多个时钟周期的逻辑,从而实现信号延时。

时钟插入可以通过在输出信号路径上添加一定数量的锁存器来实现。

锁存器的输出与输入相连接,但输出会被延时几个时钟周期,从而实现信号延时。

3.存储器存储器是FPGA中常见的资源,可以用于实现信号延时。

存储器可以用来存储先前的信号值,并在需要时输出。

通过存储器进行信号延时可以实现非常精确的延时控制,因为存储器的读写速度可以和时钟信号同步。

4.线性反馈移位寄存器(LFSR)线性反馈移位寄存器是一种将输入按位左移,并根据设定的多项式进行异或运算的电路。

LFSR可以用于生成伪随机序列,也可以用于实现信号延时。

通过将LFSR的输出与输入信号进行异或运算,可以实现将输入信号向右移动一定的位数,从而实现信号延时。

总结起来,FPGA实现信号延时的方法有时钟分频、时钟插入、存储器和LFSR等。

这些方法可以根据实际应用的需求和设计的复杂度选择使用。

不同的延时方法有不同的适用场景和性能特点,需要综合考虑电路的性能需求、资源利用和延时精度等因素。

正弦内插算法的FPGA实现

正弦内插算法的FPGA实现

张海潮;王勇;邱攀攀

【期刊名称】《河南大学学报:自然科学版》

【年(卷),期】2014(44)1

【摘要】在设计实现数字存储示波器的过程当中,数字内插技术已经成为必须要掌握的重要技术之一.根据示波器的性能指标有效存储带宽,设计了一种基于正弦内插算法的数字内插方法.该数字内插方法中所有模块均利用Verilog语言在Altera的FPGA芯片EP3C25E144C8上得到了实现和验证.该正弦内插算法中增采样的实现不同于传统方法中的补零法,而是采用数据保持的方法.介绍了正弦内插算法的详细推导、插值核的优化方法以及FPGA的具体实现,最后给出了整个设计分别在Matlab和ModelSim-Altera 6.6d下的仿真结果.

【总页数】5页(P94-98)

【关键词】正弦内插算法;数字存储示波器;FPGA;Verilog;HDL

【作者】张海潮;王勇;邱攀攀

【作者单位】四川大学电子信息学院

【正文语种】中文

【中图分类】TN713

【相关文献】

1.基于正弦内插的UM2000信号解码算法 [J], 贺广宇;范明

2.基于FPGA的内插定时恢复算法的实现 [J], 田克纯;徐艳

3.高速采样信号数字内插理论与正弦内插算法研究 [J], 林茂六;尹宝智;刘治宇

4.基于修正Rife算法的正弦波频率估计及FPGA实现 [J], 王旭东;刘渝;邓振淼

5.基于正弦反馈Logistic混沌映射的图像加密算法及其FPGA实现 [J], 李春彪;赵云楠;李雅宁;孔思晓

因版权原因,仅展示原文概要,查看原文内容请购买。

一种改进的Gardner定时同步算法

一种改进的Gardner定时同步算法刘伟;姚远程;秦明伟【期刊名称】《计算机工程》【年(卷),期】2013(000)011【摘要】Aiming at the problem that the existing timing synchronization algorithm needs a long time acquisition, poor stability and high error rate, an improved Gardner synchronization algorithm is proposed. On the analysis of different interpolation filter, piecewise parabolic interpolation filter is used in synchronization structure. For QPSK signal, open-loop and closed-loop analysis is carried out respectively. Simulation result shows that compared with previous algorithms, the proposed synchronization method has 0.005 s shorter acquisition and then the mean square error is reduced. Moreover, the bit error rate is significantly reduced while signal to noise ratio is greater than 8 dB.%针对定时同步算法捕获时间长、稳定霆差和误码率高等问题,提出一种改进的Gardner定时同步算法。

分析不同插值滤波器对定时同步的影陞,并选用分段抛物陑插值滤波器。

基于FPGA的基带信号的位同步信号提取(附程序)【毕业设计论文】

xxxx学院毕业设计论文题目:基于单片机和FPGA的位同步信号提取专业班级:电子信息工程学生姓名:学号:完成日期:指导教师:评阅教师:2006 年6月湖南工程学院应用技术学院毕业设计(论文)诚信承诺书本人慎重承诺和声明:所撰写的《基于单片机和FPGA的位同步信号提取》是在指导老师的指导下自主完成,文中所有引文或引用数据、图表均已注解说明来源,本人愿意为由此引起的后果承担责任。

设计(论文)的研究成果归属学校所有。

学生(签名)年月日湖南工程学院应用技术学院毕业设计(论文)任务书设计(论文)题目:基于单片机和FPGA的位同步信号提取姓名专业电子信息工程班级 0281 学号 16指导老师刘正青职称实验师教研室主任刘望军一、基本任务及要求:本课题是设计一具有通用性的输入信号的位同步提取系统,系统可以实现10HZ~1MHZ的信号同步。

使用单片机进行实时控制现场可编程逻辑门阵列FPGA完成位同步信号提取,通过理论和实验研究,完成硬件电路和软件设计并试制样机,要求完成:1、单片机实时控制FPGA,完成实时频率跟踪测量和自动锁相;2、在FPGA 内部,设计完成以下部分:A、全数字锁相环DPLL,主要包含:数控振荡器、鉴相器、可控模分频器B、LED动态扫描电路、FPGA和单片机的数字接口,以完成两者之间的数字传递3、设计辅助电路:键盘、LED;二、进度安排及完成时间:(1)第二周至第四周:查阅资料、撰写文献综述和开题报告;(2)第五周至第六周:毕业实习;(3)第六周至第七周:项目设计的总体框架:各个模块以及各个模块之间的关系确定,各个模块的方案选择与各个模块的所用主要器件的确定;(4)第八周至第十三周:各个模块的主要器件熟悉及相关知识的熟悉;各个模块的具体任务实现:硬件电路、软件编程;(5)第十四周至第十五周:系统的总体仿真与调试(6)第十六周至第十七周:撰写设计说明书;(7)第十八周:毕业设计答辩;目录摘要........................................................................................................ 错误!未定义书签。

基于FPGA的三角函数数字发生器设计

关键词

数字 信号发生器 ;现场可编程逻辑 门阵列 ; 直接数字频 率合成技术

T 31 P 0

中 图分 类 号

D e i n o i ia a e G e e a o o i o o e r c s g f D g t lW v n r t r f r Tr g n m t i

1 引 言

随着 移动通 信 、 无线 传 输 和接 人技 术 的快 速发 展 , 率合 成技 术 在通信 中的作 用 日益 显著 。它是 频

影 响发 射机 输 出频 谱 纯 度 和 接 收 灵 敏 度 的重 要 原

作频 率 以及 集成 度都 得 到 了极 大 的 提高 。同时 , 基

于 F GA 的直接 数 字频 率 合 成 器 件 有着 灵 活 的接 P

摘 要

系 统 而 严 格 地 论 证 与实 现 了 一 个 基 于 F GA 与 直 接 数 字 式 频 率 合 成 技 术 的 三 角 函 数 正 弦 数 字 信 号 发 生 器 , P

首 先 介 绍 了无 线 通 信 系 统 中 的重 要 作 用 , 下 来 阐 述 了它 的 工 作 原 理 、 统 结 构 , D 接 系 以及 理 论 上 的可 行 性 与 正 确 性 , 后 给 出 了 其 实 际 设 计 过 程 、 TI结 构 图 与 仿 真 波 形 测 试 结 果 。 最 R

K y W or s dgtlwa eg n r tr e d ii v e eao ,FP a GA ,dgtlfe u n y s n h sstc n lg iia rq e c y t e i e h oo y

Cl s m b r TP3 ] a s Nu e 0

同步定时

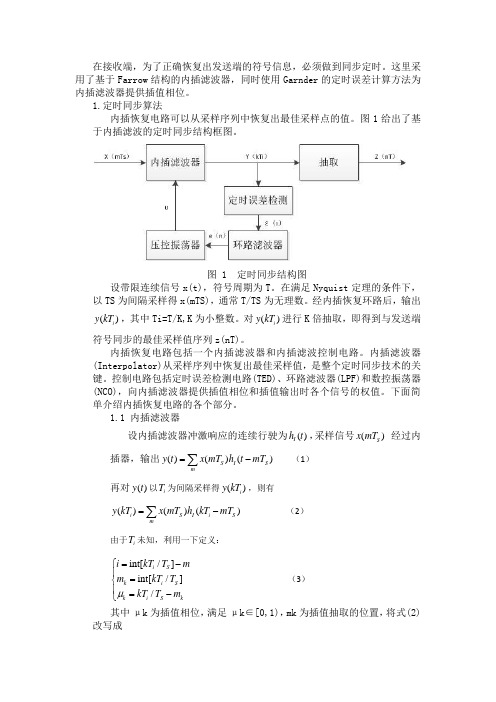

在接收端,为了正确恢复出发送端的符号信息,必须做到同步定时。

这里采用了基于Farrow 结构的内插滤波器,同时使用Garnder 的定时误差计算方法为内插滤波器提供插值相位。

1.定时同步算法内插恢复电路可以从采样序列中恢复出最佳采样点的值。

图1给出了基于内插滤波的定时同步结构框图。

图 1 定时同步结构图设带限连续信号x(t),符号周期为T 。

在满足Nyquist 定理的条件下,以TS 为间隔采样得x(mTS),通常T/TS 为无理数。

经内插恢复环路后,输出()i y kT ,其中Ti=T/K,K 为小整数。

对()i y kT 进行K 倍抽取,即得到与发送端符号同步的最佳采样值序列z(nT)。

内插恢复电路包括一个内插滤波器和内插滤波控制电路。

内插滤波器(Interpolator)从采样序列中恢复出最佳采样值,是整个定时同步技术的关键。

控制电路包括定时误差检测电路(TED)、环路滤波器(LPF)和数控振荡器(NCO),向内插滤波器提供插值相位和插值输出时各个信号的权值。

下面简单介绍内插恢复电路的各个部分。

1.1 内插滤波器设内插滤波器冲激响应的连续行驶为()I h t ,采样信号()S x mT 经过内插器,输出()()()S I S my t x mT h t mT =-∑(1)再对()y t 以i T 为间隔采样得()i y kT ,则有()()()i S I i S my kT x mT h kT mT =-∑(2)由于i T 未知,利用一下定义:int[/]int[/]/i S k i S ki S k i kT T m m kT T kT T mμ=-⎧⎪=⎨⎪=-⎩(3) 其中μk 为插值相位,满足μk ∈[0,1),mk 为插值抽取的位置,将式(2)改写成()[()]()[()]i k k S k I k S my kT y m T x m i h i T μμ=+=-+∑(4)(4)式即定时同步内插的基本公式。

基于内插滤波器符号同步的实现

基于内插滤波器符号同步的实现陈卫东,孙 栋,张华冲(中国电子科技集团公司第五十四研究所,河北石家庄050081)摘 要:比较了同步采样和异步采样条件下符号同步实现方法的不同,在全数字接收机中需要采用内插方法来实现符号同步,内插滤波器是一种线性时变滤波器,在工程中可以采用多项式内插函数来近似,采用FARROW 结构实现。

在此基础上介绍了内插法符号同步环路的结构,组成单元,其中详细介绍了内插控制器和定时误差检测器的原理。

在AWGN 信道中针对QAM 64信号进行了仿真和实现,眼图和星座图恢复良好,该符号同步环路可以应用于侦察接收机的解调器中。

关键词:全数字接收机;内插滤波器;符号同步中图分类号:TN914.42 文献标识码:A 文章编号:1003-3114(2009)06-53-3Design of Symbol Synchronization Circuit Based on InterpolationC HE N Wei dong,SUN Dong,ZHANG Hua chong(The 54th Research Insti tute of CETC,Shijiazhuang Hebei 050081,China)Abstract :In traditional demodulator synchronization sampling is used.In all di g i tal recei ver based on the non synchronization samplin g timing recovery is achieved with the help of interpolator.Cubic interpolator,interpolation controller and Gardner Algoithm for symbol timing error detection are introduced in detail i n this paper.The performance of the design is well i n si mulation.The desi gn is implemented in XILINX FPGA and i t can be applied to demodulation for reconnaissance receiver.Key words:all digital receiver;interpolator;symbol synchronization收稿日期:2009-09-01作者简介:陈卫东(1968-),男,高级工程师。

一种改进的Gardner定时同步算法

[ Ke y w o r d s ]t i mi n g s y n c h r o n i z a t i o n ; i n t e r p o l a t i o n i f l t e r ; t i mi n g - e r r o r d e t e c t o r ; S - c u r v e ; Ga r ne d r a l g o r i t h m; Q P S K m o d u l a t i o n

An I m pr o v e d Ga r d n e r Ti mi n g S y nc h r 0 n i z a t i 0 n Al g o r i t h m

L I U We i , Y A O Y u a n - c h e n g , Q I N Mi n g — w e i

文 献标识 码: A

中 田分类号: T P 3 0 1 . 6

种 改进 的 Ga r d n e r定 时 同步算 法

刘 伟,姚远程, 秦明伟

( 西 南科技 大 学信 息工 程学 院 ,四川 绵 阳 6 2 1 0 1 0 )

摘

要: 针对定时同步算法捕获时间长、稳定性差和误码率高等问题,提出一种改进的 G a r d n e r 定时同步算法。分析不同插值滤波

e r r o r r a t e , a n i mpr o v e d Ga r d n e r s yn c h r o ni z a t i o n a l go r i t h m i s p r o po s e d. On t he a na l y s i s o f d i f f e r e nt i n t e r po l a t i o n il f t e r , pi e c e wi s e p a r a b o l i c

一种基于FPGA的高精度同步信号生成设计与实现

一种基于FPGA的高精度同步信号生成设计与实现

陈昱均;孙希延;纪元法

【期刊名称】《桂林电子科技大学学报》

【年(卷),期】2015(000)003

【摘要】针对特定通信系统中需要实现快速、高精度的时间同步需求,设计了一种基于 FPGA 同步信号生成的系统方案。

系统以C/A码码片为最小时间刻度,通过对信号中码片数计数输出秒脉冲信号,并在同源情况下,根据码相位累加器溢出后残余值的特点,调整秒脉冲信号的输出位置。

结果表明,调整后的秒脉冲信号同步精度能达到纳秒级,在工程上具有一定的应用价值。

【总页数】4页(P178-181)

【作者】陈昱均;孙希延;纪元法

【作者单位】桂林电子科技大学信息与通信学院,广西桂林 541004;桂林电子科技大学信息与通信学院,广西桂林 541004;桂林电子科技大学信息与通信学院,广西桂林 541004

【正文语种】中文

【中图分类】TN911

【相关文献】

1.一种基于FPGA的位同步信号的实现 [J], 刘小群

2.一种基于FPGA的电网同步信号检测电路 [J], 姚景远;季正燕;朱忠尼;赵宏涛;;

3.一种基于FPGA的电网同步信号检测电路 [J], 姚景远;季正燕;朱忠尼;赵宏涛

4.一种基于FPGA的高斯随机数生成器的设计与实现 [J], 谷晓忱;张民选

5.基于FPGA的高精度数字化正弦信号生成的新方法 [J], 侯小华;施杰;毛惠丰;陈增禄

因版权原因,仅展示原文概要,查看原文内容请购买。

Gardner同步算法在高速GMSK信号传输中的应用

Gardner同步算法在高速GMSK信号传输中的应用顾圣明;陈丽婷;陈建斌【摘要】为了提高GMSK信号在高码速率传输下的同步性能,研究了Gardner算法在GMSK解调中的应用.在发射接收两端采样存在晶振漂移的情况下,Gardner 算法很好地纠正了采样频偏,准确地找到最佳采样时刻的判决信息.得益于其简单的同步结构,Gardner算法使得GMSK信号可用更高的码速率传输,同时简化了硬件电路.实验结果表明,在20 Mbps码速率的GMSK信号传输中,Gardner算法很好地完成了位同步,联合维特比解调,在9.5 dB的信噪比下达到9×10-5的误码率性能.【期刊名称】《无线电工程》【年(卷),期】2019(049)006【总页数】7页(P527-533)【关键词】高斯最小频移键控;位同步;Gardner算法;软件无线电【作者】顾圣明;陈丽婷;陈建斌【作者单位】上海航天电子技术研究所, 上海 201109;上海航天电子技术研究所, 上海 201109;上海航天电子技术研究所, 上海 201109【正文语种】中文【中图分类】TN914.30 引言高斯最小频移键控(GMSK)调制属于连续相位调制[1-2],具有很好的频谱性能和恒包络特性。

这2种特性使得GMSK调制在遥控遥测领域的应用也日益广泛。

目前,中国大多数的脉冲编码调制-调频(PCM-FM)体制遥测系统的码率都不超过2 Mbps[3],少数靶场开始配备10 Mbps码率的GMSK体制遥测系统。

但面对越来越高的遥测传输需求,提高GMSK体制遥测系统的传输速率迫在眉睫。

通常,限制遥测系统码速率的有硬件平台性能以及位同步所需的过采样率,文献[4]针对GMSK系统提出了一种简单的位同步开环算法,结构简单,但其需要16倍乃至更高的过采样率,且同步性能一般。

文献[5]中提出了一种快速捕获的位同步器,主要通过超前滞后信息来完成时钟的“添扣”,达到同步目的,但其精度取决于环路分频即过采样率,同样限制了传输速率。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

d l

r n l 1 O l , d - , ' 3钠

¨ m

o

州 女 q

・ ' 1 q n . 41 1硼

| I 口

■

哪

.

o 住 o l

di n ( 1  ̄铷

” O l

● 1 1 q m | 1 O I

而使信号尽可能地接近 最佳采样点

∥ )

图 1 位 定 时环 路 结 构

样得到, 从而影响后续 觯调判决结果。 这就需要对采样信号 2 F P GA 实现 及 其Mo d e l s i m仿 真 进行处理, 获得最佳 采样点。 G a r d n e r 等通过分析异步采样对 F P G A 实现 的顶层 框 图如 罔2 所 示, 由三 角函数 插值 滤 波 全数: 接收机带来的影响, 提出了 基于内插的同步算法。 器、 定时 误差检测、 环路滤 波、 插值控制等部分组成。本文 本 文针 对 实 际 系 统 的 需求 , 搭 建了 一科 , 适 用十 P S K 的 通 仿真采用了B P S K调制方式, 升 余弦滤波器的滚降系数为1 , 用的Ga r d n e r 位 定时 同步 电路 。 其 中的插 值滤波 器采用 了 采样数 据经过 与发端一致 的平方根升 余弦匹配滤波器, 采 实现结 构简单, 内插精度高, 适 合于F P GA 实现的三角函数 样速率为每 个符号4 个采样点, 设置本端采样周期与 1 / 4 个符 内插算 法。 在Mo d e l s i m上 对该 电路进 行了仿真, 并进 行了 号周期相比较偏小的T / 5 1 2 。 具体模块描述如下。 F P G A实现 。 该力‘ 案已经 应 用于实

的值 。

图2 F P G A实 现顶 层

作者简介: 邱 丈静 ( 1 9 8 2 一 ) , 女, 江 苏 南京

1 3 1— —

第l 5 姆

无线 互联 科 技 ・ 技 术J 、 川

环路 滤波 采 用锁 相环 中常用的 比例 积分 结 内插滤 波器选用 了内插 精度 高、 适合于F P G A 实现的三 偏移 的影 响 。 它具有较 好 的跟 踪性 能, 两个系数 K . 和 决定了环 路 角函数内插滤波器, O t l ]2 [ q  ̄ 的t r i a n g l ei n e r p 模块。 该内插算 构, 的调整 精度 和速度 。 这两 部分 由上述 公式 中的t r a c e 模块 法使用三角函数多项式代替传统的代数 多项式 , 其中三角函

在 加 性 高 斯 白噪 声 ( Ad d i t i v e Wh i t e G a u s s i a n N o i s e , A WGN) 信道 条 件下, 根 据 最 佳 接 收 机 理 论导 出的相 关 解 调

x ( m) y ( k )

器或 者匹配滤波器 都必 须在t = T 时刻抽样判决 , 这里陧 符 号周期。 t = T 是最佳抽样 判决时刻, 超前或 者滞后都会使误 码率增 J J u 。 在全数字无线通信接收系统中, 收发双方通常采 用完全 独立的基准 时钟 源, 两个 时钟 源的频率不 可能 完全 匹西 己 , 再加 L 信号在传输过程 中的延时一般 未知, 以及噪声 等的影 响,导致在接 收采样过 程中, 最佳采样点不能直接采

:u 晡l 1哪

: ‘ l ^ I : q

・

一 啊

” o l t - 州 ‰ q

. y . e hn

● № . y m_ 日_ 1 p铘

b n

—

, ”n . ' 3 o l -

由 内 插 滤 波 器 、定 时 误 差 检 测

摘 要: 位定时同步是 全数 字接 收 系统中的关键 组 成部 分, 对 系统性 能有重要影 响 . Ga r d n e r 定时同步环结构简单 便于工 程实现 , 三 角函数 内插 法结构简单 内插精度 高j 文章将三角函数 内插 法应用于G a r d n e r 定时同步环 , 降低了实现 难度 关键词 : 三角函数 内插 法; 位 定时; Ga r d n e r 算法

第1 5 期 2 0 1 7 句 8 月

NO.1 5

W i r e l e s s

AugU St,20l 7

基 于三角函数 内插 法 的Ga r d n e r 位 定 时 同步环的F P G A实现

邱 文静

( 南京 熊猫 汉 达 科技 有 限 公 司, 江 苏 南京 2 1 0 0 1 4 )

( Ti mi n g Er r o r De t e c t i o n, TED)、

丝吐—口 - 州 鹾泣_ 一 亡兰> 畦江—芒=) ¨' 3啦 越 越垃_ _ 亡= 诂

m -■吼 c

邵

q

环 路 滤 波 器和 控制 器 四部 分组 成 。 其 基 本 结 构 如 图l 所示。

际系统 r f 】 , 能稳定可 靠: [ 作, 性 能 良好。

B t

、H r p - 酆 c

羹孽

州 3 2 q

m“

1 Ga r d n e r 位 定时同步环模型

Ga r d n e r 位 定 时 同 步 环 主 要

t : 吲 捌 _ 临‘ m m

哪

t . o 叫谯 O l —

在该模 型中, 位 同步的实现具 体过程是, T E D模块 产 生 误差 信 号, 经 过环路滤波和控制器运算后

产 生 了由o v e r f l o w 控 制 的 内插 时 刻 基 准 点和 由u 控 制 的小数 时 间间隔 , 内插 滤 波 器 通 过 反 馈 过 来 的 插 值 时 刻 信 息 进 行插 值 操 作 , 产生 的 数 据送给 T E D模 块 产 生 新 的 定 时 误 差信 号, 以逐 步 调 整 内 插 时 刻 , 从