EDA实验指导书

EDA实验指导书_2

EDA 技术与VHDL实验指导书通信实验室编制2012年9月实验一组合电路的设计 (3)实验二时序电路的设计.................................错误!未定义书签。

实验三8位全加器的设计................................错误!未定义书签。

实验四含异步清零和同步时钟使能的加法计数器的设计错误!未定义书签。

实验五十六进制七段数码显示译码器设计.错误!未定义书签。

实验六数控分频器的设计.............................错误!未定义书签。

实验七序列检测器的设计.............................错误!未定义书签。

实训一组合电路的设计一、实验目的熟悉QuartusⅡ的VHDL文本设计流程全过程, 学习简单组合电路的设计、多层次电路设计、仿真和硬件测试。

二、实验内容1: 首先利用QuartusⅡ完成2选1多路选择器的文本编辑输入(mux21a.vhd)和仿真测试等步骤, 给出仿真波形。

最后在实验系统上进行硬件测试, 验证本项设计的功能。

2:将此多路选择器看成是一个元件mux21a, 利用元件例化语句描述一个双2选1多路选择器, 并将此文件放在同一目录中。

三、实验仪器ZY11EDA13BE型实验箱通用编程模块, 配置模块, 开关按键模块, LED显示模块。

四、实验原理1.2选1多路选择器的VHDL源代码ENTITY mux21a ISPORT ( a, b, s: IN BIT;y : OUT BIT );END ENTITY mux21a;ARCHITECTURE one OF mux21a ISBEGINPROCESS (a,b,s)BEGINIF s = '0' THEN y <= a ; ELSE y <= b ;END IF;END PROCESS;END ARCHITECTURE one ;下图为本例2选1多路选择器的仿真图形2.双2选1多路选择器以下是部分参考程序:...COMPONENT MUX21APORT ( a, b, s : IN STD_LOGIC;y : OUT STD_LOGIC);END COMPONENT ;...u1 : MUX21A PORT MAP(a=>a2, b=>a3, s=>s0, y=>tmp);u2 : MUX21A PORT MAP(a=>a1, b=>tmp, s=>s1, y=>outy);END ARCHITECTURE BHV ;五、实验报告:根据以上的实验内容写出实验报告, 包括程序设计、软件编译、仿真分析、硬件测试和详细实验过程;给出程序分析报告、仿真波形图及其分析报告。

EDA实验指导书

实验一 MAX+PLUSII软件的使用[实验目的] 掌握MAX+PLUSII软件的使用。

[实验内容] 学习MAX+PLUSII软件的设计操作步骤。

[实验原理] MAX+PLUSII软件介绍。

MAX+PLUSII软件功能简介:1 原理图输入(Graphic Editor)MAX+PLUSII软件具有图形输入能力,用户可以方便的使用图形编辑器输入电路图,图中的元器件可以调用元件库中元器件,除调用库中的元件以外,还可以调用该软件中的符号功能形成的功能块。

2 硬件描述语言输入(Text Editor)MAX+PLUSII软件中有一个集成的文本编辑器,该编辑器支持VHDL,AHDL和Verilog硬件描述语言的输入,同时还有一个语言模板使输入程序语言更加方便,该软件可以对这些程序语言进行编译并形成可以下载配置数据。

3 波形编辑器(waveform Editor)在进行逻辑电路的行为仿真时,需要在所设计电路的输入端加入一定的波形,波形编辑器可以生成和编辑仿真用的波形(*.SCF文件),使用该编辑器的工具条可以容易方便的生成波形和编辑波形。

4 编译与仿真当设计文件被编译好,并在波形编辑器中将输入波形编辑完毕后,就可以进行行为仿真了,通过仿真可以检验设计的逻辑关系是否准确。

5 器件编程当设计全部完成后,就可以将形成的目标文件下载到芯片中,实际验证设计的准确性。

[实验步骤]设计过程如下:1)输入项目文件名(File/Project/Name)2)输入源文件(图形、VHDL、AHDL、Verlog和波形输入方式)(Max+plusⅡ/graphic Editor, Max+plusⅡ/Text Editor, Max+plusⅡ/Waveform Editor)3)指定CPLD型号(Assign/Device)4)设置管脚、下载方式和逻辑综合的方式(Assign/Global Project Device Option,Assign/Global Logic Synthesis)5)保存并检查源文件(File/project/Save & Check)6)指定管脚(Max+plusⅡ/Floorplan Editor)7)保存和编译源文件(File/project/Save & Compile)8)生成波形文件(Max+plusⅡ/Waveform Editor)9)仿真(Max+plusⅡ/Simulator)10)下载配置(Max+plusⅡ/Programmer)[实验报告要求]不做要求。

电子设计自动化(eda)实验指导书

电子设计自动化(EDA)实验指导书前言近些年来,电子设计自动化(EDA)技术发展迅速。

一方面,各种大容量、高性能、低功耗的可编程逻辑器件不断推出,使得专用集成电路(ASIC)的生产商感受到空前的竞争压力。

另一方面,出现了许多EDA设计辅助工具,这些工具大大提高了新型集成电路的设计效率,使更低成本、更短周期的复杂数字系统开发成为可能。

于是一场ASIC与FPGA/CPLD之争在所难免。

然而PLD器件具有先天的竞争优势,那就是可以反复编程,在线调试。

EDA技术正是这场较量的推动引擎之一。

一般来说,EDA技术就是以计算机为平台,以EDA软件工具为开发环境,以HDL为设计语言,以可编程器件为载体,以ASIC、SOC芯片为目标器件,以电子系统设计为应用方向的电子产品自动化设计过程。

设计者只需编写硬件描述语言代码,然后选择目标器件,在集成开发环境里进行编译,仿真,综合,最后在线下载调试。

整个过程,大部分工作由EDA软件完成。

全球许多著名的可编程器件提供商都推出了自己的集成开发工具软件,如Altera 公司的MAX+PLUSⅡ、Quartus Ⅱ软件;Xilinx公司的Foundation 、ISE软件,Lattice公司的ispExpert软件,Actel公司的Libero 软件等。

这些软件的推出,极大地促进了集算法设计、芯片编程、电路板设计于一体的EDA技术的发展。

另外,在以SOC芯片为目标器件的电子系统设计要求下,可编程器件的内部开始集成高速的处理器硬核、处理器软核、DSP模块、大量的存储资源、高速的串行收发模块、系统时钟管理器、多标准的I/O接口模块,亦使得设计者更加得心应手,新一轮的数字革命由此引发。

EDA技术是一门实践性很强的学科,要培养出具有竞争力的一流IC设计人才,动手能力是关键。

只有通过理论学习,加上现场实验,在使用软件编程加硬件调试的过程中真正获得锻炼,增长技能。

ZY11EDA13BE型实验系统采用主板加适配板加扩展板的灵活结构,可方便进行基于不同PLD芯片的实验开发,并易于升级,符合当前高校在此方面对人才培养的要求。

EDA实验指导书

EDA技术实验指导书2012.09第一章针对HDL设计的EDA基本实验与设计实验1.计数器设计(1) 实验目的:熟悉Quartus II的Verilog/VHDL文本设计流程全过程,学习计数器的设计、仿真和硬件测试。

掌握原理图与文本混合设计方法。

(2) 实验原理:参考教材[1]3.3节。

实验程序为例(3) 实验内容1:根据教材[1]的4.1节在Quartus II上对例3-22进行编辑、编译、综合、适配、仿真。

说明例中各语句的作用。

给出其所有信号的时序仿真波形,根据波形详细描述此设计的功能特点,包括RST、EN、LOAD、DA TA,CLK等信号等异步和同步特性。

查阅编译后的计数器的时序特点,从时序仿真图和编1 原理图示意图译报告中了解计数时钟输入至计数数据输出的延时情况,包括设定不同优化约束后的改善情况以及当选择不同FPGA后的延时情况,给出分析报告。

(4) 实验内容2:用教材[1]第4章介绍的不同方式锁定引脚并硬件下载测试。

引脚锁定后进行编译、下载和硬件测试实验。

将实验过程和实验结果写进实验报告。

硬件实验中,注意测试所有控制信号和显示信号,包括RST、EN、LOAD、DA TA等的同步、异步特性,进位信号等。

时钟CLK换不同输入:手动有抖动或无抖动键输入,1Hz或4Hz时钟脉冲输入,这需要附录1.3的模块B4板才能获得,或直接使用KX_DN5/7系列EDA/SOPC实验系统。

(5) 实验内容3:使用SignalTap II对此计数器进行实时测试,流程与要求参考教材[1]第4章,给出报告。

(6) 实验内容4:从设计中去除SignalTap II,要求全程编译后,将生成的SOF文件转变成用于配置器件EPCS4的压缩的间接配置文件*. jic,并使用USB-Blaster对实验板上的EPCS4进行编程,最后进行验证。

编程和全程编译前,按教材[1]图4-6所示,设定所有控制和参数。

(7) 实验内容5:为此项设计加入一个可用于SignalTap II采样的独立的时钟输入端CLK0。

EDA实验指导书1209

实验一QuartusII软件应用一、实验目的1、熟悉EDA开发平台的基本操作。

2、掌握EDA开发工具的图形设计方法。

3、掌握图形设计的编译与验证方法。

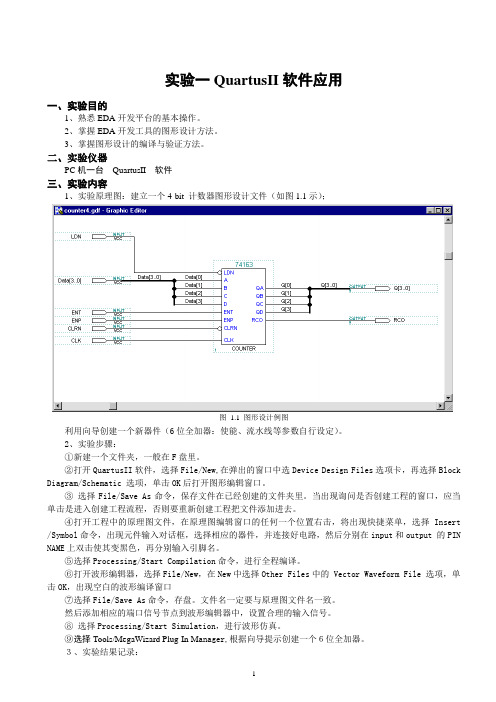

二、实验仪器PC机一台QuartusII软件三、实验内容1、实验原理图:建立一个4-bit 计数器图形设计文件(如图1.1示);图 1.1 图形设计例图利用向导创建一个新器件(6位全加器:使能、流水线等参数自行设定)。

2、实验步骤:①新建一个文件夹,一般在F盘里。

②打开QuartusII软件,选择File/New,在弹出的窗口中选Device Design Files选项卡,再选择Block Diagram/Schematic 选项,单击OK后打开图形编辑窗口。

③选择File/Save As命令,保存文件在已经创建的文件夹里。

当出现询问是否创建工程的窗口,应当单击是进入创建工程流程,否则要重新创建工程把文件添加进去。

④打开工程中的原理图文件,在原理图编辑窗口的任何一个位置右击,将出现快捷菜单,选择Insert /Symbol命令,出现元件输入对话框,选择相应的器件,并连接好电路,然后分别在input和output 的PIN NAME上双击使其变黑色,再分别输入引脚名。

⑤选择Processing/Start Compilation命令,进行全程编译。

⑥打开波形编辑器,选择File/New,在New中选择Other Files中的 Vector Waveform File 选项,单击OK,出现空白的波形编译窗口⑦选择File/Save As命令,存盘。

文件名一定要与原理图文件名一致。

然后添加相应的端口信号节点到波形编辑器中,设置合理的输入信号。

⑧选择Processing/Start Simulation,进行波形仿真。

⑨选择Tools/MegaWizard Plug-In M anager,根据向导提示创建一个6位全加器。

3、实验结果记录:打印出实验原理图与仿真波形图,打印出利用向导创建的新器件的图形,完成实验报告四、实验研究与思考1、延迟时间分析、最高工作频率分析等时间分析有何重要性?2、流水线的作用是什么?对那些性能有影响?2、功能仿真、验证起到什么作用?实验二VHDL软件设计一、实验目的1、熟悉EDA开发平台的基本操作。

EDA实验指导书

实验一熟悉QUARTUS Ⅱ的设计过程[输入方式:文本输入、图形输入、波形输入等]一、实验目的:1、掌握QUARTUSⅡ安装过程;2、熟悉QUARTUSⅡ设计环境;3、掌握QUARTUSⅡ的设计过程。

二、实验内容及步骤(一)、安装QUARTUS II。

注:第一次安装QUARTUS要安装license。

(二)、QUARTUSⅡ设计开发步骤一、创建工作文件夹在windows中建立一个文件夹(又称工作库或WORK LIBRARY),用于保存设计工程项目的有关文件。

注:设计工程项目的有关文件不能保存在根目录下,必须保存在一个文件夹之下。

例如建立的文件夹:E:\mux.二、启动Quartus II点击QUARTUSⅡ7.0图标打开QUARTUSⅡ7.0设计窗口。

三、设计文件输入1、打开输入文件编辑器点击菜单File\new…新建立一个文本设计文件。

用文本输入法输入程序。

程序见附录。

2、保存文件,文件名名同实体名。

后缀.VHD四、逻辑综合1、创建工程点击菜单File\New Project Wizard…….进行工程设置。

2、编译设置⑴选择PLD芯片:Assignmenmts\Settings\Device弹出的窗口中选择选择芯片。

⑵选择配置芯片的工作方式:Assignmenmts\Settings\Device\Device&Pin Options弹出的窗口中首选General项,在Options栏中选择Auto-restart-configuration after error.⑶选择配置芯片和编程方式:Assignmenmts\Settings\Device\Device&Pin Options弹出的窗口中选择Configuration栏,在窗口中设置配置方式,配置芯片和是否生成压缩的配置文件。

⑷选择输出设置:保持默认。

⑸选择目标器件闲置引脚的状态:Assignmenmts\Settings\Device\Device&Pin Options弹出的窗口中选择Unused Pins栏,在窗口中对闲置的引脚设置,推荐设置为As output driving groud。

EDA实验指导书全

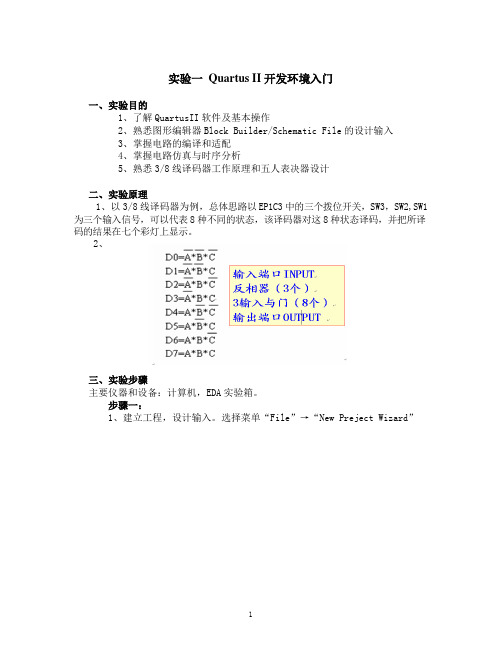

实验一Quartus II开发环境入门一、实验目的1、了解QuartusII软件及基本操作2、熟悉图形编辑器Block Builder/Schematic File的设计输入3、掌握电路的编译和适配4、掌握电路仿真与时序分析5、熟悉3/8线译码器工作原理和五人表决器设计二、实验原理1、以3/8线译码器为例,总体思路以EP1C3中的三个拨位开关,SW3,SW2,SW1为三个输入信号,可以代表8种不同的状态,该译码器对这8种状态译码,并把所译码的结果在七个彩灯上显示。

2、三、实验步骤主要仪器和设备:计算机,EDA实验箱。

步骤一:1、建立工程,设计输入。

选择菜单“File”→“New Preject Wizard”将设计文件加入工程中:点击下方的“Next” 按钮,在弹出的对话框中点击“File”栏的按钮,将此工程相关的所有VHDL文件加入进此工程(如果有的话)。

Cyclone系列的EP1C3T144C8按下“Next”后,出现仿真工具选择对话框。

不作任何选择。

4、完成设置点击“Next”后,完成工程的设定,点击“finish”。

步骤二:1、选择File/New或点击主菜单中的空白图标,进入新建程序文件状态,选择VHDL file 。

VHDL程序文件的扩展名是:* .vhd程序代码:-- A simple 3 to 8 decoderlibrary ieee;use ieee.std_logic_1164.all;entity decoder isport ( inp: in std_logic_vector(2 downto 0);outp: out std_logic_vector(7 downto 0)); end decoder;architecture behave of decoder isbeginoutp(0) <= '1' when inp = "000" else '0';outp(1) <= '1' when inp = "001" else '0';outp(2) <= '1' when inp = "010" else '0';outp(3) <= '1' when inp = "011" else '0';outp(4) <= '1' when inp = "100" else '0';outp(5) <= '1' when inp = "101" else '0';outp(6) <= '1' when inp = "110" else '0';outp(7) <= '1' when inp = "111" else '0';end behave;步骤三:1、选择菜单“File”→“New ” →“ Schematic File”,即弹出原理图编辑框。

《EDA技术》实验指导书

EDA技术实验指导书适用于电子信息工程专业QUARTUS II 8.1软件的使用一、实验目的与要求:1、练习使用QUARTUS II 8.1软件,掌握利用该软件进行简单EDA设计的基本流程;2、完成一个通过拨码开关控制发光二极管亮灭的应用,实验结束后可独立完成思考题。

二、实验环境与器材:1、微机(已安装授权的QUARTUS II 8.1软件)2、EDA/SOPC实验开发系统3、USB Blaster下载线一根三、背景知识与操作流程:QUARTUS II是ALTERA公司推出的EDA开发工具,其前身为MAX PLUS II,目前实验室安装的版本为8.1,利用该软件可进行对可编程逻辑器件的分析、综合、下载等设计。

EDA/SOPC实验开发系统是由北京百科公司生产的一套EDA实验系统,其核心芯片采用ALTERA公司的CYCLONE系列FPGA产品EP1C6Q240C8,同时配备了丰富的外部接口资源,可供学生进行EDA设计实验。

启动QUARTUS后的界面如图1所示,首先需要创建一个工程,具体操作过程如下:图1 QUARTUS软件的启动界面(1)点击File –> New Project Wizard创建一个新工程,系统显示如图2。

图2 工程创建向导的启始页(2)点击Next,为工程选择存储目录、工程名称、顶层实体名等,如图3所示;(3)点击Next,若目录不存在,系统可能提示创建新目录,如图4所示,点击“是”按钮创建新目录,系统显示如图5所示;(4)系统提示是否需要加入文件,在此不添加任何文件;(5)点击Next,进入设备选择对话框,如图6,这里选中实验箱的核心芯片CYCLONE系列FPGA产品EP1C6Q240C8;(6)点击Next,系统显示如图7,提示是否需要其他EDA工具,这里不选任何其他工具;(7)点击Next后,系统提示创建工程的各属性总结,若没有错误,点击Finish,工程创建向导将生成一个工程,这时软件界面如图8,在窗口左侧显示出设备型号和该工程的基本信息等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验一 MAX+PLUSII软件的使用[实验目的] 掌握MAX+PLUSII软件的使用。

[实验内容] 学习MAX+PLUSII软件的设计操作步骤。

[实验原理] MAX+PLUSII软件介绍。

MAX+PLUSII软件功能简介:1 原理图输入(Graphic Editor)MAX+PLUSII软件具有图形输入能力,用户可以方便的使用图形编辑器输入电路图,图中的元器件可以调用元件库中元器件,除调用库中的元件以外,还可以调用该软件中的符号功能形成的功能块。

2 硬件描述语言输入(Text Editor)MAX+PLUSII软件中有一个集成的文本编辑器,该编辑器支持VHDL,AHDL和Verilog硬件描述语言的输入,同时还有一个语言模板使输入程序语言更加方便,该软件可以对这些程序语言进行编译并形成可以下载配置数据。

3 波形编辑器(waveform Editor)在进行逻辑电路的行为仿真时,需要在所设计电路的输入端加入一定的波形,波形编辑器可以生成和编辑仿真用的波形(*.SCF文件),使用该编辑器的工具条可以容易方便的生成波形和编辑波形。

4 编译与仿真当设计文件被编译好,并在波形编辑器中将输入波形编辑完毕后,就可以进行行为仿真了,通过仿真可以检验设计的逻辑关系是否准确。

5 器件编程当设计全部完成后,就可以将形成的目标文件下载到芯片中,实际验证设计的准确性。

[实验步骤]设计过程如下:1)输入项目文件名(File/Project/Name)2)输入源文件(图形、VHDL、AHDL、Verlog和波形输入方式)(Max+plusⅡ/graphic Editor, Max+plusⅡ/Text Editor, Max+plusⅡ/Waveform Editor)3)指定CPLD型号(Assign/Device)4)设置管脚、下载方式和逻辑综合的方式(Assign/Global Project Device Option,Assign/Global Logic Synthesis)5)保存并检查源文件(File/project/Save & Check)6)指定管脚(Max+plusⅡ/Floorplan Editor)7)保存和编译源文件(File/project/Save & Compile)8)生成波形文件(Max+plusⅡ/Waveform Editor)9)仿真(Max+plusⅡ/Simulator)10)下载配置(Max+plusⅡ/Programmer)[实验报告要求]不做要求。

实验二简单组合逻辑电路设计[实验目的] 1 通过本实验提供的实例,掌握组合逻辑电路的设计方法。

2 初步了解PLD设计的全过程和相关软件的使用。

[实验内容]1设计一个3-8线译码器。

2设计一个8-3线优先编码器。

3设计一个8位数值比较器。

4设计一个优先权排队电路。

[实验原理]1、3-8线译码器,8-3线优先编码器,8位数值比较器在数字电路教材中有详细的论述此处略。

2、优先权排队电路,排队顺序为:A=1 最高优先级,B=1 次高优先级,C=1 最低优先级输出端最高只能有一端为“1”,即只能是优先级较高的输入端所对应的输出端为“1”,即该输出端所对应的灯亮。

[实验步骤]注:本章的实验内容均以ALTERA公司的EPF10K10适配板为基础编写。

(一)3-8线译码器:启动Max plusⅡ软件,打开工程Test1/3-8decoder文件,下载3-8decoder.sof程序;(先插上下载线,再打开交流开关,然后打开直流开关APW1,最后打开通用下载模块的电源开关XPW1,点击软件中的下载编程或者配置按钮即可开始下载所需要的程序。

后面所有的下载操作步骤均一样将不在重复介绍)。

将拨码开关AS1(2)(3)设置“ON”(当不使用数码管时AS1(1)设置“ON”)。

实验现象:拨位开关KD1~KD3分别代表图中的C、B、A;发光二极管LED1~LED8分别代表图中的LED1~LED8。

当C、B、A依次从000~111拨动时,发光二极管LED1~LED8依次从左至右被选亮。

(二)8-3线优先编码器:启动Max plusⅡ软件,打开工程Test1/encode文件,下载encode.sof程序;将拨码开关AS1(2)(3)(4)设置“ON”;按照下表1所示的真值表完成该实验。

实验现象:拨位开关KD1~KD8,KD16分别代表程序中的D0~D7,EIN;发光二极管L ED1~LED5分别代表程序中的A2N,A1N,A0N,GSN, EON。

真值表输出数据中的‘1’代码所对应的发光二极管将会被点亮。

8-3线优先编码器真值表1—高电平;0—低电平;X—任意,输入低电平有效。

(三)8位数值比较器:启动Max plusⅡ软件,打开工程Test1/bijiaoqi文件,下载bijiaoqi.sof程序。

将拨码开关AS1(2)(3)(4)设置“ON”。

实验现象:拨位开关KD1~KD16分别代表图中的A7~A0(从高到低),B7~B0(从高到低);发光二极管LED1~LED3分别代表图中的LAMP1~LAMP3。

当A[7..0]>B[7..0]时,LED3被点亮;当A[7..0]=B[7..0]时,LED2被点亮;当A[7..0]<B[7..0]时,LED1被点亮。

(四)优先权排队电路:启动Max plusⅡ软件,打开工程Test1/gate2文件,下载gate2.sof程序。

拨码开关AS1(2)(3)设置“ON”。

实验现象:拨位开关KD1~KD3分别代表图中的A,B,C;发光二极管LED1~LED3分别代表图中的LAMP1~LAMP3,在该实验中A的优先级最高。

当KD1=‘1’时,发光二极管LED1被点亮;当KD1=‘0’,KD2=‘1’时,发光二极管LED2被点亮;当KD1=‘0’,KD2=‘0’,KD3=‘1’时,发光二极管LED3被点亮。

[实验报告]要求用VHDL语言编程完成以上3-8译码器,8-3线优先编码器,8位数值比较器的设计。

比较图形输入法与语言输入法的优劣。

实验三简单时序电路设计[实验目的]1、掌握基本RS触发器、D触发器、JK触发器的逻辑功能。

2、掌握时序电路的设计方法。

3、熟悉触发器之间相互转换的方法。

[实验内容]1通过模拟和仿真分析和验证三种触发器的逻辑功能及触发方式。

2设计基本RS触发器、D触发器、JK触发器。

3扩展任务:设计其它触发器如T触发器,并研究其相互转化的方法。

[实验原理]1、RS基本触发器:(见相关数字电路教材,此处略)2、D触发器:正沿触发的D触发器的电路符号如下图所示。

它是一个正边沿触发的D触发器,有一个数据输入端d,一个时钟输入端clk和一个数据输出端q。

D触发器的真值表如下表所示。

从表中可以看到,D锁存器的输出端只有在正沿脉冲过后,输入端d的数据才可以传递到输出端q。

D锁存器真值表3、JK触发器:带有复位/置位功能的JK触发器电路符号如下图所示。

JK触发器的输入端有置位输入prn,复位输入clrn,控制输入j和k,时钟信号clk;输出端q和反向输出端NQ。

JK触发器的真值表如下表所示。

[实验步骤](一)RS基本触发器:启动Max plusⅡ软件,打开工程Test3/RS文件,下载rs.sof程序;将拨码开关AS1(2)(3)设置“ON”;实验现象:拨位开关KD1~KD2分别代表图中的R、S输入端;发光二极管LED1~LED2分别代表图中的Q、NQ输出端。

当拨位开关按照R、S触发器真值表的输入值拨动时,发光二极管则按照真值表的输出值显示(‘1’亮;‘0’灭)。

(二)D触发器:启动Max plusⅡ软件,打开工程Test3/DFF文件,下载dff.sof程序;将拨码开关AS1(2)(3)设置“ON”;实验现象:拨位开关KD1代表图中的D输入端;发光二极管LED1~LED2分别代表图中的Q、NQ输出端;输入时钟clk接1Hz档(TJ1处)。

当拨位开关(KD1)按照D触发器真值表的输入值拨动时,发光二极管则按照真值表的输出值显示(‘1’亮;‘0’灭)。

(三)JK触发器:启动Max plusⅡ软件,打开工程Test3/JKFF文件,下载jkff.sof程序;将拨码开关AS1(2)(3)设置“ON”;实验现象:拨位开关KD1~KD3分别代表图中的PRN置位端和J、K输入端;轻触开关K17代表图中的CLRN清零端;发光二极管LED1~LED2分别代表图中的Q、NQ输出端;输入时钟clk接1Hz 档(TJ1处)。

当拨位开关(J、K和PRN)、轻触开关(K17)按照JK触发器真值表的输入值拨动时,发光二极管则按照真值表的输出值显示(‘1’亮;‘0’灭)。

[实验报告]要求用VHDL语言编程完成D触发器和JK触发器的设计。

实验四 LED显示译码电路的设计[实验目的]1、实现十六进制计数显示。

2、实现常见英语字母显示。

[实验内容]1.编写一个简单的0~F轮换显示的十六进制计数电路。

2.编写一个显示英文字母A、B、C、D、E、F、H、P、L的轮换显示电路。

3.通过仿真或观察波形验证设计电路的正确性。

[实验原理]用数码管除了可以显示0~9的阿拉伯数字外,还可以显示一些英语字母。

数码管由7段显示输出,利用7个位的组合输出,就可以形成26个英语字母的对应显示。

表2显示常见的字母与7段显示关系。

表2 常见的字母与7段显示关系[实验步骤](一)0~F计数显示电路:1、启动Max plusⅡ软件,打开工程Test4/display1文件,下载display1.sof程序;2、将拨码开关AS1全部设置为“OFF”;实验现象:将计数频率设置为1Hz(TJ1处,数码管显示的数值每隔一秒变化一次),数码管SM5~SM8同时循环显示0~F。

当改变计数频率时,先按一下复位键(K17)然后再显示。

(二)英语字母显示电路:1、启动Max plusⅡ软件,打开工程Test4/display2文件,下载display2.sof程序;2、将拨码开关AS1(1)设置为“ON”;实验现象:将计数频率设置为1Hz(TJ1处,数码管显示的数值每隔一秒变化一次),扫描频率设置为32.768KHz(TJ5处);数码管SM5~SM8同时循环显示A、B、C、D、E、F、H、L、O。

[实验报告]要求用VHDL语言编程完成十六进制数LED显示译码器的设计。

实验五数字钟设计[实验目的]1掌握多位计数器相连的设计方法。

2掌握十进制、六十进制、二十四进制计数器的设计方法。

3掌握喇叭的驱动方法。

4LED 灯的花样显示。

5掌握CPLD的层次化设计方法。

[实验内容]1、具有时、分、秒计数显示功能,以24小时循环计时。

2、具有清零,调节小时、分钟的功能。