运放稳定性分析环路稳定性基础

典型的两级运放环路稳定性分析

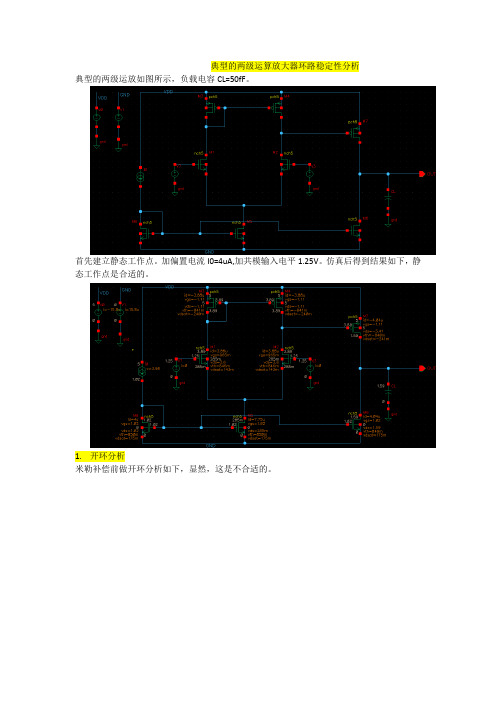

典型的两级运算放大器环路稳定性分析典型的两级运放如图所示,负载电容CL=50fF。

首先建立静态工作点。

加偏置电流I0=4uA,加共模输入电平1.25V。

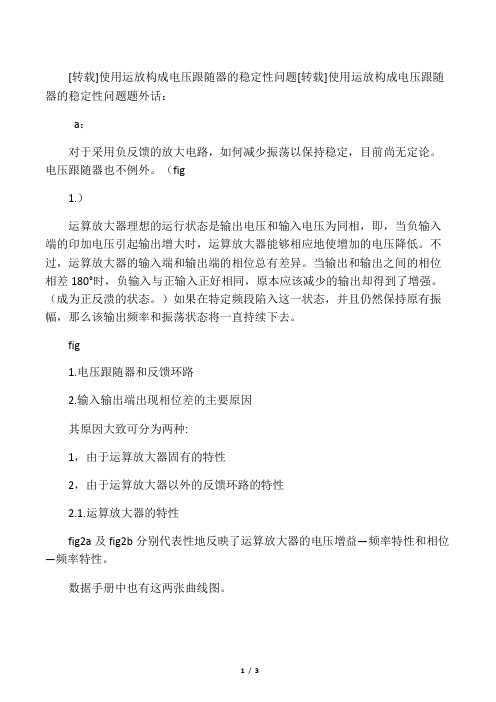

仿真后得到结果如下,静态工作点是合适的。

1.开环分析米勒补偿前做开环分析如下,显然,这是不合适的。

加米勒补偿电容Cc=200fF,做开环分析如下,显然,这也是不合适的。

这是由于电路中存在零点造成的。

加入调零电阻Rz=40K,,仿真结果如下。

可以看出,,,相位裕度为40度,不够。

可通过加大补偿电容来进一步分裂p1,p2主次极点。

(已尝试过加米勒补偿电容Cc=300fF可以得到大于60度的相位裕度)。

但是本次设计的运放用在负反馈环路中,故只需要负反馈环路是稳定的就达到设计标准。

理论计算。

查看各管子的静态工作点。

,,,即。

,,,即。

,。

理论值与仿真结果非常接近。

,理论值与仿真结果非常接近。

,,理论值与仿真结果非常接近。

,,理论值与仿真结果40度偏差较大。

2.在负反馈环路中做环路稳定性分析:从上图可以看出,加入反馈电阻网络R1,R2后就打破了原有的静态工作点:主要是反馈电阻网络R1,R2中的电流由M7管提供,所以M7管的静态工作点打破了,即运放的第二级跨导GmⅡ,输出电阻R2都变了。

从波特图中可以看出相位裕度为77度,满足设计标准。

理论计算:查看各管子的静态工作点。

,,,即。

,,,即。

,。

理论值与仿真结果非常接近。

,理论值与仿真结果非常接近。

,理论值与仿真结果非常接近。

,,理论值与仿真结果77度偏差较大。

此结果可能是由于gm7变大,原来的调零电阻RZ过大造成的。

现在改变调零电阻Rz=25K,,仿真结果如下:此时,相位裕度为63度,满足设计标准。

3.改用大电感大电容仿真环路增益:仿真方法如上图所示,将环路断开,加入大电感L0=1GH通直流以建立直流工作点,并且断开交流通路,加入大电容C3=1GF通交流小信号V8。

从仿真结果图中可以看出相位裕度为70度。

不同的仿真方式所得到的结果略有误差。

环路稳定性分析

X2(s) 为控制

开环控制的பைடு நூலகம்递函数为:

X 2 ( s) G1 ( s ) = X 1 ( s)

两个环节串联:

图1.2 两环节控制模型

可以得出:

X 2 (s) G1 ( s ) = X1 (s)

X 3 (s) G2 ( s ) = X 2 (s)

X3 (s) X2 (s) X3 (s) G(s) = = g = G1(s)g 2 (s) G X1(s) X1(s) X2 (s)

R1

C3 =

1 2pgR3g g SW 0.7 F

其中, FSW 为 IC工作频率(也即为开关频率). 通过上面求得的电阻电容等参数数值需保证: 交越频率点需以- 20dB / decade穿越0dB线,并且交越频率点所对应的相位 裕度需大于 45°.

四.OP+MOS稳定性分析

图4.1 OP+MOS完整结构图

C1 =

C2 2p gR2 g 2 gFCE - 1 C

(四).第二个极点频率 F 2 介于0.5~1.0IC工作频率范围内,一般选择0.7倍因 P 子.设置较低的 FP 2能够有效降低补偿网络高频增益,从而降低接收高频尖峰 噪声的干扰. R 3 , C3 通过下面两式可求得:

R3 =

FSW -1 FLC

x20logmaxinf在低频时输入信号不衰减增益为在频率以cldvlcosc上随着电容阻抗的减少电感阻抗的增加使得增益变化率为40dbdecade或斜率为2由于大多数波电容具有esr因此在以上的低频段容抗远远flc大于esr此时阻抗仅是容抗在起作用斜率仍为20dbdecade在更高频1wcesr时从输出端看的阻抗仅是esr在此频率范围电路f变为lr波而不是lc波

使用运放构成电压跟随器的稳定性问题

[转载]使用运放构成电压跟随器的稳定性问题[转载]使用运放构成电压跟随器的稳定性问题题外话:a:对于采用负反馈的放大电路,如何减少振荡以保持稳定,目前尚无定论。

电压跟随器也不例外。

(fig1.)运算放大器理想的运行状态是输出电压和输入电压为同相,即,当负输入端的印加电压引起输出增大时,运算放大器能够相应地使增加的电压降低。

不过,运算放大器的输入端和输出端的相位总有差异。

当输出和输出之间的相位相差180°时,负输入与正输入正好相同,原本应该减少的输出却得到了增强。

(成为正反溃的状态。

)如果在特定频段陷入这一状态,并且仍然保持原有振幅,那么该输出频率和振荡状态将一直持续下去。

fig1.电压跟随器和反馈环路2.输入输出端出现相位差的主要原因其原因大致可分为两种:1,由于运算放大器固有的特性2,由于运算放大器以外的反馈环路的特性2.1.运算放大器的特性fig2a及fig2b分别代表性地反映了运算放大器的电压增益—频率特性和相位—频率特性。

数据手册中也有这两张曲线图。

如图所示,运算放大器的电压增益和相位随频率变化。

运算放大器的增益与反馈后的增益(使用电压跟随器时为0db)之差,即为反馈环路绕行一周的增益(反馈增益)。

如果反馈增益不足1倍(0db),那么,即使相位变化180o,回到正反馈状态,负增益也将在电路中逐渐衰减,理论上不会引起震荡。

反而言之,当相位变化180o后,如频率对应的环路增益为1倍,则将维持原有振幅;如频率对应的环路增益为大于1倍时,振幅将逐渐发散。

在多数情况下,在振幅发散过程中,受最大输出电压等非线性要素的影响,振幅受到限制,将维持震荡状态。

为此,当环路增益为0db时的频率所对应的相位与180o之间的差是判断负反馈环路稳定性的重要因素,该参数称为相位裕度。

(fig2b.)如没有特别说明,单个放大器作为电压跟随器时,要保持足够相位裕度的。

注:数据手册注明「建议使用6db以上的增益」的放大器,不可用作电压跟随器。

关于共模反馈环路稳定性的考虑

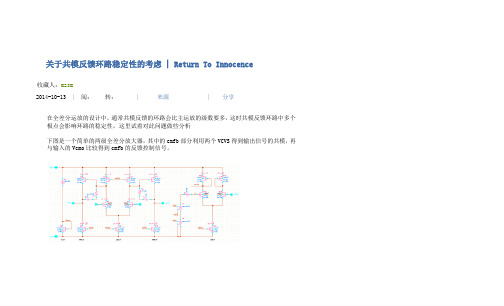

关于共模反馈环路稳定性的考虑 | Return To Innocence收藏人:mzsm2014-10-13 | 阅:转:| 来源| 分享在全差分运放的设计中,通常共模反馈的环路会比主运放的级数要多,这时共模反馈环路中多个极点会影响环路的稳定性,这里试着对此问题做些分析下图是一个简单的两级全差分放大器,其中的cmfb部分利用两个VCVS得到输出信号的共模,再与输入的Vcmo比较得到cmfb的反馈控制信号。

考虑共模反馈环路,其中存在3个极点,包括运放第一级的输出极点、第二级的输出极点以及cmfb节点对应的极点。

与分析运放稳定性问题一样,前两者分别为主极点和次主极点,对于第3个极点,由于其阻抗和输出极点一样在1/gm量级(实际上,为消除系统失调,运放输出共源放大的mos管和cmfb的二极管连接的mos管有相同的过驱动电压,其gm按w/l成比例),不能简单的忽略。

实际上,这个cmfb的极点与上图中P管的特征频率ft相关,为此我们需要为其选择一个合适的过驱动电压Vov:首先Vov不能太低,这样才能以保证其ft在足够高的频率,以避免cmfb极点对环路的作用;同时这Vov也不能太高,他必须提供一定的gm/Id,保证运放输出级在电流一定的条件下有足够的gm,从而避免运放输出极点频率的下降。

上面是对利用理想VCVS得到输出共模的方式下的一些分析,下面我们看看实际的得到输出共模电路中的问题。

以电阻方式等到输出信号的共模电平是一种常见的方法,如果忽略前面电路的输出阻抗,cm-sense的电阻Rs和之后的共模比较电路的栅节点电容Cx会在共模反馈的环路中引入一个极点。

考虑到一般Rs至少要在Rds量级以避免其对运放增益的衰减,这位个极点的位置不会太高,因此必须加以考虑。

实际中,可通过在电阻Rs上并联电容Cs来减小这一极点的影响。

在上面的电路中, 通过简单的分析, 可以得到: 引入 Cs 之后, 由 cm-sense 部分引入的零极点为: Po=1/(Rs*(Cs+Cx)), Zo=1/(Rs*Cs), 即在极点之后补了一个零点来抵消其作用. 至于具体的 Cs 的取值, 考虑 Cs 至少与 Cx 比较接近, cmfb 环路才能得到一定的相位裕度, 若进一步考虑零极点对建立时间的影响, 应该将 Cs/Cx 取为一定值以上才能将零极点拉的足够近, 以减小这一零极点对对共模信号建立时间的影响。

利用Pspice模型分析放大器环路的稳定性

利用Pspice模型分析放大器环路的稳定性放大器放大器放大器的稳定性,但评估一个较为复杂的电路是否稳定,难度可能会大得多。

本文使用常见的Pspice宏模型结合一些简单的电路设计技巧来提高设计工程师的设计能力,以确保其设计的实用性与稳定性。

导致放大器不稳定的原因在任何相关频率下,只要环路增益不转变为正反馈,则闭环系统稳定。

环路增益是一个相量,因而具有幅度和相位特性。

环路由理想的负反馈转变为正反馈所带来的额外相移即是最常见的不稳定因素。

环路增益相位的“相关”频率,一般出现在环路增益大于或等于0dB之处。

图1:总等效噪声密度-反馈电阻关系曲线.的放大器电路,通过断开环路,测量信号在环路中传播一次所产生的相移,即可推算出电路的稳定情况.以下例子介绍的方法可利用仿真软件,运算放大器宏模型以及Pspice提供的理想元器件来实现。

图2:跨阻抗放大器。

高速低噪声跨阻放大器(TIA)稳定性示例我们以一个跨阻放大器(TIA)为例,通过分析其稳定性来阐述我们将要推荐的技术。

TIA广泛应用在工业领域和消费领域,例如LIDAR(光探测和测距)、条形码扫描仪、工厂自动化等。

设计工程师遇到的挑战是,在不会造成衰减和老化的情况下,如何最大化信噪比(SNR),以及如何获得足够的速度/带宽来传递所需的信号.图2为采用了LMH6629的放大器示意图,这款超高速(GBWP=4GHz)低噪声(0。

69nV/RtHz)器件具有+10V/V的最小稳定增益(COMP引脚连至VCC)的。

LMH6629的补偿(COMP)输入可以连至VEE,从而进一步将最小稳定增益降低到4V/V。

为获得最大的转换速率和带宽(小信号和大信号),在这个例子中,COMP引脚被连接到VCC。

可获得的带宽与放大器GBWP直接相关,与跨阻增益(RF)和光电二极管内的寄生电容成反比。

确定一个给定放大器所使用的反馈电阻(RF)有一个简单方便的办法:在使用了LMH6629的情况下,总等效输入电流噪声密度“ini”与RF的关系.图中的“in”是LMH6629的输入噪声电流,“en”是LMH6629的输入噪声电压,“k”是波尔兹曼常数,而“T”是用℃表示的绝对温度。

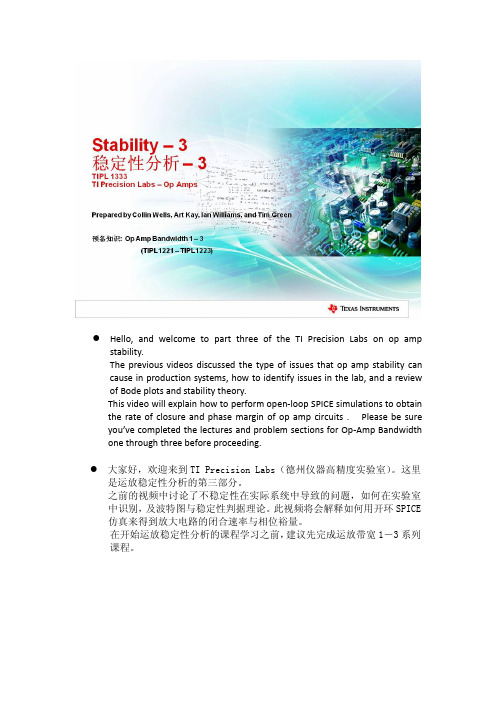

运算放大器稳定性分析3

Several example circuits ready for open-loop simulation are shown here. They can be used for review if there is confusion regarding where to break the loop in many standard circuit configurations. Note that for proper stability analysis, any output loading must remain directly on the output of the op amp and should not be placed on the other side of the inductor. Doing so would remove the effects the output loads have on the op amp output. 很多电路可以运用开环 SPICE 电路仿真,在实际电路中不知在何处断开 环路而感到困惑时可以用这些例子作为参考。 注意为了得到正确的稳定性分析结论,运放输出端所接的负载必须直接 体现在电路中,且不应该放置在电感的另外一端,否则就体现不同的负 载效应。

浅析DC-DC的环路稳定性问题

浅析DC/DC的环路稳定性问题

在电路系统的单板设计中我们经常用到各种电源,DC/DC是最广泛的一种,比如BUCK降压电路,一般我们都采用的是相关厂家的集成芯片如TI、ADI、Linear等,总的来说应用还是比较简单的,按照参考电路配置外围器件即可,然后按照布局布线原则完成单板设计。

但是如果仅仅是知道基本原理却不知所以然,导致的结果就是在出现问题时完全摸不着头脑,比如最近遇到一个问题就是DC/DC在空载时电压异常的现象。

这个问题是偶然出现的:该芯片已在其他单板上使用正常,但是最新的一块板子却出现电压异常波动。

对比二者原理图发现都一样,但是检查完PCB 后检查原理图发现输出电容配置有问题,改过电容后电压正常。

那幺为何同样的设计之前的没有问题,现在的有问题呢?进一步发现,新的问题板子在未使用时是空载的,而之前的板子都是一直带载,于是不改变电容插上负载,输出电压也正常了。

这是一个典型的开关电源的环路响应问题。

我们在学习运放的时候就研究过运放的闭环反馈特性,也就是幅频特性和相频特性。

那幺对于DC/DC而言,环路同样具有类似特性,下图是一个同步BUCK 电路。

基本的传输拓扑为:。

环路稳定性基础

环路稳定性基础引言本系列所采用的所有技术都将“以实例来定义”,而不管它在其他应用中能否用普通公式来表达。

为便于进行稳定性分析,我们在工具箱中使用了多种工具,包括数据资料信息、技巧、经验、SPICE仿真以及真实世界测试等,都将用来加快我们的稳定运放电路设计。

尽管很多技术都适用于电压反馈运放,但上述这些工具尤其适用于统一增益带宽小于20MHz的电压反馈运放。

选择增益带宽小于20MHz的原因是,随着运放带宽的增加,电路中的其他一些主要因素会形成回路,如印制板(PCB) 上的寄生电容、电容中的寄生电感以及电阻中的寄生电容与电感等。

我们下面介绍的大多数经验与技术并非仅仅是理论上的,而且是从利用增益带宽小于20MHz的运放、实际设计并构建真实世界电路中得来的。

本系列的第1部分回顾了进行稳定性分析所需的一些基本知识,并定义了将在整个系列中使用的一些术语。

图字(上、下):数据资料信息、技巧、经验、Tina SPICE仿真、测试;目的:学习如何用数据资料信息、技巧、经验法则、Tina SPICE仿真及测试来“更容易地”分析和设计运放,以确保环路稳定性;注:用于统一增益带宽小于20MHz的电压反馈运放的技巧与经验法则。

波特图(曲线)基础幅度曲线的频率响应是电压增益改变与频率改变的关系。

这种关系可用波特图上一条以分贝(dB) 来表示的电压增益比频率(Hz) 曲线来描述。

波特幅度图被绘成一种半对数曲线:x轴为采用对数刻度的频率(Hz)、y轴则为采用线性刻度的电压增益(dB) ,y轴最好是采用方便的每主格45°刻度。

波特图的另一半则是相位曲线(相移比频率),并被描绘成以“度”来表示的相移比频率关系。

波特相位曲线亦被绘成一种半对数曲线:x轴为采用对数刻度的频率(Hz)、y轴为采用线性刻度的相移(度),y轴最好是采用方便的每主格45°刻度。

图字(上、下):Aol曲线、幅度曲线、频率、相位曲线。

幅度波特图要求将电压增益转换成分贝(dB) 。

运算放大器的稳定性4―环路稳定性主要技巧与经验

运算放大器的稳定性4―环路稳定性主要技巧与经验运算放大器的稳定性第4部分(共15部分):环路稳定性主要技巧与经验作者:Tim Green,TI公司本系列的第4部分着重讨论了环路稳定性的主要技巧与经验。

首先,我们将讨论45度相位及环路增益带宽准则,考察了在Aol 曲线与1/β曲线以及环路增益曲线Aolβ中的极点与零点之间的互相转化关系。

我们还将讨论用于环路增益稳定性分析的频率“十倍频程准则”。

这些十倍频程准则将被用于1/β、Aol及Aolβ曲线。

我们将给出运放输入网络ZI与反馈网络ZF的幅度“十倍频程准则”。

我们将开发一种用于在1/β曲线上绘制双反馈路径的技术,并将解释为何在使用双反馈路径时应该避免出现“BIG NOT”这种特殊情况。

最后,我们将给出一种便于使用的实际稳定性测试方法。

在本系列的第5部分中,这些关键工具的综合使用使我们能够系统而方便地稳定一个带有复杂反馈电路的实际运放应用。

环路增益带宽准则已确立的环路稳定性标准要求在fcl处相移必须小于180度,fcl是环路增益降为零时的频率。

在fcl处的相移与整个180度相移之间的差定义为相位余量。

图4.0详细给出了建议用于实际电路的经验,亦即在整个环路增益带宽(f≤fcl)中设计得到135度的相移(对应于45度的相位余量)。

这是考虑到,在实际电路中存在着功率上升、下降及瞬态情况,在这些情况下,运放在Aol曲线上的改变可能会导致瞬态振荡。

而这种情况在功率运放电路中是特别不希望看到的。

由于存在寄生电容与印制板布局寄生效应,因此这种经验还考虑在环路增益带宽中用额外的相位余量来考虑实际电路中的附加相移的。

此外,当环路增益带宽中相位余量小于45度时,即可能在闭环传输函数中导致不必要的尖峰。

相位余量越低及越靠近fcl,则闭环尖峰就会越明显。

180135-135oFrequency90(Hz)450-45Loop Stability Criteria:<-180 degree phase shift at fcl -135 degree phase shift at all frequencies <fcl Why?: Because Aolis not always “Typical” Power-up, Power-down,Power-trans ient ?Undefined “Typical”Aol Allows for phase shift due to real world Layout & Component Parasitics图4.0:环路增益带宽准则图字(上下、左右):Aolβ(环路增益)相位曲线、-135°“相移”、频率(Hz)、45°“相位余量”环路稳定性标准:在fcl处相移< -180度θ设计目的:在所有< fcl的频率上,都有相移≤-135度原因:因为Aol(开环增益)并不总是“典型”,考虑到实际电路布局与器件的寄生效应,存在着功率上升、下降及暂态现象→这些是未定义的“典型”Aol。

运放环路稳定性

运算放大器的稳定性第4部分(共15部分):环路稳定性主要技巧与经验作者:Tim Green,TI公司本系列的第4部分着重讨论了环路稳定性的主要技巧与经验。

首先,我们将讨论45度相位及环路增益带宽准则,考察了在Aol 曲线与1/β曲线以及环路增益曲线Aolβ中的极点与零点之间的互相转化关系。

我们还将讨论用于环路增益稳定性分析的频率“十倍频程准则”。

这些十倍频程准则将被用于1/β、Aol及Aolβ曲线。

我们将给出运放输入网络ZI与反馈网络ZF的幅度“十倍频程准则”。

我们将开发一种用于在1/β曲线上绘制双反馈路径的技术,并将解释为何在使用双反馈路径时应该避免出现“BIG NOT”这种特殊情况。

最后,我们将给出一种便于使用的实际稳定性测试方法。

在本系列的第5部分中,这些关键工具的综合使用使我们能够系统而方便地稳定一个带有复杂反馈电路的实际运放应用。

环路增益带宽准则已确立的环路稳定性标准要求在fcl处相移必须小于180度,fcl是环路增益降为零时的频率。

在fcl处的相移与整个180度相移之间的差定义为相位余量。

图4.0详细给出了建议用于实际电路的经验,亦即在整个环路增益带宽(f≤fcl)中设计得到135度的相移(对应于45度的相位余量)。

这是考虑到,在实际电路中存在着功率上升、下降及瞬态情况,在这些情况下,运放在Aol曲线上的改变可能会导致瞬态振荡。

而这种情况在功率运放电路中是特别不希望看到的。

由于存在寄生电容与印制板布局寄生效应,因此这种经验还考虑在环路增益带宽中用额外的相位余量来考虑实际电路中的附加相移的。

此外,当环路增益带宽中相位余量小于45度时,即可能在闭环传输函数中导致不必要的尖峰。

相位余量越低及越靠近fcl,则闭环尖峰就会越明显。

18013545Frequency(Hz)90θ-45-135oDesign for: <Loop Stability Criteria:<-180 degree phase shift at fcl-135 degree phase shift at all frequencies <fclWhy?:Because Aol is not always “Typical”Power-up, Power-down, Power-transient ÆUndefined “Typical”AolAllows for phase shift due to real world Layout & Component Parasitics图4.0:环路增益带宽准则图字(上下、左右):Aolβ(环路增益)相位曲线、-135°“相移”、频率 (Hz)、45°“相位余量”环路稳定性标准:在fcl处相移< -180度设计目的:在所有< fcl 的频率上,都有相移≤ -135度原因:因为Aol (开环增益)并不总是“典型”,考虑到实际电路布局与器件的寄生效应,存在着功率上升、下降及暂态现象→这些是未定义的“典型” Aol 。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

运放稳定性分析环路稳定性基础引言本系列所采用的所有技术都将“以实例来定义”,而不管它在其他应用中能否用普通公式来表达。

为便于进行稳定性分析,我们在工具箱中使用了多种工具,包括数据资料信息、技巧、经验、SPICE仿真以及真实世界测试等,都将用来加快我们的稳定运放电路设计。

尽管很多技术都适用于电压反馈运放,但上述这些工具尤其适用于统一增益带宽小于20MHz的电压反馈运放。

选择增益带宽小于20MHz的原因是,随着运放带宽的增加,电路中的其他一些主要因素会形成回路,如印制板(PCB) 上的寄生电容、电容中的寄生电感以及电阻中的寄生电容与电感等。

我们下面介绍的大多数经验与技术并非仅仅是理论上的,而且是从利用增益带宽小于20MHz的运放、实际设计并构建真实世界电路中得来的。

本系列的第1部分回顾了进行稳定性分析所需的一些基本知识,并定义了将在整个系列中使用的一些术语。

波特图(曲线)基础幅度曲线的频率响应是电压增益改变与频率改变的关系。

这种关系可用波特图上一条以分贝(dB) 来表示的电压增益比频率(Hz) 曲线来描述。

波特幅度图被绘成一种半对数曲线:x轴为采用对数刻度的频率(Hz)、y轴则为采用线性刻度的电压增益(dB) ,y轴最好是采用方便的每主格45°刻度。

波特图的另一半则是相位曲线(相移比频率),并被描绘成以“度”来表示的相移比频率关系。

波特相位曲线亦被绘成一种半对数曲线:x轴为采用对数刻度的频率(Hz)、y轴为采用线性刻度的相移(度),y轴最好是采用方便的每主格45°刻度。

幅度波特图要求将电压增益转换成分贝(dB) 。

进行增益分析时,我们将采用以dB(定义为20Log10A)表示的电压增益,其中A为以伏/伏表示的电压增益。

在电压增益波特图上,增益随频率变化的斜线可定义成按+20dB/decade或-20dB/decade增加或减小。

另一种描述同样斜线的方法是按+6dB/octave 或-6dB/octave增加或减小(参见图1.4)以下推导证明了20dB/decade与6dB/octave的等效性:?A(dB) = A(dB) at fb – A(dB) at fa?A(dB) = [Aol(dB) - 20log10(fb/f1)] – [Aol(dB) - 20log10(fa/f1)]?A(dB) = Aol(dB) - 20log10(fb/f1) – Aol(dB) + 20log10(fa/f1)]?A(dB) = 20log10(fa/f1) – 20Log10(fb/f1)]?A(dB) = 20log10(fa/fb)?A(dB) = 20log10(1k/10k) = -20dB/decade?A(dB) = 20log10(fb/fc)?A(dB) = 20log10(10k/20k) = -6db/octave-20dB/decade = -6dB/octave因此:+20dB/decade = +6dB/octave -20dB/decade = -6dB/octave+40dB/decade = +12dB/octave -40dB/decade = -12dB/octave+60dB/decade = +18dB/Octave -60dB/decade = -18dB/Octave极点à单个极点响应在波特图(幅度或增益曲线)上具有按-20dB/decade 或-6db/octave斜率下降的特点。

在极点位置,增益为直流增益减去3dB。

在相位曲线上,极点在频率fP上具有-45°的相移。

相位在fP的两边以-45°/decade的斜率变化为0°和-90°。

单极点可用图1.5中的简单RC低通网络来表示。

请注意极点相位是如何影响直到高于(或低于)极点频率10倍频程处的频率的。

零点à单个零点响应在波特图(幅度或增益曲线)上具有按+20dB/decade 或+6db/octave斜率上升(对应于下降)的特点。

在零点位置,增益为直流增益加3dB。

在相位曲线上,零点在其频率fz上具有+45°的相移。

相位在fz的两边以+45°/decade斜率变化为0°与+90°。

单零点可用图1.6中的简单RC高通网络来表示。

请注意零点相位是如何影响直到高于(或低于)零点频率10倍频程处的频率的。

在波特幅度图上,很容易测量给定极点或零点的频率。

由于x轴为频率的对数刻度,故这种技术允许用距离比来准确及迅速地确定感兴趣的极点或零点的频率。

图1.7显示这种“对数刻度技巧”。

直观元件模型大多数运放应用都采用四种关键元件的组合,即:运放、电阻、电容和电感。

为便于进行稳定性分析,最好是能拥有这些关键元件的“直观模型”。

用于交流稳定性分析的直观运放模型如图1.8所示。

IN+ 与IN- 端之间的差分电压先被放大1倍并转化为单端交流电压源VDIFF, VDIFF然后再被放大K(f) 倍,其中K(f) 代表数据资料中的Aol(开环增益比频率曲线)。

由此得到的电压VO再后接运放开环、交流小信号及输出电阻RO。

电压通过RO后即为VOUT。

图1.10定义用于交流稳定性分析的直观电容模型,包括三个不同的工作区。

在“直流”区,电容将被看成是开路。

在“高频”区,电容则被看成是短路。

在这二者之间,电容将被看成是一个受频率控制的电阻(阻抗1/Xc随频率增加而减小)。

图1.11所示的SPICE仿真结果显示直观电容模型随频率变化的关系。

图1.12定义用于交流稳定性分析的直观电感模型,包括三个不同的工作区。

在“直流”区,电感将被看成是短路。

在“高频”区,电感则被看成是开路。

在这二者之间,电感将被看成是一个受频率控制的电阻(阻抗XL随频率增加而增加)。

图1.13所示的SPICE仿真结果显示出直观电感模型随频率变化的关系。

稳定性标准图1.14的下部显示代表一个带反馈运放电路的传统控制环路模型框图;上部显示与控制环路模型相对应的典型带反馈运放电路。

我们将这种带反馈运放电路称为“运放环路增益模型”。

请注意,Aol为运放数据资料Aol,且为运放的开环增益。

β(贝它)为从VOUT上作为反馈返回的输出电压量。

本例中的β网络为一个电阻反馈网络。

在推导VOUT/VIN时,我们能看到,可直接用Aol 及β来定义闭环增益函数。

从图1.14所示的运放开环增益模型中,我们能得出稳定闭环运放电路的标准。

详细推导如图1.15所示。

在频率fcl上,环路增益(Aolβ) 为1或0dB,如果环路增益相移为+/-180°,则电路不稳定!在fcl上,环路增益相移距离180°的相位称为环路增益相位余量。

对于临界阻尼表现良好的闭环响应,我们要求环路增益相位余量大于45°。

环路稳定性测试由于环路稳定性由环路增益(Aolβ) 的幅度与相位曲线决定,因此我们需要知道如何才能方便地分析环路增益幅度与相位。

为做到这一点,我们需要打破闭环运放电路,并将一个小信号交流源插入到环路中,然后再测量幅度与相位并绘出完整的环路增益曲线图。

图1.16显示运放环路增益控制模型的等效控制环路框图、以及我们准备用于环路增益测试的技术。

在分析用SPICE仿真构建的电路时,传统环路增益法利用一个电感及电容将闭环运放电路打破。

很大的电感值可确保环路在直流上闭合(要求SPICE 仿真能在进行交流分析以前先计算出直流工作点),但在感兴趣的交流频率上打开。

很大的电容值可确保交流小信号源与直流隔开,但可直接与感兴趣的频率相连。

图1.17显示用于传统环路增益测试的SPICE设置示意图。

在用SPICE仿真一个电路之前,我们想知道近似结果如何。

请记住GIGO(垃圾进,垃圾出)!!贝它(β) 及其倒数(1/β) 连同数据资料Aol曲线,可在运行SPICE以前为我们提供一种用于环路增益分析一阶近似的强大方法。

在后续几节中,我们将介绍计算(β) 及其倒数(1/β) 的技巧与经验。

图 1.18定义运放电路的贝它(β) 网络。

Aol曲线上叠加的1/β曲线,可提供环路增益(Aolβ) 曲线究竟如何的清晰画面。

从图1.19中的推导中,我们可清楚地看出,当我们以dB值来在Aol 曲线上绘出1/β时,Aolβ幅度曲线即为Aol 与1/β之差。

请注意,Aolβ随频率的增加而减小。

Aolβ是用于纠正VOUT/VIN或闭环响应中误差的增益。

因此,随着Aolβ减小,VOUT/VIN响应精度降低,直到Aolβ降为0dB、而VOUT/VIN响应完全跟随Aol为止。

一旦我们在Aol上绘出1/β,有一种称为“闭合速度” 的简单一阶稳定性检查法。

这种闭合速度稳定性检查,定义为1/β曲线与Aol曲线在fcl上(此时环路增益为0dB)的“闭合速度”。

40db/decade的闭合速度意味着不稳定,因为它意味着在fcl以前有两个极点,而这可能意味着180°的相移。

图1.20给出了4个例子,并将其各自的闭合速度计算如下:fcl1: Aol-1/β1 = -20dB/decade - +20dB/decade = -40dB/decade à 40dB/decade 闭合速度与不稳定fcl2: Aol-1/β2 = -20dB/decade - 0dB/decade = -20dB/decade à 20dB/decade闭合速度与稳定fcl3: Aol-1/β3 = -40dB/decade - 0dB/decade = -40dB/decade à 40dB/decade闭合速度与不稳定fcl4: Aol-1/β4 = -40dB/decade - -20dB/decade = -20dB/decade à 20dB/decade 闭合速度与稳定环路增益稳定性举例环路增益分析举例(图1.21)用来说明我们如何能从绘制在Aol曲线上的1/β曲线来分析运放的稳定性。

这里,随着频率的增加,电容CF逐渐趋于短路,从而分别随频率的增加而降低β曲线的幅度(亦即电压反馈随频率增加而减小)或抬高1/β曲线的幅度。

从闭合速度标准来看,我们预计该电路不稳定。

从Aol曲线上的1/β曲线,我们能绘出Aolβ(环路增益)幅度曲线(图1.22)。

从环路增益幅度曲线,我们又能绘出环路增益相位曲线。

从Aol曲线上的1/β曲线绘出Aolβ曲线的规则很简单:Aol曲线上的极点和零点即为Aolβ曲线上的极点和零点;1/β曲线上的极点和零点则为Aolβ曲线上的零点与极点。

记住这一点的一种简单方法是,β用于Aolβ曲线,而1/β为β的倒数,因此我们预计Aolβ曲线会采用1/β曲线上极点与零点的倒数,而极点的倒数为零点,零点的倒数为极点。