先行进位加法器教材

先行进位加法器教材

实验四32位先行进位加法器一、功能概述串行进位加法器延时很大,每级的输出结果都要等上一级的进位到来才可以求和算出结果,这次实验对普通全加器进行改良,改良为先行进位加法器。

先行进位加法器,各级的进位彼此是独立产生,只与输入数据A,B和C_in有关,将各级间的进位级联传播给去掉了,这样就可以减小进位产生的延时。

每个等式与只有三级延迟的电路对应,第一级延迟对应进位产生信号和进位传递信号,后两级延迟对应上面的积之和。

通过这种进位方式实现的加法器称为超前进位加法器。

因为各个进位是并行产生的,所以是一种并行进位加法器。

二、实验原理1、设二进制加法器第i位为A i,B i,输出为S i,进位输入为C i,进位输出为C i+1,则有:S i=A i⊕B i⊕C i(1-1)C i+1 =A i * B i+ A i *C i+ B i*C i =A i * B i+(A i+B i)* C i(1-2)令G i = A i * B i , P i = A i+B i,则C i+1= G i+ P i *C i当A i和B i都为1时,G i = 1,产生进位C i+1 = 1当A i和B i有一个为1时,P i = 1,传递进位C i+1= C i因此G i定义为进位产生信号,P i定义为进位传递信号。

G i的优先级比P i高,也就是说:当G i = 1时(当然此时也有P i = 1),无条件产生进位,而不管C i是多少;当G i=0而P i=1时,进位输出为C i,跟C i之前的逻辑有关。

下面推导4位超前进位加法器。

设4位加数和被加数为A 和B,进位输入为C in,进位输出为C out,对于第i位的进位产生G i = A i·B i ,进位传递P i=A i+B i , i=0,1,2,3。

于是这各级进位输出,递归的展开Ci,有:C0 = C inC1=G0 + P0·C0C2=G1 + P1·C1 = G1 + P1·G0 + P1·P0▪C0C3=G2+ P2·C2= G2+ P2·G1+ P2·P1·G0+P2·P1·P0·C0C4=G3+ P3·C3= G3+ P3·G2+ P3·P2·G1+P3·P2·P1·G0 + P3·P2·P1·P0·C0 (1-3)C out=C4由此可以看出,各级的进位彼此独立产生,只与输入数据Ai、Bi和Cin有关。

第2章 加法器

应用于四个4位先行进位加法器,则有:

Cm1=Gm1+Pm1C0 Cm2=Gm2+Pm2Cm1 = Gm2+ Pm2Gm1 + Pm2 Pm1C0

Cm3=Gm3+Pm3Cm2 = Gm3+ Pm3Gm2 + Pm3Pm2Gm1+ Pm3 Pm2 Pm1C0

Cm4=Gm4+Pm4Cm3 = Gm4+ Pm4Gm3 + Pm4Pm3Gm2+ Pm4Pm3Pm2 Gm1+ Pm4Pm3Pm2P m1C0

cc33cc44cc22cc11gg22pp33gg33pp44gg44gg11pp22pp11先行进位产生电路cc00先行进位线路ff44cc33aa44bb44pp44gg44faff33cc22aa33bb33pp33gg33faff22cc11aa22bb22pp22gg22facc00ff11aa11bb11pp11gg11facc4444位先行进位加法器?理论上讲这种先行进位加法器可以扩充到n位字长但是当加法器位数增加时进位函数ci1会变得越来越复杂n位字长的加法器最高进位位需要一个n1位输入的或门和n1位输入的与门电路实现这给电路的实现带来了困难

• 在行波进位加法器中,进位信号的逻辑表 达式为: Ci= Gi+Pi Ci-1 • C1=G1+P1C0 • C2=G2+P2C1 • C3=G3+P3C2 • ………… • Cn=Gn+PnCn-1 可见,后一级的进位直接依赖前一级,进 位是逐级形成的,最长进位延迟时间为 2.5nty,与n成正比。可见,行波进位加法 器的加法速度比较低。

• 则当实现加法运算时,给出A→FA及B→FA 两个控制命令,则将[A]补和[B]补送到加法 器 FA 的两个输入端, FA 完成 [A] 补+ [B] 补 的加法过程,然后通过FA→A命令将加法运 算结果存入A寄存器。 • 如果实现减法运算,给出 A→FA 及 /B→FA 以及1→C0控制命令,则将[A]补和[-B]补送 到加法器FA的两个输入端,FA完成[A]补+ [-B]补的加法过程,然后通过 FA→A命令将 减法运算结果存入A寄存器。

先行进位加法器

实验四32位先行进位加法器一、功能概述串行进位加法器延时很大,每级的输出结果都要等上一级的进位到来才可以求和算出结果,这次实验对普通全加器进行改良,改良为先行进位加法器。

先行进位加法器,各级的进位彼此是独立产生,只与输入数据A,B和C_in有关,将各级间的进位级联传播给去掉了,这样就可以减小进位产生的延时。

每个等式与只有三级延迟的电路对应,第一级延迟对应进位产生信号和进位传递信号,后两级延迟对应上面的积之和。

通过这种进位方式实现的加法器称为超前进位加法器。

因为各个进位是并行产生的,所以是一种并行进位加法器。

二、实验原理1、设二进制加法器第i位为A i,B i,输出为S i,进位输入为C i,进位输出为C i+1,则有:S i=A i⊕B i⊕C i(1-1)C i+1 =A i * B i+ A i *C i+ B i*C i =A i * B i+(A i+B i)* C i(1-2)令G i = A i * B i , P i = A i+B i,则C i+1= G i+ P i *C i当A i和B i都为1时,G i = 1,产生进位C i+1 = 1当A i和B i有一个为1时,P i = 1,传递进位C i+1= C i因此G i定义为进位产生信号,P i定义为进位传递信号。

G i的优先级比P i高,也就是说:当G i = 1时(当然此时也有P i = 1),无条件产生进位,而不管C i是多少;当G i=0而P i=1时,进位输出为C i,跟C i之前的逻辑有关。

下面推导4位超前进位加法器。

设4位加数和被加数为A 和B,进位输入为C in,进位输出为C out,对于第i位的进位产生G i = A i·B i ,进位传递P i=A i+B i , i=0,1,2,3。

于是这各级进位输出,递归的展开Ci,有:C0 = C inC1=G0 + P0·C0C2=G1 + P1·C1 = G1 + P1·G0 + P1·P0▪C0C3=G2+ P2·C2= G2+ P2·G1+ P2·P1·G0+P2·P1·P0·C0C4=G3+ P3·C3= G3+ P3·G2+ P3·P2·G1+P3·P2·P1·G0 + P3·P2·P1·P0·C0 (1-3)C out=C4由此可以看出,各级的进位彼此独立产生,只与输入数据Ai、Bi和Cin有关。

先行进位加法器课件

实验四32位先行进位加法器一、功能概述串行进位加法器延时很大,每级的输出结果都要等上一级的进位到来才可以求和算出结果,这次实验对普通全加器进行改良,改良为先行进位加法器。

先行进位加法器,各级的进位彼此是独立产生,只与输入数据A,B 和C_in有关,将各级间的进位级联传播给去掉了,这样就可以减小进位产生的延时。

每个等式与只有三级延迟的电路对应,第一级延迟对应进位产生信号和进位传递信号,后两级延迟对应上面的积之和。

通过这种进位方式实现的加法器称为超前进位加法器。

因为各个进位是并行产生的,所以是一种并行进位加法器。

二、实验原理1、设二进制加法器第i位为A i,B i,输出为S i,进位输入为C i,进位输出为C i+1,则有:S i=A i⊕B i⊕C i(1-1)C i+1 =A i * B i+ A i *C i+ B i*C i =A i * B i+(A i+B i)* C i(1-2)令G i = A i * B i , P i = A i+B i,则C i+1= G i+ P i *C i当A i和B i都为1时,G i = 1,产生进位C i+1 = 1当A i和B i有一个为1时,P i = 1,传递进位C i+1= C i因此G i定义为进位产生信号,P i定义为进位传递信号。

G i的优先级比P i高,也就是说:当G i = 1时(当然此时也有P i = 1),无条件产生进位,而不管C i是多少;当G i=0而P i=1时,进位输出为C i,跟C i之前的逻辑有关。

下面推导4位超前进位加法器。

设4位加数和被加数为A和B,进位输入为C in,进位输出为C out,对于第i位的进位产生G i = A i·B i,进位传递P i=A i+B i , i=0,1,2,3。

于是这各级进位输出,递归的展开Ci,有:C0 = C inC1=G0 + P0·C0C2=G1 + P1·C1 = G1 + P1·G0 + P1·P0▪C0C3=G2 + P2·C2 = G2 + P2·G1 + P2·P1·G0 + P2·P1·P0·C0C4=G3 + P3·C3 = G3 + P3·G2 + P3·P2·G1 + P3·P2·P1·G0 + P3·P2·P1·P0·C0 (1-3)C out=C4由此可以看出,各级的进位彼此独立产生,只与输入数据Ai、Bi和Cin有关。

数字电路课程设计之超前进位加法器

reg

Cin;

wire[3:0] S;

wire

Cout;

carry_look_add CAL (.A(A),.B(B),.Cin(Cin),.Cout(Cout),.S(S)); initial begin

#10 A=4'd0;B=4'd0;Cin=0; #10 A=4'd11;B=4'd1;Cin=0; #10 A=4'd10;B=4'd12;Cin=0; #10 A=4'd11;B=4'd4;Cin=0; #100 $stop; end endmodule

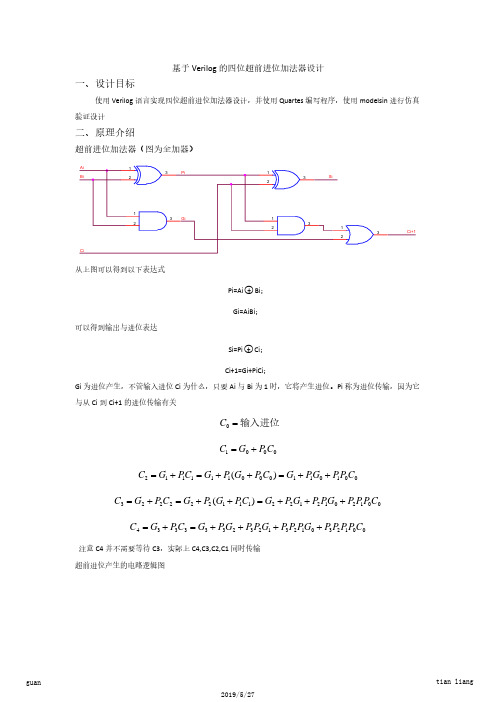

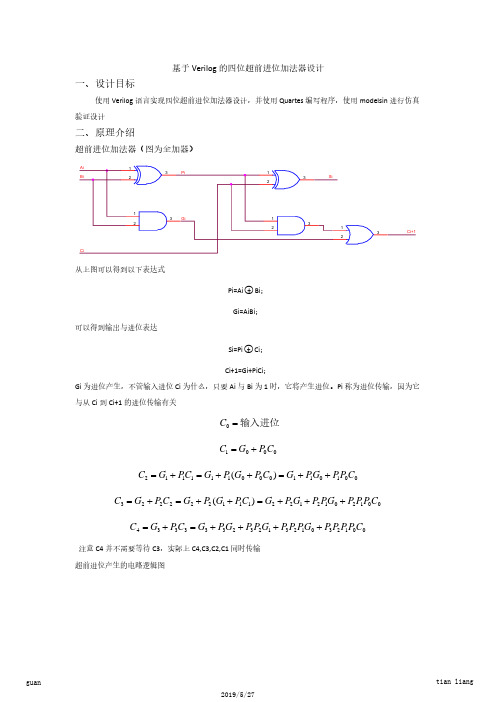

Pi=Ai○+ Bi;

可以得到输出与进位表达

Gi=AiBi;

Si=Pi○+ Ci;

Ci+1=Gi+PiCi; Gi 为进位产生,不管输入进位 Ci 为什么,只要 Ai 与 Bi 为 1 时,它将产生进位。Pi 称为进位传输,因为它 与从 Ci 到 Ci+1 的进位传输有关

C0 = 输入进位

C1 = G0 + P0C0

Half_Add H3(.a(A[2]),.b(B[2]),.s(v6),.c(v5));

Half_Add H4(.a(A[3]),.b(B[3]),.s(v8),.c(v7));

carry_look

CL1(.C0(Cin),.P0(v2),.G0(v1),.P1(v4),.G1(v3),.P2(v6),.G2(v5),.P3(v8),.G3(v7),.C1(o1),.C2(o2),.C3(o3),.C4(Cout));

注意 C4 并不需要等待 C3,实际上 C4,C3,C2,C1 同时传输 超前进位产生的电路逻辑图

课件:第三章 计算机的算术运算加减法

G4 P4

G3 P3

S 16~S 13

S 12~S 9

G2 P2 S 8~S 5

G1 P1 S 4~S 1

BCLA

C12

BCLA

C8

BCLA

C4

BCLA

C0

加法器

加法器

加法器

加法器

A 16~A 13

A 12~A 9

B 16~B 13

B 12~B 9

A 8~A 5 B 8~B 5

A 4~A 1 B 4~B 1

再经过2ty后,才能产生第2、3、4小组内的C5~C7、C9~C11、 C13~C15。

以典型的四位ALU芯片(SN74181)为例介绍ALU的结 构及应用。

得[x+y]补=0.0110,x+y=+0.0110

[例2]X=-11001,Y=-00011,求X+Y=? 解:[x]补=1,00111,[y]补=1,11101

[x]补 = 1,00111 +)[y]补 = 1,11101 [x+y]补 =1 1,00100

丢掉

验算:

x=-11001=(-25)10 Y=(-3)10 X+Y=(-28)10 =(-11100)2

S 8~S 5

S 4~S 1

C16

4位C L A

C12

4位C L A

C8

4位C L A

C4

4位C L A

C0

加法器

加法器

加法器

加法器

A 1 6~A 1 3

A 1 2~A 9

B 1 6~B 1 3

B 1 2~B 9

A 8~A 5

B 8~B 5

A 4~A 1

超前进位加法器

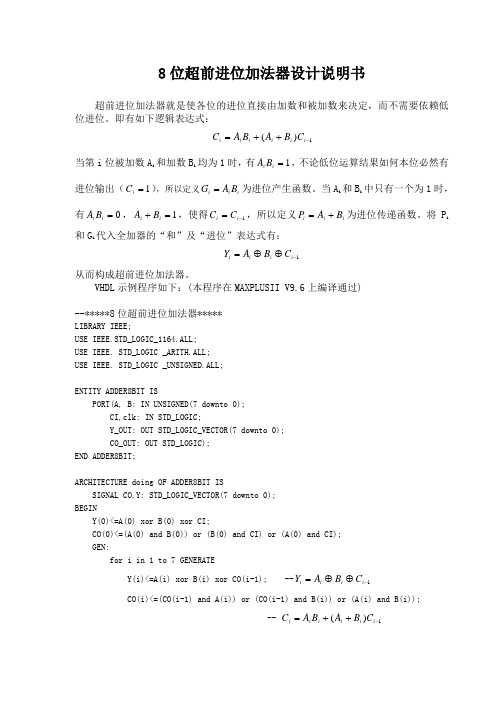

8位超前进位加法器设计说明书超前进位加法器就是使各位的进位直接由加数和被加数来决定,而不需要依赖低位进位。

即有如下逻辑表达式:1)(-++=i i i i i i C B A B A C当第i 位被加数A i 和加数B i 均为1时,有1=i i B A ,不论低位运算结果如何本位必然有进位输出(1=i C ),所以定义i i i B A G =为进位产生函数。

当A i 和B i 中只有一个为1时,有0=i i B A ,1=+i i B A ,使得1-=i i C C ,所以定义i i i B A P +=为进位传递函数。

将P i 和G i 代入全加器的“和”及“进位”表达式有:1-⊕⊕=i i i i C B A Y从而构成超前进位加法器。

VHDL 示例程序如下:(本程序在MAXPLUSII V9.6上编译通过)--*****8位超前进位加法器*****LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE. STD_LOGIC _ARITH.ALL;USE IEEE. STD_LOGIC _UNSIGNED.ALL;ENTITY ADDER8BIT ISPORT(A, B: IN UNSIGNED(7 downto 0);CI,clk: IN STD_LOGIC;Y_OUT: OUT STD_LOGIC_VECTOR(7 downto 0);CO_OUT: OUT STD_LOGIC);END ADDER8BIT;ARCHITECTURE doing OF ADDER8BIT ISSIGNAL CO,Y: STD_LOGIC_VECTOR(7 downto 0);BEGINY(0)<=A(0) xor B(0) xor CI;CO(0)<=(A(0) and B(0)) or (B(0) and CI) or (A(0) and CI);GEN:for i in 1 to 7 GENERATEY(i)<=A(i) xor B(i) xor CO(i-1); --1-⊕⊕=i i i i C B A YCO(i)<=(CO(i-1) and A(i)) or (CO(i-1) and B(i)) or (A(i) and B(i)); -- 1)(-++=i i i i i i C B A B A Cend GENERATE;process(clk)beginif clk'event and clk='1' thenY_OUT<=Y(7) & Y(6) & Y(5) & Y(4) & Y(3) & Y(2) & Y(1) & Y(0);CO_OUT<=CO(7);end if;end process;END doing;附:仿真时序波形。

数字电路课程设计之超前进位加法器

# MACRO ./mul_run_msim_rtl_verilog.do PAUSED at line 14

通过查阅资料将 Verilog 测试文件

Timsbench 文件没有实例化,修改为

修改后仿真 OK 参考文献: 1.数字设计与 Verilog 实现 M.Morris Mano 著 第五版

Pi=Ai○+ Bi;

可以得到输出与进位表达

Gi=AiBi;

Si=Pi○+ Ci;

Ci+1=Gi+PiCi; Gi 为进位产生,不管输入进位 Ci 为什么,只要 Ai 与 Bi 为 1 时,它将产生进位。Pi 称为进位传输,因为它 与从 Ci 到 Ci+1 的进位传输有关

C0 = 输入进位

C1 = G0 + P0C0

instance name in instantiation of 'carry_look_add'.

#

#

Region: /carry_look_add_tb

# Error loading design

# Error: Error loading design

#

Pausing macro execution

基于 Verilog 的四位超前进位加法器设计

使用 Verilog 语言实现四位超前进位加法器设计,并使用 Quartes 编写程序,使用 modelsin 进行仿真

验证设计

二、原理介绍

超前进位加法器(图为全加器)

Ai

1

3

Pi

Bi

2

1

3

Si

2

1 3 Gi

2

Ci

1

3

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验四32 位先行进位加法器一、功能概述串行进位加法器延时很大,每级的输出结果都要等上一级的进位到来才可以求和算出结果,这次实验对普通全加器进行改良,改良为先行进位加法器。

先行进位加法器,各级的进位彼此是独立产生,只与输入数据A, B 和C_in 有关,将各级间的进位级联传播给去掉了,这样就可以减小进位产生的延时。

每个等式与只有三级延迟的电路对应,第一级延迟对应进位产生信号和进位传递信号,后两级延迟对应上面的积之和。

通过这种进位方式实现的加法器称为超前进位加法器。

因为各个进位是并行产生的,所以是一种并行进位加法器。

二、实验原理1、设二进制加法器第i位为A i, B i,输出为S,进位输入为C i, 进位输出为C i+i,则有:S=A i ㊉B i ㊉C i(1-1)C i+1 =A i * B i+ A i *C i+ B i*C i =A i * B i+(A i+B i)* C i(1-2)令G i = A i * B i , P i = A i+B i,贝y C i+1= G i+ P i *C i当A i和B i都为1时,G i = 1 ,产生进位C i+i = 1当A i和B i有一个为1时,P i = 1,传递进位C i+i= C i因此G i定义为进位产生信号,P i定义为进位传递信号。

G i的优先级比P i 高,也就是说:当G i = 1时(当然此时也有P i = 1),无条件产生进位,而不管C i 是多少;当G i=0 而P i=1 时,进位输出为C i,跟C i之前的逻辑有关。

下面推导 4 位超前进位加法器。

设 4 位加数和被加数为 A 和B,进位输入为C in,进位输出为C out,对于第i位的进位产生G i = A i •B i,进位传递P i=A i+B i , i=0,1,2,3。

于是这各级进位输出,递归的展开Ci,有:C0 = C inG=G o + P o •C oC2=G 1 + P1 •C 1 = G 1 + P1 •G 0 + P1 •P o ?C oC3=G 2 + P2 •C 2 = G2 + P2, G 1 + P2 •P1 •G o +P2 •P1 •P o •C oC4=G 3 + P3 •C 3 = G3 + P3, G 2 + P3 •P2 •G 1 +P3 •P 2 •P1 •G o + P 3 P2 •P1•P o •C o (1-3)C out=C4由此可以看出,各级的进位彼此独立产生,只与输入数据Ai、Bi 和Cin 有关。

2、接口说明序号 接口信号名称方向说明备注1 A[31:0] I 输入数据2 B[31:0] I 输入数据3 S[31:0] O 加法结果4countO最高位进位3、结构框图三、实验方案方案一:分为两个模块:1个4位add_4和1个add_32,其中add_32 调用4个add_4.首先设计4位超前进位加法器:框图如下:设计好四位的之后,开始调用四位的实现32位的方案二:分为五个模块:(1)计算传播值和产生值模块:|L —7 \4位 ^28 4位C^4 4位 - 4位CLACLAA15~12 B 15~12 A11~8 B11~8 A7~4 B 7-4 A3~o B 3~014位L CLAC 12 4位 CLA4位 CLAC4<-l 4位 CLA1 F 1 r卄* g x1 p x1 C 16g x1g x0 Px0C s24位 BCLApgr 5 CLA CLA 9~16g m4 P m4g m7 P m7P m6 gm5 pm54位 BCLAA31~28 B 31~28 A27~24 B 27~24 A23~20 B23~20 A19~16 B 19~161~8gm0 P mO16 位1 f f S7~4gm2Pm24位 BCLAmlPm1* * Si5~i2 g m3P m31 T S3~0模块(2)超前进位模块:cla 模块(3)加法求和模块:sum 模块(4)求和并按输出a,b,c_in 分组:bit_slice 模块(5)32 位超前进位加法器总模块:cla_32 总框图:四、验证方案:对32 位的两个输入赋值:当a=32'b1000_0001_0111_1011_1101_1001_1101_1000;b=32'b0111_1000_ 0001_ 1000_ 1100_ 0111_ 0101_ 0001;c_in=1'b0;结果:s=32'b11111001;_1001 _1001 _0100 _1010 _0001 _0010_当a=32'b1000_0001_1000;0111_ 1011_ 1101_ 1001_ 1101_0001;b=32'b0111_1000_0001_ 1000_ 1100_ 0111_ 0101_c_in=1'b1;结果:s=32'b1111 _1001 _1001 _0100 _1010 _0001 _0010_ 1010; 来对波形进行观察,看波形是否正确。

五、实验代码:方案一:(1)add_32 模块顶层模块:(2) 4位add_4模块方案二:(1) cla_32顶层模块:module cla_32(a,b,c_in,s,count ); input [31:0] a,b;input c_in;output [31:0] s;output count;wire [7:0] gg,gp,gc;wire [3:0] ggg,ggp,ggc;wire gggg,gggp;bit_sliceb1(.a(a[3:0]),.b(b[3:0]),.c_in(gc[0]),.s(s[3:0]),.gp(gp[0]),.gg(gg[0 ])); bit_sliceb2(.a(a[7:4]),.b(b[7:4]),.c_in(gc[1]),.s(s[7:4]),.gp(gp[1]),.gg(gg[1 ])); bit_sliceb3(.a(a[11:8]),.b(b[11:8]),.c_in(gc[2]),.s(s[11:8]),.gp(gp[2]),.gg(g g[2]) );bit_sliceb4(.a(a[15:12]),.b(b[15:12]),.c_in(gc[3]),.s(s[15:12]),.gp(gp[3]),.g g(g g[3]));bit_sliceb5(.a(a[19:16]),.b(b[19:16]),.c_in(gc[4]),.s(s[19:16]),.gp(gp[4]),.g g(g g[4]));bit_sliceb6(.a(a[23:20]),.b(b[23:20]),.c_in(gc[5]),.s(s[23:20]),.gp(gp[5]),.gg(gg[5]));bit_sliceb7(.a(a[27:24]),.b(b[27:24]),.c_in(gc[6]),.s(s[27:24]),.gp(gp[6]), .gg(g g[6]));bit_sliceb8(.a(a[31:28]),.b(b[31:28]),.c_in(gc[7]),.s(s[31:28]),.gp(gp[7]), .gg(g g[7]));clac0(.p(gp[3:0]),.g(gg[3:0]),.c_in(ggc[0]),.c(gc[3:0]),.gp(ggp[0]),.gg (ggg[ 0]));clac1(.p(gp[7:4]),.g(gg[7:4]),.c_in(ggc[1]),.c(gc[7:4]),.gp(ggp[1]),.gg (ggg[1]));assign ggp[3:2]=2'b11;assign ggg[3:2]=2'b00;cla c2(.p(ggp),.g(ggg),.c_in(c_in),.c(ggc),.gp(gggp),.gg(gggg)); assign count=gggg|(gggp&c_in);endmodule2)pg 模块:module pg(a,b,p,g);input [3:0] a,b;output [3:0] p,g;assign p=a A b;assign g=a&b;endmodule(3) cla 模块:module cla(p,g,c_in,c,gp,gg); input [3:0] p,g;input c_in;output [3:0] c;output gp,gg;function [99:0] do_cla;input [3:0] p,g;input c_in;begin:labelinteger i;reg gp,gg;reg [3:0] c;gp=p[0];gg=g[0];c[0]=c_in;for(i=1;i<4;i=i+1)begingp=gp&p[i];gg=(gg&p[i])|g[i]; c[i]=(c[i-1]&p[i-1])|g[i-1]; end do_cla={c,gp,gg};endendfunctionassign {c,gp,gg}=do_cla(p,g,c_in);endmodule( 4) sum 模块:module sum(a,b,c,s );input [3:0] a,b,c;output [3:0] s;wire [3:0] t=a A b;assign s=tAc;endmodule5) bit_slice 模块:module bit_slice(a,b,c_in,s,gp,gg ); input [3:0] a,b;input c_in;output [3:0] s;output gp,gg;wire [3:0]p,g,c;pg i1(a,b,p,g);cla i2(p,g,c_in,c,gp,gg);sum i3(a,b,c,s);endmodule(6)激励代码:module cla32_tb;// Inputsreg [31:0] a;reg [31:0] b;reg c_in;// Outputswire [31:0] s;wire count;// Instantiate the Unit Under Test (UUT) cla_32 uut ( .a(a),.b(b),.c_in(c_in),.s(s),.count(count));initial begin// Initialize Inputsa = 0;b = 0;c_in = 0;// Wait 100 ns for global reset to finish#10a=32'b1000_ 0001 0111 1011_ 1101_ 1001 1101 _1000;b=32'b0111_ 1000 0001 1000_ 1100_ 0111 0101 _0001;c_in=1'b0;#10a=32'b1000_ 0001 0111 1011_ 1101_ 1001 1101 _1000;b=32'b0111_ 1000 0001 1000_ 1100_ 0111 0101 _0001;c_in=1'b1;// Add stimulus here end endmodule 六、波形图说明1、仿真波形2、结果说明对于三个输入:a=32'b1000_0001_0111_1011_1101_1001_1101_1000;b=32'b0111_1000_0001_1000_1100_0111_0101_0001; c_in=1'bO;结果与实验方案的相同,结果仿真正确.七、实验总结 对于这次实验,自己在老师布置完,努力做了几个下午,不 断调试才得到正确结果波形,是非常有收获的。