verilog编写六-十进制计数器

Verilog24小时计数器

VERILOG24小时多功能数字钟的设计班级:自动化学生:XXXXX 学号:XXXXXX1 设计目标掌握可编程逻辑器件的应用开发技术——设计输入、编译、仿真和器件编程;熟悉一种EDA软件使用与实验系统介绍;掌握Verilog HDL设计方法,设计一个多功能数字钟,满足以下要求:①能显示小时、分钟、秒钟(小时以24进制,时、分用显示器,秒用LED);②能调整小时、分钟的时间;③复位;2 实验装置586计算机,MAX+plusⅡ 10.2软件,专用编程电缆,EDA Pro2K数字实验装置等。

3 设计步骤和要求①在MAX+plusⅡ 10.2软件中,输入设计的原理图,采用Verilog HDL输入方式,采用分层模块的设计方法设计电路②对电路进行仿真分析;③选择器件,分配引脚,重新对设计项目进行编译和逻辑综合;④对EDA Pro2K数字实验装置中的FPGA器件进行在系统编程,并实际测试电路的逻辑功能(用实验板上的译码显示电路显示结果);4 具体步骤4.1 建立 Quartus 工程;1.打开 Quartus II 工作环境2.点击菜单项 File->New Project Wizard 帮助新建工程3.输入工程工作路径、工程文件名以及顶层实体名4.添加设计文件5.选择设计所用器件6.设置EDA工具7.查看新建工程总结在完成新建后,Quartus II 界面中Project Navigator 的Hierarchy 标签栏中会出现用户正在设计的工程名以及所选用的器件型号4.2 使用 Verilog HDL 完成设计输入代码如下:(1)数字钟顶层模块://*****************timeclock top block(top_clock.v)***************module clock_24(CLK,CP,nCR,EN,Adj_Min,Adj_Hour,SEG7_1,SEG7_2,SEG7_3,SEG7_4);input CLK,nCR,EN,Adj_Min,Adj_Hour; //定义输入端口变量output[7:0]SEG7_1,SEG7_2,SEG7_3,SEG7_4;output CP;wire CP;wire[7:0]Hour,Minute,Second; //说明变量的类型supply1 Vdd;wire MinL_EN,MinH_EN,Hour_EN; //定义中间变量freqDiv UO(CLK,CP);counter10 U1(Second[3:0],nCR,EN,CP); //秒计数器个位counter6 U2(Second[7:4],nCR,(Second[3:0]==4'h9),CP); //秒计数器十位assign MinL_EN=Adj_Min?Vdd:(Second==8'h59);assignMinH_EN=(Adj_Min&&(Minute[3:0]==4'h9))||(Minute[3:0]==4'h9)&&(Second==8' h59);counter10 U3(Minute[3:0],nCR,MinL_EN,CP); //分计数器个位counter6 U4(Minute[7:4],nCR,MinH_EN,CP); //分计数器十位//产生小时计数器使能信号。

FPGA实验二:基于HDL的十进制计数器

《FPGA》课程报告设计题目:基于HDL的十进制计数器学生班级:学生学号:学生姓名:指导教师:时间:成绩:一、实验目的:1.掌握基于语言的ISE设计全流程;2.熟悉、应用VerilogHDL描述数字电路;3.掌握基于Verilog的组合和时序逻辑电路的设计方法。

二、实验原理:本次实验是使用Verilog HDL进行编写十进制计数器与显示器代码而进行的实验,实验原理图如下:本次实验的内容包括十进制计数器模块,七段译码显示器模块,以及消抖模块。

十进制计数器:对输入时钟进行计数输入:CLK -------待计数的时钟CLR ---------异步清零信号,当CLR =1,输出复位为0,当CLR =0,正常计数ENA---------使能控制信号,当ENA=1,电路正常累加计数,否则电路不工作输出:SUM[3:0]---------- 计数值的个位。

即,在CLK上升沿检测到SUM=9时,SUM将被置0,开始新一轮的计数。

COUT ------------计数值的十位进位,即:只有在时钟CLK上升沿检测到SUM=9时,COUT将被置1,其余情况下COUT=0;LED显示驱动模块:输入:sum[3:0] -------待显示的数值out[6:0] ----------驱动数码管的七位数值七段数码管的字符显示真值表如下:消抖模块:三、实验过程:1.首先建立一个新的工程,添加一个新的Verilog Module,在其中编写十进制计数模块的代码,如下:module liao1(CLR,CLK,ENA,SUM,COUT);input CLR,CLK,ENA;output[3:0] SUM;output COUT;reg[3:0] SUM;reg COUT;always@(posedge CLK or posedge CLR)if(CLR)beginSUM<=4'b0000;COUT<=1'b0;endelseif(ENA)beginif(SUM==9)beginSUM<=4'b0000;COUT<=1'b1;endelsebeginSUM<=SUM+1'b1;COUT<=1'b0;endendendmodule然后执行综合,确认无误后,新建一个Test Bench WaveForm文件,进行仿真,仿真图如下:2.再新建一个Verilog Module,在其中编写七段数码显示模块的代码,如下:module liao2(SUM,out);input[3:0] SUM;output[6:0] out;reg [6:0] out;always @(SUM)begincase(SUM)4'b0000: out<=7'b0000001;4'b0001: out<=7'b1001111;4'b0010: out<=7'b0010010;4'b0011: out<=7'b0000110;4'b0100: out<=7'b1001100;4'b0101: out<=7'b0100100;4'b0110: out<=7'b0100000;4'b0111: out<=7'b0001111;4'b1000: out<=7'b0000000;4'b1001: out<=7'b0000100;default :out<=7'b0000001;endcaseendendmodule执行综合,确认无误后新建一个Test Bench WaveForm文件,进行仿真,仿真图如下:3.添加消抖模块,然后再新建一个Verilog Module,编写例化文件,制成顶层文件,其例化文件代码如下:module liao(CLK_50M,CLK,CLR,ENA,COUT,out);input CLR,CLK,ENA;input CLK_50M;output[6:0] out;output COUT;wire[3:0] SUM;debounce_module u1(CLK_50M,CLR,CLK,clk_out);liao1 u2(CLR,clk_out,ENA,SUM,COUT);liao2 u3(SUM,out);endmodule保存之后形成顶层文件:4.执行综合,确认无误后,根据实验指导书进行锁引脚操作:锁引脚完成后,修改、编辑约束文件:5.生成下载配置文件,下载到开发板进行经行验证。

verilog中数字的表示格式

一、概述Verilog是一种硬件描述语言,用于描述数字系统的行为和结构。

数字在Verilog中起着非常重要的作用,因为数字是数字系统中最基本的元素。

在Verilog中,数字的表示格式是非常重要的,因为它直接影响了数字系统的行为和性能。

本文将对Verilog中数字的表示格式进行探讨和分析。

二、十进制表示1. 在Verilog中,十进制数字可以直接以数字的格式进行表示,例如:```verilogmodule test;reg [31:0] num = 123;endmodule```2. 在这个例子中,数字123就是一个十进制数,它直接以数字的形式出现在代码中。

这种直接表示的方式非常简洁和直观,但有时可能会陷入十进制和二进制之间的转换困扰。

三、二进制表示1. 除了十进制表示外,Verilog还支持使用二进制数字进行表示。

例如:```verilogmodule test;reg [31:0] num = 32'b1010;endmodule```2. 这个例子中,数字1010以二进制的形式出现在代码中,其中32'b表示该数字为32位二进制数。

使用二进制表示可以帮助程序员更直观地理解数字的结构,但也可能增加代码的长度和复杂度。

四、八进制和十六进制表示1. 在Verilog中,还可以使用八进制和十六进制进行数字表示。

例如:```verilogmodule test;reg [31:0] num1 = 8'o123;reg [31:0] num2 = 16'h1A;endmodule```2. 这个例子中,数字123和1A分别以八进制和十六进制的形式出现在代码中。

使用八进制和十六进制表示可以进一步简化数字的表示方式,尤其对于大型数字系统来说,可以减少代码长度和提高可读性。

五、实数表示1. 在Verilog中,数字还可以表示为实数。

例如:```verilogmodule test;real num1 = 3.0;real num2 = 5.6e-3;endmodule```2. 这个例子中,数字3.0以实数的形式出现在代码中,其中5.6e-3表示5.6乘以10的负3次方。

计数器(1):Verilog常用写法

计数器(1):Verilog常⽤写法 计数器是⾮常基本的使⽤,没有计数器就⽆法处理时序。

我在学习时发现市⾯上有⼏种不同的计数器写法,⾮常有趣,在此记录下来:⼀、时序逻辑和组合逻辑彻底分开1.代码1//======================================================================2// --- 名称 : Count_13// --- 作者 : xianyu_FPGA4// --- ⽇期 : 2018-12-105// --- 描述 : 模10计数器,0到10循环累加6//======================================================================78module Count_19 (10input clk ,11input rst_n ,12output reg [ 3:0] cnt13 );1415//----------------------------------------------------------------------16//-- 组合电路17//----------------------------------------------------------------------18reg [ 3:0] cnt_n ;1920always @(*)begin21if(cnt == 4'd9)22 cnt_n = 4'd0;23else24 cnt_n = cnt + 1'b1;25end2627//----------------------------------------------------------------------28//-- 时序电路29//----------------------------------------------------------------------30always @(posedge clk or negedge rst_n)begin31if(!rst_n)32 cnt <= 4'b0;33else34 cnt <= cnt_n;35end3637endmodule3839/*40//----------------------------------------------------------------------41//-- 组合电路也可以这样写42//----------------------------------------------------------------------43wire [ 3:0] cnt_n ;4445assign cnt_n = (cnt==4'd9)? 4'd0 : cnt+1'b1;4647*/2.写法1的RTL视图3.写法2的RTL视图⼆、最常见的写法1.代码1//======================================================================2// --- 名称 : Count_23// --- 作者 : xianyu_FPGA4// --- ⽇期 : 2018-12-105// --- 描述 : 模10计数器,0到10循环累加6//======================================================================78module Count_29 (10input clk ,11input rst_n ,12output reg [ 3:0] cnt13 );1415always @(posedge clk or negedge rst_n)begin16if(!rst_n)17 cnt <= 4'd0;18else if(cnt==4'd9)19 cnt <= 4'd0;20else21 cnt <= cnt + 1'b1;22end23242526endmodule2.RTL视图三.代码⽚段写法1.代码1//====================================================================== 2// --- 名称 : Count_33// --- 作者 : xianyu_FPGA4// --- ⽇期 : 2018-12-105// --- 描述 : 模10计数器,0到10循环累加6//====================================================================== 78module Count_39//---------------------<端⼝声明>---------------------------------------10 (11input clk ,12input rst_n ,13output reg [ 3:0] cnt14 );15//---------------------<信号定义>---------------------------------------16wire add_cnt ;17wire end_cnt ;1819//----------------------------------------------------------------------20//-- 0-9计数21//----------------------------------------------------------------------22always @(posedge clk or negedge rst_n)begin23if(!rst_n)24 cnt <= 'd0;25else if(add_cnt)begin26if(end_cnt)27 cnt <= 'd0;28else29 cnt <= cnt + 1'b1;30end31else32 cnt <= cnt;33end3435assign add_cnt = 1;36assign end_cnt = add_cnt && cnt==10-1;3738394041endmodule2.RTL视图四、⾃减计数器(较少⽤到)1.代码1//====================================================================== 2// --- 名称 : Count_43// --- 作者 : xianyu_FPGA4// --- ⽇期 : 2018-12-195// --- 描述 : 模10⾃减计数器,10到0循环累减6//====================================================================== 78module Count_49//---------------------<端⼝声明>---------------------------------------10 (11input clk ,12input rst_n ,13output reg [ 3:0] cnt14 );15//---------------------<参数定义>---------------------------------------16parameter CNT_MAX = 10 ;1718//----------------------------------------------------------------------19//-- 10到0循环累减20//----------------------------------------------------------------------21always @(posedge clk or negedge rst_n)begin22if(!rst_n) begin23 cnt <= 0;24end25else if(cnt==0) begin26 cnt <= CNT_MAX;27end28else begin29 cnt <= cnt - 1;30end31end323334endmodule2.RTL视图3.仿真波形五、新学到的⼀种⾮常简洁的计数器 本以为计数器就是这样了,近来学习开源骚客《SDRAM那些事⼉》系列教程,⼜发现⼀种新的写法,对于特定功能的实现上⾮常简洁。

verilog综合设计实验:计数器及译码器的总体设计源代码

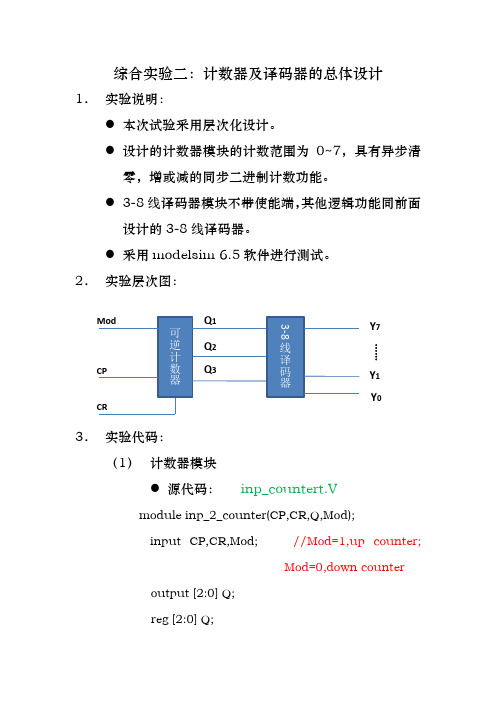

综合实验二:计数器及译码器的总体设计1. 实验说明:● 本次试验采用层次化设计。

● 设计的计数器模块的计数范围为0~7,具有异步清零,增或减的同步二进制计数功能。

● 3-8线译码器模块不带使能端,其他逻辑功能同前面设计的3-8线译码器。

● 采用modelsim 6.5软件进行测试。

2. 实验层次图:3. 实验代码:(1) 计数器模块● 源代码:inp_countert.Vmodule inp_2_counter(CP,CR,Q,Mod);inputCP,CR,Mod; //Mod=1,up counter;Mod=0,down counteroutput [2:0] Q;reg [2:0] Q; Y 7 Y 1 Y 0……always @ (posedge CP or negedge CR)if(~CR)Q<=3'b000;//CR=0,asynchronousclear else if (Mod==1) Q<=Q+1'b1;else Q<=Q-1'b1;endmodule●测试代码:test_inp_counter.Vmodule test_inp_2_counter;regCP,CR,Mod;wire [2:0] Q;inp_2_counter u0(CP,CR,Q,Mod);initialbeginCP=0;CR=0;Mod=1;#20 CR=1;Mod=1;#60 CR=0;Mod=1;#20 CR=1;Mod=1;#40 CR=1;Mod=0;#20 CR=0;Mod=1;endalways #10 CP=~CP;endmodule●测试结果:见inp2counter.WLF(2)译码器模块●源代码:3-8-decoder.Vmodule decoder_3to8(Q,Y);input [2:0] Q;output [7:0] Y;reg [7:0] Y;always @(Q)begin case(Q)3'b000:Y=8'b11111110;3'b001:Y=8'b11111101;3'b010:Y=8'b11111011;3'b011:Y=8'b11110111;3'b100:Y=8'b11101111;3'b101:Y=8'b11011111;3'b110:Y=8'b10111111;3'b111:Y=8'b01111111;endcaseendendmodule●测试代码:test_3_8_decoder.Vmodule test_decoder_3to8;reg [2:0] Q;wire [7:0] Y;decoder_3to8 u1(Q,Y);initialbeginQ=3'b000;endalways #20 Q=Q+1'b1;endmodule●测试结果:见decoder-3-8.WLF(3)顶层模块●源代码:top.Vmoduledec_counter(CP,CR,Mod,Y);inputCP,CR,Mod;output [7:0] Y;wire [2:0] Q; //intermediate carriesinp_2_counter f1(CP,CR,Q,Mod);decoder_3to8 f2(Q,Y);endmodule●测试代码:test_top.Vmoduledec_counter(CP,CR,Mod,Y);inputCP,CR,Mod;output [7:0] Y;wire [2:0] Q; //intermediate carriesinp_2_counter f1(CP,CR,Q,Mod);decoder_3to8 f2(Q,Y);endmodule测试结果:见top_dec_cn.WLF4.实验心得:本次实验为第一次使用分层次的电路设计方法来完成所需功能。

verilog中进制转换原理

Verilog中进制转换原理1.概述进制转换在计算机科学中起着重要的作用,特别是在硬件描述语言中。

V e ri lo g作为一种常用的硬件描述语言,也具备了进制转换的功能。

本文将介绍Ve ri lo g中的进制转换原理,包括二进制、八进制、十进制和十六进制之间的转换方法及其应用。

2.二进制转换二进制是计算机中最基本的进制形式,只包含两个数字0和1。

在V e ri lo g中,二进制数可以通过使用前缀`'b`来表示。

例如,`4'b1010`表示二进制数1010。

要将其他进制数转换为二进制数,可以使用一些内置函数和操作符。

例如,使用`$di sp la y`函数可以将其他进制数转换为二进制数并在仿真时显示出来。

3.八进制转换八进制是基于8个数字的进制形式,从0到7。

在Ve ri lo g中,八进制数可以通过使用前缀`'o`来表示。

例如,`12'o17`表示八进制数17。

要将其他进制数转换为八进制数,可以使用内置函数和操作符,例如`$di sp la y`函数。

4.十进制转换十进制是最常用的进制形式,包含0到9十个数字。

在V eri l og中,十进制数可以直接用数字表示,例如,`1234`表示十进制数1234。

要将其他进制数转换为十进制数,同样可以使用内置函数和操作符。

在仿真时,可以使用`$di sp la y`函数将其他进制数转换为十进制并显示出来。

5.十六进制转换十六进制是基于16个数字的进制形式,从0到9和A到F。

在V e ri lo g中,十六进制数可以通过使用前缀`'h`来表示。

例如,`8'h1A`表示十六进制数1A。

同样,可以使用内置函数和操作符将其他进制数转换为十六进制数,并使用`$di sp l ay`函数在仿真时显示出来。

6.进制转换的应用场景进制转换在硬件描述语言中有广泛的应用场景。

例如,在设计电路时,需要将数值表示为二进制数,并进行位操作。

verilog计数器设计原理

Verilog计数器设计原理1. 介绍计数器是一种常见的数字电路,用于计算和记录事件的数量。

在数字系统中,计数器通常用于生成时钟信号、控制状态机、实现频率分频等应用。

Verilog是一种硬件描述语言,可以用于设计和仿真数字电路。

本文将详细介绍与Verilog计数器设计相关的基本原理。

2. 计数器的基本概念计数器是一种能够在输入脉冲信号的作用下进行累加或递减操作的数字电路。

它通常由触发器和逻辑门组成,触发器用于存储和传递数据,逻辑门用于控制触发器的工作状态。

2.1 同步计数器同步计数器是通过时钟信号来同步各个触发器的状态转换,以实现数据的累加或递减操作。

它包含一个时钟输入端(CLK)和一个复位输入端(RST)。

2.1.1 同步正向计数器同步正向计数器是最简单的同步计数器之一,它能够在每个上升沿时钟信号到达时进行累加操作。

2.1.1.1 原理同步正向计数器由多个触发器和逻辑门组成,其中每个触发器都有一个时钟输入端和一个复位输入端。

当时钟信号的上升沿到达时,触发器的状态将根据输入信号进行更新。

具体的原理如下:1.初始化:将计数器的初始值设置为0。

2.时钟边沿检测:当时钟信号的上升沿到达时,进入下一步操作。

3.累加操作:根据触发器的当前状态进行累加操作。

如果触发器为0,则变为1;如果触发器为1,则变为0。

4.检测溢出:如果最高位触发器由1变为0,则表示计数溢出,需要将其他低位触发器进行进位操作。

2.1.1.2 Verilog代码示例以下是一个4位同步正向计数器的Verilog代码示例:module synchronous_counter(input wire clk,input wire rst,output wire [3:0] count);reg [3:0] count;always @(posedge clk or posedge rst)beginif (rst)count <= 4'b0000;elsecount <= count + 1;endendmodule2.1.2 同步递减计数器同步递减计数器是同步正向计数器的一种扩展,它能够在每个上升沿时钟信号到达时进行递减操作。

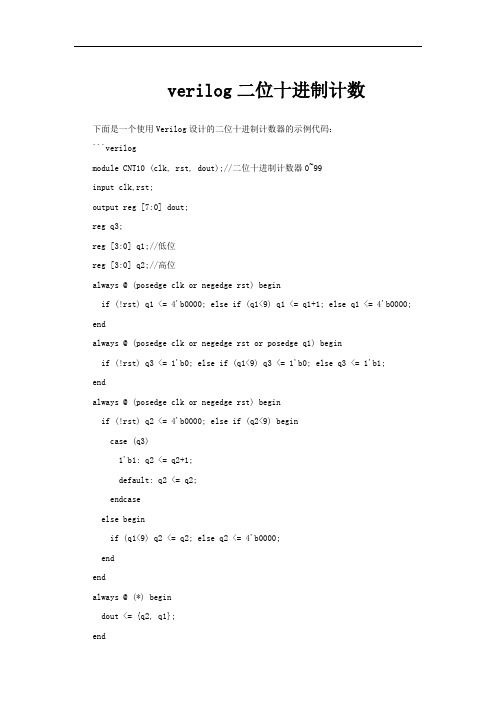

verilog二位十进制计数

verilog二位十进制计数下面是一个使用Verilog设计的二位十进制计数器的示例代码:```verilogmodule CNT10 (clk, rst, dout);//二位十进制计数器0~99input clk,rst;output reg [7:0] dout;reg q3;reg [3:0] q1;//低位reg [3:0] q2;//高位always @ (posedge clk or negedge rst) beginif (!rst) q1 <= 4'b0000; else if (q1<9) q1 <= q1+1; else q1 <= 4'b0000; endalways @ (posedge clk or negedge rst or posedge q1) beginif (!rst) q3 <= 1'b0; else if (q1<9) q3 <= 1'b0; else q3 <= 1'b1;endalways @ (posedge clk or negedge rst) beginif (!rst) q2 <= 4'b0000; else if (q2<9) begincase (q3)1'b1: q2 <= q2+1;default: q2 <= q2;endcaseelse beginif (q1<9) q2 <= q2; else q2 <= 4'b0000;endendalways @ (*) begindout <= {q2, q1};end```这个计数器可以对输入的时钟信号进行计数,并在输出端输出二位十进制的计数值。

它使用了三个寄存器来存储计数值的高位、低位和进位信号,并通过逻辑判断和计数器的级联实现了二位十进制的计数功能。