全差分运放电路的设计

一种新型的0.5V全差分运放的设计

只能 用于 有单 阱 的工 艺 中 , S管跨 导较 小 , 效输 入 MO 等

噪声 较大 , 此外 , 子特性 与工 艺也 有很 大 的关 系 。 管 近年来 , 携式设 备 的迅速 普及 和小 尺寸 器件 的需 便 求增 长对 运放 的低压 低功 耗要求 也 越来 越高 , 在很 多应 用场合 , 如助 听器 等移 动 设 备 中 , 例 电源 电压 最 好 能 够

b s d o SM I 0. 8 “ sa d M a e n C 1 m tn a CM OS p o e s The sm uat n rs lsu ig H Spe h w ha heo e o p gan o hes r c u e rcs. i l i e u t sn o ie s o t tt p n l o i f t tu t r c n a he e 7 B ,nd u t a c iv 6 d a niy—gan b n i a dwit a c e e 1 0 M H z d h c n a hiv 5 . Ke ywo ds:ow —v t ge; e a i a m p iir;uly dif r n i ; om m o ~m od e d c r l ola op r ton la lfe f l fe e talc n e f e ba k

01 m 标准 C . 8“ MOS工 艺 , pc 仿 真 结 果表 明 , 种 结 构 的 开 环 增 益 可 以达 到 7 B, 位 增 益 带 宽 1 0MHz HS i e 这 6d 单 5 。

关键词 : 压 ; 低 运放 ; 差 分 ; 模 反 馈 全 共

中 图 分 类 号 : N4 2 T 0

B e ja W ANG i H H UA ig AIW n u n。 Z , O Jn

一款高增益、低功耗、宽带宽全差分运放设计

一款高增益、低功耗、宽带宽全差分运放设计周吉;龚敏;高博【摘要】基于SMIC 0.18 μm工艺模型设计了一种低电压1.8 V下的高增益、低功耗、宽输出摆幅、宽带宽的运算放大器电路.采用增益自举技术的折叠共源共栅结构极大地提高了增益,并采用辅助运放电流缩减技术有效地降低了功耗,且具有开关电容共模反馈(SC-CMFB)电路.在Cadence spectre平台上仿真得到运放具有极高的开环直流增益(111.2 dB)和1.8V的宽输出摆幅,单位增益带宽576 MHz,相位裕度为58.4°,功耗仅为0.792 mW,在1 pF的负载时仿真得到0.1%精度的建立时间为4.597 ns,0.01%精度的建立时间为4.911 ns.【期刊名称】《电子与封装》【年(卷),期】2016(016)005【总页数】5页(P26-30)【关键词】低功耗;运算放大器;高增益;宽带宽;折叠共源共栅【作者】周吉;龚敏;高博【作者单位】四川省微电子技术重点实验室,四川大学物理学院,成都610064;四川省微电子技术重点实验室,四川大学物理学院,成都610064;四川省微电子技术重点实验室,四川大学物理学院,成都610064【正文语种】中文【中图分类】TN402运算放大器(简称运放)是许多模拟系统和混合信号系统中一个完整且关键的部分,随着无线通讯技术和CMOS集成电路制造工艺技术的迅猛发展,电源电压越来越低,功耗要求越来越小,但数模混合信号系统对分辨率和速度的要求却越来越高,因此高性能的运放设计成为了必要[1]。

根据模拟电路设计的“八边形法则[1]”,运放的关键性能参数如增益、速度、功耗、输出摆幅等参数相互制约,这对高性能放大器的设计提出了许多难题。

因此,设计同时具有高增益、宽带宽、宽输出摆幅并且低功耗的放大器便成为了本设计的难点[1,2,3]。

高速、高精度的应用需要运放具有很高的增益和带宽,而这必然会增加运放的功耗,Mersi A.等发表的文献中采用两级带补偿结构的运放功耗仅为0.86 mW[4],而这种结构对进一步提高运放带宽等有一定的局限性,本文采用了一种不同的低功耗运放结构,希望解决这个问题。

采用折叠式结构的两级全差分运算放大器的设计

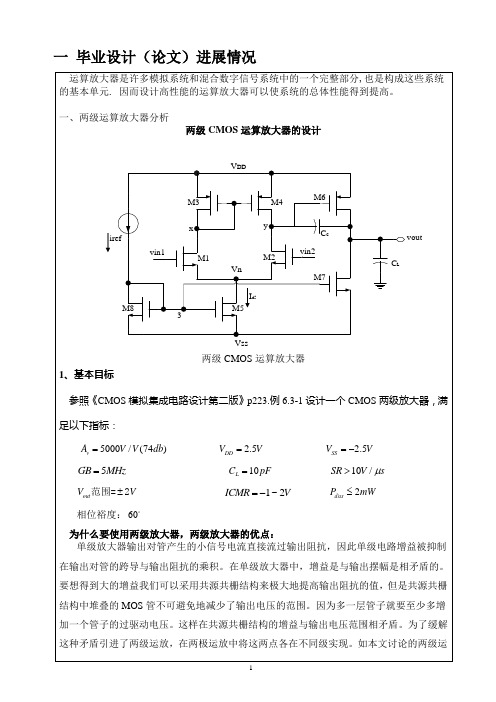

目录1. 设计指标 (1)2. 运算放大器主体结构的选择 (1)3. 共模反馈电路(CMFB)的选择 (1)4. 运算放大器设计策略 (2)5. 手工设计过程 (2)5.1 运算放大器参数的确定 (2)5.1.1 补偿电容Cc和调零电阻的确定 (2)5.1.2 确定输入级尾电流I0的大小和M0的宽长比 (3)5.1.3 确定M1和M2的宽长比 (3)5.1.4确定M5、M6的宽长比 (3)5.1.5 确定M7、M8、M9和M10宽长比 (3)5.1.6 确定M3和M4宽长比 (3)5.1.7 确定M11、M12、M13和M14的宽长比 (4)5.1.8 确定偏置电压 (4)5.2 CMFB参数的确定 (4)6. HSPICE仿真 (5)6.1 直流参数仿真 (5)6.1.1共模输入电压范围(ICMR) (5)6.1.2 输出电压范围测试 (6)6.2 交流参数仿真 (6)6.2.1 开环增益、增益带宽积、相位裕度、增益裕度的仿真 (6)6.2.2 共模抑制比(CMRR)的仿真 (7)6.2.3电源抑制比(PSRR)的仿真 (8)6.2.4输出阻抗仿真 (9)6.3瞬态参数仿真 (10)6.3.1 转换速率(SR) (10)6.3.2 输入正弦信号的仿真 (11)7. 设计总结 (11)附录(整体电路的网表文件) (12)采用折叠式结构的两级全差分运算放大器的设计1. 设计指标5000/ 2.5 2.551010/21~22v DD SS L out dias A V VV V V VGB MHz C pF SR V s V V ICMR V P mWµ>==−==>=±=−≤的范围2. 运算放大器主体结构的选择图1 折叠式共源共栅两级运算放大器运算放大器有很多种结构,按照不同的标准有不同的分类。

从电路结构来看, 有套筒式共源共栅、折叠式共源共栅、增益提高式和一般的两级运算放大器等。

全差分运算放大器设计

全差分运算放大器设计全差分运放(Fully-Differential Amplifier,简称FDA)是一种特殊的运放,它具有两个差动输入和两个差动输出。

全差分运放具有许多优点,包括良好的共模抑制和电源抑制比,适用于高精度传感器信号放大、功率放大和模拟信号处理等领域。

在这篇文章中,我将介绍全差分运放的设计原理和步骤。

首先,我们需要确定设计的要求和规范。

这包括增益要求、带宽要求、电源电压和输入输出电阻等参数。

根据这些要求,我们可以选择合适的运放器件和电路拓扑。

全差分运放的常见电路拓扑有两级差分放大器、共射共源放大器和增益交换放大器等。

在这里,我们以两级差分放大器为例进行设计。

第一步是选择运放器件。

我们需要根据设计要求选择适合的运放器件,可以根据其增益带宽积、供电电压范围和失调电流等参数进行选择。

一般来说,我们可以选择低失调电流、高增益带宽积和低电压噪声的器件。

第二步是确定电路拓扑。

在两级差分放大器中,第一级是差分放大器,第二级是共射共源放大器。

差分放大器的作用是提供高输入阻抗和共模抑制比,共射共源放大器的作用是提供电流放大和驱动能力。

由于这两级放大器要分别满足不同的要求,我们可以选择不同的放大倍数和器件参数来优化电路性能。

第三步是确定偏置电路。

偏置电路的作用是提供恒定的工作电流,这可以通过电流源和电阻网络来实现。

偏置电流的选择要根据运放器件的要求和特点,可以使用恒流源或电流反馈等方法来实现。

第四步是确定反馈电路。

反馈电路的作用是控制放大倍数和增益稳定性,可以使用电阻、电容或者电流源等元件来实现。

选择适当的反馈方式可以减小失调电压和非线性,提高性能。

第五步是进行电路仿真和优化。

通过电路仿真,我们可以验证设计的性能和满足要求。

优化可以通过调整电路参数和进行迭代仿真来实现,以达到设计要求。

第六步是进行电路布局和线路板设计。

在设计布局时,要注意分离放大器电路和干扰源,减少电源和信号线的串扰。

线路板设计要保证差分信号走线的对称性和阻抗匹配,以提高传输性能。

全差分套筒式共源共栅放大器及其共模反馈电路

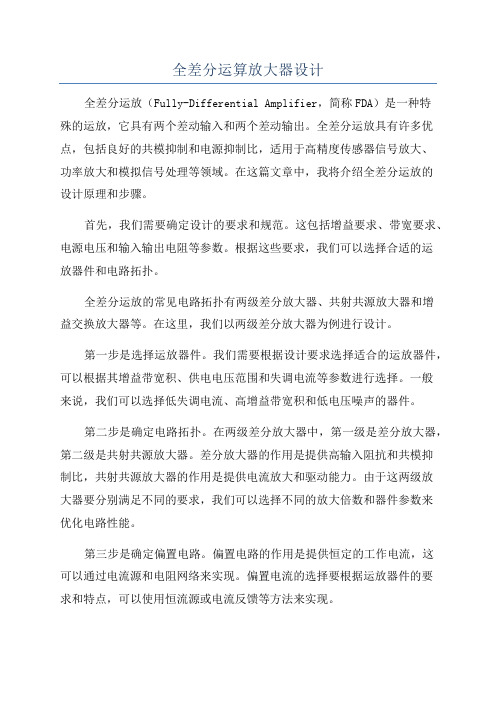

一毕业设计(论文)进展情况60为什么要使用两级放大器,两级放大器的优点:单级放大器输出对管产生的小信号电流直接流过输出阻抗,因此单级电路增益被抑制在输出对管的跨导与输出阻抗的乘积。

在单级放大器中,增益是与输出摆幅是相矛盾的。

GB GB GB ()()()p p z的相位裕量,所以2.2 10LC因此由补偿电容最小值即可以得到2m112'1g (/)(/)2/12N W L W L K I ==≅ 用负ICMR 公式计算5Dsat V 由式(12)我们可以得到下式15(min)IC SS GS Dsat V V V V =++如果5DS V 的值小于100mv ,可能要求相当大的5(/)W L ,如果5Dsat V 小于0,则ICMR 的设计要求则可能太过苛刻,因此,我们可以减小5I 或者增大5(/)W L 来解决这个问题,我们为了留一定的余度我们(min)IC V 等于-1.1V 为下限值进行计算152511(min)Dsat IC TN SS I V V V V β=---()则可以得到的5Dsat V 进而推出555'2552(/)()Dsat S W L K V ==(I )11/1≅即有58(/)(/)11/1W L W L =≅为了得到60°的相位裕量,6m g 的值近似起码是输入级跨导1m g 的10倍(allen 书p.211例6.2-1),我们设us g g m m 9421016==,为了达到第一级电流镜负载(M3和M4)的正确镜像,要求46SG SG V V =,图中x ,y 点电位相同我们可以得到6644(/)(/)64/1m m gW L W L g ==进而由6662(/)m Pd g K W L I '=我们可以得到直流电流 22m6m667''6666g g 113.72(/)2d d I I A K W L K S μ==== 同样由电流镜原理,我们可以得到7755(/)(/)32/1d d IW L W L I ==3、仿真和测量 (1)DC 分析图2 VOUT 、M5管电流、M7管电流、Vx 与Vy 与输入共模电压变化的关系图4 测量共模输入范围的电路图图5 运放的输入共模电压范围从图中可以得到输入共模范围满足设计指标(-1V~2V)(3)测量输出电压范围在单位增益结构中,传输曲线的线性收到ICMR 限制。

模拟集成电路设计——两级全差分高增益放大器设计_2

全差分高增益放大器的设计一、设计产品名称全差分高增益放大器二、设计目的1.掌握模拟集成电路的基本设计流程;2.掌握Cadence基本使用方法;3.学习模拟集成电路版图的设计要点;4.培养分析、解决问题的综合能力;5.掌握模拟集成电路的仿真方法;6.熟悉设计验证流程方法。

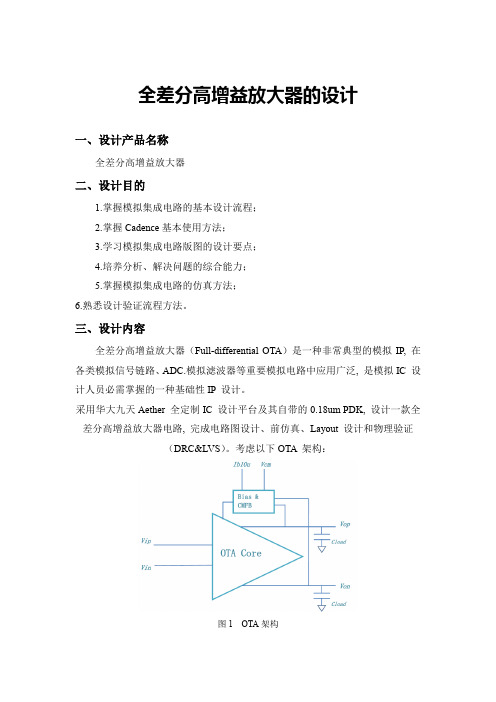

三、设计内容全差分高增益放大器(Full-differential OTA)是一种非常典型的模拟IP, 在各类模拟信号链路、ADC.模拟滤波器等重要模拟电路中应用广泛, 是模拟IC 设计人员必需掌握的一种基础性IP 设计。

采用华大九天Aether 全定制IC 设计平台及其自带的0.18um PDK, 设计一款全差分高增益放大器电路, 完成电路图设计、前仿真、Layout 设计和物理验证(DRC&LVS)。

考虑以下OTA 架构:图1 OTA架构四、电路设计思路模拟集成电路的设计分为前端与后端, 设计流程可以分为明确性能要求、选择电路结构、计算器件参数、原理图绘制、前仿真、版图绘制、DRC设计规则检查、LVS版图与电路图一致性检查、寄生参数提取及后仿真、流片测试。

本次实验使用基于华大九天Aether 全定制IC 设计平台及其自带的0.18um PDK, 实现模拟集成电路全差分高增益放大器的全流程设计与仿真。

(1)性能指标:需要验证三种PVT Corner:a) 电源电压1.8V, 温度27℃, corner 为TT;b) 电源电压1.6V, 温度80℃, corner 为SS;c) 电源电压2.0V, 温度-40℃, corner 为FF;要求各Corner 下开环技术指标(含Cload=10fF):①放大器开环DC 增益Av0≥90dB;②0dB 带宽BW0≥500MHz;③相位裕度Phase Margin≥50°。

④DC 抑制比PSRR-0≥60dB, (3*2=6 分)⑤10MHz 时抑制比PSRR-10M≥45dB。

全差分两级放大电路

综合课程设计研究报告课题名称:全差分两级运放研究人员:指导教师:王向展宁宁201 年1月1日微电子与固体电子学院目录一、绪论 (1)(一)研究工作的背景与意义 (1)(二)国内外现状分析 (1)二、研究目标、研究内容与技术指标 (1)(一)研究目标 (2)(二)研究内容 (2)(三)关键技术 (2)(四)技术指标 (3)三、电路工作原理 (3)(一)电路结构理论 (4)(二)关键电路模块 (4)(三)非理想效应 (5)四、电路设计与仿真 (6)(一)电路设计方案 (6)(二)电路设计结构 (9)(三)电路仿真及结果 (10)五、全文总结与展望 (12)参考文献 (13)一、绪论(一)研究工作的背景与意义随着模拟集成电路技术的发展,高速、高精度运算放大器得到广泛应用。

全差分运算放大器在输入动态范围、抑制共模信号和噪声的能力等方面,较单端输出运放有很大优势,成为应用很广的电路单元。

另外,全差分输出时的输出电压信号幅度比单端输出时增大一倍,这对低电源电压供电的现代CMOS电路尤为重要,因为这可以扩大输出信号的动态范围。

因此,本文讨论并设计了满足一定要求的全差分运算放大器。

(二)国内外现状分析从第一颗运算放大器IC问世到现在,运算放大器技术已经在半导体制造工艺和电路设计两方面取得了巨大进展。

在大约40年的发展过程中,IC制造商们利用上述先进技术设计出了近乎“完美”的放大器。

虽然什么是理想放大器很难有一个精确定义,但它却为模拟设计工程师提供了一个目标。

理想放大器应该无噪声、具有无穷大增益、无穷大输入阻抗、零偏置电流以及零失调电压,它还应该不受封装尺寸限制,不占用空间。

上述这些,都是许多教科书为了得到简单的传递函数而做出的种种假设。

未来放大器市场增长的驱动力主要有三方面:其一,便携式应用的低功耗要求将推动具有低操作电源电压/电流的放大器增长;其二,高分辨率应用需要能降低噪声和失真度的放大器;其三,由于性能和价格压力持续上扬,因此能够集成其他功能的放大器前景乐观。

全差分运算放大器设计

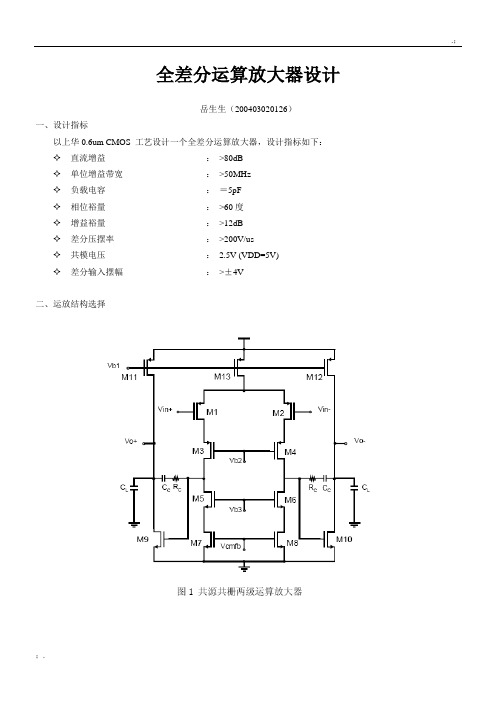

全差分运算放大器设计岳生生(200403020126)一、设计指标以上华0.6um CMOS 工艺设计一个全差分运算放大器,设计指标如下:✧直流增益:>80dB✧单位增益带宽:>50MHz✧负载电容:=5pF✧相位裕量:>60度✧增益裕量:>12dB✧差分压摆率:>200V/us✧共模电压:2.5V (VDD=5V)✧差分输入摆幅:>±4V二、运放结构选择运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。

如图2所示;(b )折叠共源共栅,folded-cascode 。

如图3所示;(c )共源共栅,telescopic 。

如图1的前级所示。

本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的,DSAT NV之和小于0.5V ,输出端的所有PMOS管的,DSAT PV之和也必须小于0.5V 。

对于单级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该要求,因此我们采用两级运算放大器结构。

另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。

考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。

两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。

三、性能指标分析1、 差分直流增益 (Adm>80db)该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12) 第一级增益1351113571135135753()m m m o o o o o m m m m o o o o m m g g gg gg G A R r rr r g g r r r r=-=-=-+第二级增益92291129911()m o o o m m o o gg G AR r rgg=-=-=-+整个运算放大器的增益:4135912135753911(80)10m m m m overallo o o o m m o o dB g g g gAA A g g g gr r r r ==≥++2、 差分压摆率 (>200V/us )转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

全差分运放电路的设计

全差分运放电路是一种常用的放大电路,它可以在信号采集和信号处

理中起到很大的作用。

全差分运放电路通过将信号输入分为两个互为相反

的信号,从而抵消共模干扰,提高系统的抗干扰能力,实现高质量的信号

放大。

本文将会详细介绍全差分运放电路的设计方法和注意事项。

首先,全差分运放电路由运放、电阻和电容器组成。

一般情况下,有

两种常见的全差分运放器设计:非反馈输出型和反馈输出型。

对于非反馈输出型的全差分运放电路,其输出电压与输入电压成正比。

这种设计方式适用于需要稳定增益的应用,如压力传感器、光传感器等。

而反馈输出型的全差分运放器则通过反馈网络来调整增益,适用于需要可

调增益的应用,如音频放大器、滤波器等。

在设计全差分运放电路时,需要考虑以下几个关键因素:

1.输入电阻和输入电容:全差分运放电路的输入电阻应尽可能大,以

减小输入电流,避免对信号源的干扰。

同时,输入电容也应尽可能小,以

提高信号的快速响应。

2.带宽:全差分运放电路的带宽需要根据实际应用需求进行选择。

一

般情况下,带宽越大,电路越容易产生共模干扰。

因此,需要根据具体应

用需求来平衡带宽和抗干扰能力。

3.输出电阻:全差分运放电路的输出电阻应尽可能小,以实现较高的

加载能力和输出电压稳定性。

4.功耗:全差分运放电路的功耗应尽可能小,以提高系统的能效和延

长电池寿命。

设计全差分运放电路时,可以按照以下步骤进行:

1.确定应用需求:首先需要明确电路的功能和应用场景,包括所需的

增益、带宽和动态范围等。

2.选择运放器:根据应用需求选择合适的全差分运放器,考虑增益范围、带宽、功耗和价格等因素。

3.选择电阻和电容器:根据所选的运放器的输入和输出特性,选择合

适的电阻和电容器,以满足输入和输出阻抗的要求。

4.建立电路模型:根据电路需求和所选元件的特性,建立电路模型进

行电路仿真,并进行参数优化。

5.PCB设计:根据电路模型进行PCB设计,注意信号、电源和地的布

线问题,尽量减少共模干扰。

6.系统验证:完成PCB制造和装配后,对全差分运放电路进行系统验证,检验其性能是否满足设计要求。

需要注意的是,全差分运放电路的设计涉及到电路原理、电路仿真、PCB设计和系统验证等多个方面,需要综合考虑各个因素,并根据具体应

用情况进行调整。

此外,还要注意对输入信号进行滤波和保护,以提高系

统的可靠性和抗干扰能力。

总结起来,设计全差分运放电路需要根据应用需求选择合适的运放器,确定电阻和电容器,并进行电路模型建立和优化,最后进行PCB设计和系

统验证。

通过合理的设计和优化,可以实现高性能的全差分运放电路,提

高系统的可靠性和抗干扰能力。