PCI接口时序测试方法

PCI总线功能概要

PCI总线的功能2.1 连接到PCI总线上的设备连接到PCI总线上的设备分为两类:(1)主控设备(master):PCI支持多主控设备,主控设备可以控制总线、驱动地址、数据及控制信号;(2)目标设备(target):不能启动总线操作,只能依赖于主控设备向他进行传递或从中读取数据。

2.2 有关PCI引脚信号有关PCI引脚信号说明如下:AD[31~0]:地址、数据信号复用线。

PCI总线支持写猝发和读猝发。

一个总线传输分为一个地址传送阶段和一个或多个数据传送阶段。

有效,表示地址传送阶段开始,此时AD[31~0]包含一个32位的物理地址,选中I/O的一个字节单元或主存的一个双字单元。

接下来为数据传送阶段(IRTY和TRDY同时有效),此时AD[7~0]包含最低字节数据,AD[31~24]包含最高字节数据。

C/BE[3~0]:总线指令和字节允许信号的复用线。

在地址传送阶段,C/BE[3~0]上传送的是4位编码的总线指令。

在数据传送阶段,C/BE[3~0]用作字节允许标志,以决定数据线上的哪些字节数据为有效数据,C/BE[3~0]可依次对应于字节3,2,1,0。

FRAME:周期帧信号。

由当前总线控制者产生,表示一个总线传输的开始和延续。

FRAME从无效变为有效.表明总线传输开始;保持有效,表明总线传输继续进行(1个或n个数据节拍正在继续);FRAME从有效变为无效,表明进入数据传输的最后一个数据传送阶段。

2.3 总线指令定义在地址传送阶段,C/BE[3~0]线上送出总线指令的编码信息。

总线指令用于对目标设备说明当前总线控制者正在进行的总线传输类型。

表1给出了总线指令的定义。

I/O读:用于从一个被选中的I/O单元中读取数据。

I/O写:用于写数据到一个被选中的I/O单元中。

3 测量PCI总线的I/O写时序波形的技术及分析方法测量PCI总线的I/O写时序波形共分3个部分,如图1所示。

具体的实现测量的过程及分析方法介绍如下3.1 编写测试程序用汇编语言编写测试程序,该程序如下:3.2 制作测试板PCI波形采用厦门厦华三宝计算机有限公司状元一族主板,执行标准号:Q/FSl0938-1999。

[实践]PCI时序图

![[实践]PCI时序图](https://img.taocdn.com/s3/m/465b456f30b765ce0508763231126edb6f1a7631.png)

1)PCI LOCAL BUS SPEC V2.2主讲人:关永聪2)内容简介3)Chapter 1 introduction1.1PCI总线概述.PCI全称peripheral component interconnect special interest group,简称PCISIG.标准的PCI系统架构4)1.2 PCI 总线的特性及优点1.高性能:33M时钟,32位数据总线,数据传输率可达132M/S.2.线性突发传输.PCI总线支持线性突发传输,可确保总线不断满载数据.3.极少的存取延迟,可大副减低外设取得总线控制权的时间.4.采用总线主控和同步操作.5.不受处理器的限制.6.适合各种机型.7.预留了发展空间.5)Chapter 2 signal definition对于只作为目标的设备,PCI需要至少47条信号线;若只作为主设备,则需49条信号线.6)2.1信号类型定义IN:输入,是一标准的只作输入的信号.OUT:输出,是一标准的输出驱动信号.T/S:表示一双向的三态输入输出信号.S/T/S:表示一持续的低电平有效的三态信号.O/D:表示漏极开路,允许多个设备以线或的型式共同驱动和分享.S/T/S:表示一持续的低电平有效的三态信号.O/D:表示漏极开路,允许多个设备以线或的型式共同驱动和分享.7)2.2 信号引脚定义2.2.1系统引脚CLOCK(IN):PCI的信号,除RST,INTA#,INTB#,INTC#,INTD#外,都在CLOCK的上升沿有效或采样.RESET#(IN):用来使PCI专用的特性寄存器和序列发生器相关的信号恢复规定的初始状态.2.2.2地址与数据引脚AD[31::00](T/S):是地址数据多路复用的输入输出信号.在FRAME#有效时,为地址期;在IRDY#.TRDY#同时有效时是数据期.C/BE[3::0](T/S):总线命令与字节使能.PAR[T/S]:奇偶校验.2.2.3接口控制引脚.FRAME#(S/T/S):帧开始信号.IRDY#(S/T/S):主设备准备好.TRDY#(S/T/S):从设备准备好.STOP#(S/T/S):停止传送数据.LOCK#(S/T/S):锁定信号.8)IDSEL(IN):初始化设备选择信号.DEVSEL#(S/T/S):设备选择信号.2.2.4仲裁引脚.REQ#(T/S):总线占用请求.GNT#(T/S):总线占用允许.2.2.5错误报告引脚.PERR#(S/T/S):奇偶校验错误报告.SERR#(O/D):系统错误报告.2.2.5中断引脚.INTA# INTB# INTC# INTD#(O/D):请求一个中断,后三个只能用于多功能设备.2.2.6其它可选信号引脚.9)PRSNT[1::2]#(IN):PCI SLOT 中是否有卡.CLOCKUN#(IN,O/D,S/T/S):只用在PCI MOBILE 中,在CONNECTOR中没定义.M66EN(IN):PCI总线频率为66M.PME#(O/D):电源管理事件.3.3V aux(IN):3.3V辅助电源输入.2.2.7 64位扩展引脚(可选).A/D[63::32](T/S)C/BE[7::4](T/S)REQ64#(S/T/S):64位传送请求.ACK64#(S/T/S):64位传送应答.10)PAR64(T/S):高32位奇偶校验.JTAG/Boundary Scan Pins (可选)TCLK(IN):在检查存取操作时检查时钟.TDI(IN):在检查存取操作时检查输入.TDO(OUT):在检查存取操作时检查输出.TMS(IN):在检查存取操作时控制控制器的状态.TRST#(IN):在检查存取操作时初始化控制器.2.2.9 System Management Bus接口引脚.(可选)SMBCLK(O/D):System Management Bus时钟.SMBDAT(O/D):System Management Bus数据.11)Chapter 3 bus operation3.1总线命令.3.1.1总线命令定义.C/BE[3::0]#Command Type0000 中断应答0001 特殊周期0010 I/O读0011 I/O写0100 保留0101 保留0110 存储器读0111 存储器写1000 保留1001 保留12)C/BE[3::0]#Command Type1010配置读1011配置写1100存储器多行读1101双地址周期1110存储器行读1111存储器写并无效13)3.2 PCI总线协议3.2 PCI总线协议.3.2.1 PCI总线的传输控制.三个重要的传输控制信号:FRAME#:由主设备驱动,指明一个数据传输的开始和结束.IRDY#:由主设备驱动,允许插入等待时间.TRDY#:又从设备驱动,允许插入等待时间.PCI总线的传输一般应遵循下面的管理规则:一.FRAME#和IRDY#定义了总线的忙/闲状态,当其中之一有效时,总线忙, 两个都无效时,总线闲.二.一旦FRAME#被置无效,在同一传输周期里不能再设置.三.除非设置了IRDY#,一般情况下不能置FRAME#无效.四.一旦主设备设置了IRDY#,直到当前数据传送结束之前,主设备不能置FRAME#和IRDY#无效.14) 3.2 PCI的编址PCI定义了三个地址空间,内存地址空间,I/O地址空间,配置地址空间.3.2.1内存地址空间:在存储器访问中,所有目标设备都要访问A/D[1::0],A/D[1::0]有下面的定义:00突发传输顺序为线性增长方式10 为CACHE行切换方式X0 保留3.2.2 I/O地址空间:在具体访问中,每当一个从设备被地址译码选中后,便要检查C/BE[3::0]#是否与A/D[1::0]相符,如果两者矛盾,则从设备不传送任何数据,而是以一个“目标终止”操作来结束访问.A/D[1::0]与C/BE[3::0]#的对应关系如下表:15)16)3.2.3配置地址空间在配置的地址空间中,要用A/D[7::0]将访问落实到一个DWORD地址.当一个设备收到配置命令,当IDSEL 有效,且A/D[1::0]=00,则该设备被选为访问的目标.否则,不参与当前的对话.17) 3.3 总在线的数据传输过程一些说明:本节所给的时序图主要表示总线以32位方式执行有关工作时,信号的相应关系.3.3.1总在线的读操作.读操作的基本时序图如下:18) 基本读操作时序图19) 3.3.2基本写操作时序20) 3.3.3传输的终止3.3.3.1由主设备提出的终止.一.数据已传输完.二.超时.21)22)3.3.3.2由从设备提出的终止一.retry.二.disconnect.23)24)25)由从设备发出的终止的特点一.STOP#发出后,就必须维持其有效状态直到FRAME#撤销为止.二.STOP#发出后,FRAME#应尽快撤销,FRAME#撤销后,STOP#也必须在接下来的时钟周期撤销.三.在STOP#有效期间,DEVSEL#也必须有效.四.从设备可以决定是否在STOP#发出后还进行一次数据传输.五.从设备不能在STOP#撤销后再传送数据.六.STOP#发出后的数据传输不能多于一次.七.若主设备要继续完成由从设备终止的传输,它必须在撤销REQ#后两个时钟周期后立刻重新置REQ#有效.26)3.4总线的仲裁仲裁是通过REQ#,GNT#两根信号线来实现的.3.4.1仲裁协议.仲裁的原则:一.若设置了GNT#无效而FRAME#有效时,当前的数据传输是合法的,继续传送下去.二.当总线非空闲时,一个设备的GNT#有效和另一个的GNT#无效之间必须有一个延期时钟,以免在A/D和奇偶校验之间发生时序竞争.三.FRAME#无效时,仲裁器可在任何时刻置REQ#,GNT#无效.若总线占用者在置REQ#,GNT#有效后,在处于空闲状态16个PCI CLOCK后,仍未传送数据,仲裁器可以打破这个状态.27)基本仲裁时序图28)3.4.2仲裁的停靠29) Chap 4 electrical specification30)4.2联接器PCI定义了两种扩展板的联接器,一种是基于5V环境的,一种是基于3.3V环境的.这两种连接器有防呆设计.31)4.3扩展板的技术指标32)Exercises1.PCI信号有哪几种类型,定义如何?2.PCI总线命令的定义.3.PCI总线传输的管理规则.4.基本读操作和基本写操作的时序图有何差异.5.由主设备提出的两种传输终止方式,数据传输完和超时有何区别.6.总线仲裁有何原则.KEY:1.page 6.2. page 11.3.page 13.4. page 18,19.5.page20,21.6.page 26.33)34)ReferencesPCILocalBusSpecification Revision 2.2。

高速总线的时序分析方法及DDR计算实例

高速总线的时序分析方法及DDR计算实例韩玉涛【摘要】随着高速存储器在通信系统和图像处理等领域的普遍使用,如果系统设计中的总线时序问题得不到满足,将会严重影响系统的运行稳定性.在详细介绍了高速总线的数学模型及时序分析方法的基础上,根据时序分析方法给出了SMP8634多媒体处理器与DDR DRAM接口连接的计算实例.【期刊名称】《常州工学院学报》【年(卷),期】2018(031)002【总页数】6页(P42-47)【关键词】DDR;高速总线;建立时间;保持时间;时序分析【作者】韩玉涛【作者单位】瑞为信息技术有限公司,广东深圳518000【正文语种】中文【中图分类】TN41随着处理器处理能力的快速提高,以及通信系统和图像处理等领域对数据高容量存储、大吞吐量传输的要求,DDR、DDR2以及DDR3 DRAM存储器得到了越来越广泛的应用。

这些存储器的工作频率都在100 MHz以上,高的可达1 GHz,这使得系统设计中的总线时序问题变得十分突出。

如果在系统设计中芯片的时序要求得不到满足,轻则会导致系统出现误码,处理能力降低,运行不稳定,严重的甚至会导致系统不能启动。

本文阐述高速数字总线的模型及时序分析方法,并给出SMP8634DDR多媒体处理器与DDR DRAM连接的计算实例。

1 高速总线模型高速总线模型如图1所示,U1和U2是两个在同一时钟CLOCK下工作的芯片,U1输出数据到U2。

图1 高速总线模型当U1输出数据时,U1在时钟上升沿后输出数据,然后输入芯片U2会在下一个时钟的上升沿去锁存数据总线上的数据,从上升沿到数据在数据总线上有效的时间称为时钟到数据的延时tCO。

图2表明了这种总线的时序关系。

图2 总线时序图tCLK:时钟CLOCK的周期。

tCO:芯片U1输出数据时,从时钟上升沿开始到数据出现在数据总线上的时间,此数据需要用到最大值tCOmax及最小值tCOmin。

tSU:芯片数据作为输入时,数据所需的建立时间(时钟上升沿前数据维持的时间),建立时间永远以最小值来计算。

PCIE 3.0简介及信号和协议测试方法

PCIE 3.0简介及信号和协议测试方法安捷伦科技(中国)有限公司:李凯一、前言PCI Express(简称PCIE)总线是PCI总线的串行版本,其采用多对高速串行的差分信号进行高速传输,每对差分线上的信号速率可以是1代的2.5Gbps、2代的5Gbps以及现在正逐渐开始应用的3代8Gbps。

PCIE标准是由PCI-SIG组织制定,自从推出以来,1代和2代标准已经在PC和Server上逐渐普及,用于支持高速显卡以及其它接口卡对于高速数据传输的要求。

出于支持更高总线数据吞吐率的目的,PCI-SIG组织在2010年制定了PCIE 3.0,即PCIE 3代的规范。

目前,PCIE 3.0已经开始出现在一些高端的Server上,而在普通PC上的应用也是指日可待。

那么PCIE 3.0总线究竟有什么特点?对于其测试有什么特殊的地方呢?我们这里就来探讨一下。

二、PCIE 3.0简介1、信号速率的变化首先我们看一下制定PCIE 3代规范的目的,其目的主要是要在现有的FR4板材和接插件的基础上提供比PCIE 2代高一倍的有效数据传输速率,同时保持和原有1代、2代设备的兼容。

别看这是个简单的目的,但实现起来可不容易。

我们知道,PCIE 2代在每对差分线上的数据传输速率是5Gbps,相对于1代提高了1倍;而3代要相对于2代把速率也提高一倍,理所当然的是把数据传输速率提高到10Gbps。

但是就是这个10Gbps把PCI-SIG给难住了,因为PC和Server上出于成本的考虑,普遍使用便宜的FR4的PCB板材以及廉价的接插件,无论采用什么技术都很难保证10Gbps的信号还能在原来的信号路径上可靠地传输很远的距离(典型距离是15~30cm)。

因此PCI-SIG最终决定把PCIE 3代的数据传输速率定在8Gbps。

但是8Gbps比着2代的5Gbps并没有高一倍,所以PCI-SIG决定在3代标准中把在1代和2代中使用的8b/10b编码去掉。

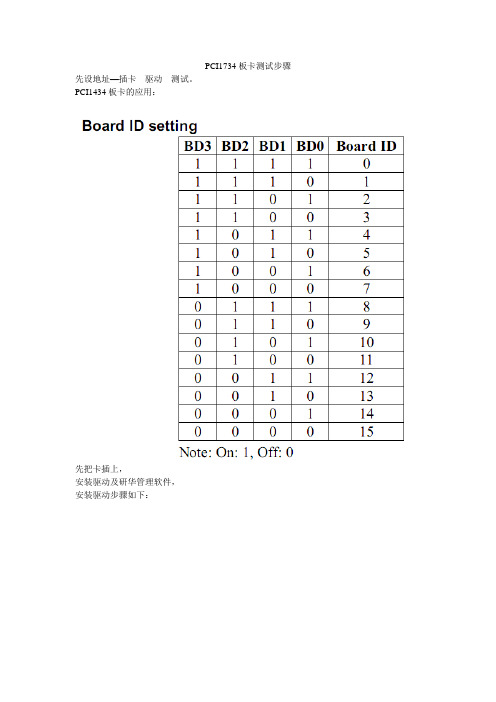

PCI1734卡测试步骤

PCI1734板卡测试步骤先设地址—插卡---驱动---测试。

PCI1434板卡的应用:

先把卡插上,

安装驱动及研华管理软件,

安装驱动步骤如下:

然后选择individual drivers option

完成驱动软件安装

进入设备管理器,查看硬件是否安装成功。

安装成功后打开研华的管理软件

在successed device 目录中查找以安装的设备PCI—1734并按add按钮添加,并在installed devices 中选择该设备然后选择test进入测试界面

1734针脚定义如下:

1734接线定义图如下:

(经测试IDO1与EGND之间的电压为0V,PCOM为24v)

测试接线过程如下:

现场选用一块24直流电源,将电源的负端接入板卡EGND管脚,将电源的正端以并联的方式一端接入板卡的PCOM端,一端接入24v继电器的控制端,将继电器控制端的另一端接到板卡中与PCOM对应的输出端。

通过在软件中控制输出观察继电器是否吸合完成测试过程。

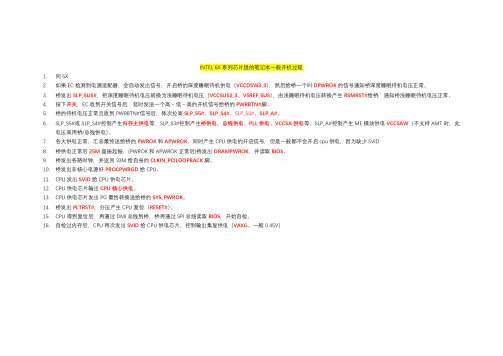

INTEL 6X、5X、4X系列芯片组的时序及查图方法及6、7系列框图

INTEL 6X系列芯片组的笔记本一般开机过程1.同5X2.如果EC检测到电源适配器,会自动发出信号,开启桥的深度睡眠待机供电(VCCDSW3_3),然后给桥一个叫DPWROK的信号通知桥深度睡眠待机电压正常。

3.桥发出SLP_SUS#,把深度睡眠待机电压转换为浅睡眠待机电压(VCCSUS3_3、V5REF_SUS),由浅睡眠待机电压转换产生RSMRST#给桥,通知桥浅睡眠待机电压正常。

4.按下开关,EC收到开关信号后,延时发送一个高-低-高的开机信号给桥的PWRBTN#脚。

5.桥的待机电压正常且收到PWRBTN#信号后,依次拉高SLP_S5#、SLP_S4#、SLP_S3#、SLP_A#。

6.SLP_S5#或SLP_S4#控制产生内存主供电等,SLP_S3#控制产生桥供电、总线供电、PLL供电、VCCSA供电等。

SLP_A#控制产生ME模块供电VCCSAW(不支持AMT时,此电压采用桥/总线供电)。

7.各大供电正常,汇总最终送给桥的PWROK和APWROK。

同时产生CPU供电的开启信号,但是一般都不会开启cpu供电,因为缺少SVID8.桥供电正常后25M晶振起振,(PWROK和APWROK正常后)桥发出DRAMPWROK,并读取BIOS。

9.桥发出各路时钟,并返回33M给自身的CLKIN_PCILOOPBACK脚。

10.桥发出非核心电源好PROCPWRGD给CPU。

11.CPU发出SVID给CPU供电芯片。

12.CPU供电芯片输出CPU核心供电。

13.CPU供电芯片发出PG最终转换送给桥的SYS_PWROK。

14.桥发出PLTRST#,分压产生CPU复位(RESET#)。

15.CPU得到复位后,再通过DMI总线到桥,桥再通过SPI总线读取BIOS,开始自检。

16.自检过内存后,CPU再次发出SVID给CPU供电芯片,控制输出集显供电(VAXG、一般0.45V)INTEL 4X系列芯片组的笔记本一般开机过程1、无任何电力供电时(没电池和电源),3V电池产生VCCRTC供给南桥的RTC电路,以保持内部时间的运行和保存CMOS信息。

基于PXI总线的MIC总线通讯控制器模块的设计与实现

基于PXI总线的MIC总线通讯控制器模块的设计与实现李广峰;刘洋;冯健;李远照【摘要】MIC总线是专门为解决在恶劣环境下电力/数据的分配和管理而开发的一种具有高可靠性的现场控制总线,根据某型装甲车辆车电系统的测试要求,对MIC总线通讯功能进行测试,完成车电系统的故障诊断;根据测试要求,设计了一整套的测试系统,该模块为其中的一部分,通过对模块的硬件结构和软件两方面进行了分析,实现了基于PXI总线的MIC总线控制器的数据通讯设计;经过用户一段时间的严格测试,结果表明该模块完全符合MIC总线标准要求,性能稳定可靠,达到设计要求.【期刊名称】《计算机测量与控制》【年(卷),期】2010(018)003【总页数】4页(P568-570,574)【关键词】MIC总线;PXI总线;总线控制器(BC)【作者】李广峰;刘洋;冯健;李远照【作者单位】北京特种车辆研究所,北京,100072;北京特种车辆研究所,北京,100072;北京中海技创科技发展有限公司,北京,100852;北京中海技创科技发展有限公司,北京,100852【正文语种】中文【中图分类】TP3360 引言PXI总线是以CompactPCI为基础的,由具有开放性的PCI总线扩展而来。

PXI总线符合工业标准,在机械、电气和软件特性方面充分发挥了PCI总线的全部优点。

PXI总线的传输速率已经达到132M bit/s(最高为500Mbit/s),是目前已经发布的最高传输速率。

因此,基于PXI总线的仪器硬件将会得到越来越广泛的应用。

本文介绍的MIC总线通信模块是按照PXI规范2.0设计的。

1 MIC总线概述[1]MIC(Multiplexed Electrical Power Control And Monitor/Management Interface Chip)总线是一种简单及可靠的时间分割多路传输串行数据总线,是专门为解决恶劣的军事环境中电力及数据分配和管理问题而开发的一种高可靠性现场总线。

基于FPGA的PCI总线接口硬件调试策略

基于FPGA的PCI总线接口硬件调试策略1.确认硬件连接:首先,确认FPGA和PCI总线接口的硬件连接是否正确,包括PCI总线插槽、电源供应、信号线连接等。

确保接口连接正确可以避免硬件故障对调试过程的影响。

2.确认FPGA设计:确认FPGA设计中PCI总线接口的配置和功能是否符合要求。

检查PCI总线接口的信号约束和时钟设置是否正确,并确保设计支持PCI总线协议的相关规范和特性。

3.电源和地线检查:确保FPGA和PCI总线接口的电源和地线连接良好,并测量电压和地线的稳定性。

如果电源和地线的连接不良,可能会导致电压噪声或地线回流,影响总线接口的性能。

4.信号完整性检查:通过使用示波器或逻辑分析仪等工具,检查总线上的信号波形是否符合预期。

关注时钟信号的稳定性、数据信号的正确性和时序要求是否满足。

5.时序分析:使用时序分析工具检查FPGA和PCI总线接口之间的时序关系。

通过分析时序图,检查总线请求、仲裁、数据传输等过程是否按照协议规范执行,是否存在时序冲突或延迟。

6.信号捕获和仿真:使用抓取信号或仿真工具,观察总线传输的实时信号状态。

通过捕获时刻使信号的状态,可以帮助找到信号传输过程中的错误和问题。

7.调试接口逻辑:如果有问题发生,检查FPGA设计中的接口逻辑是否正确。

验证总线接口的控制信号和数据信号的生成、转发和处理是否符合预期的要求。

8.确认硬件配置:在FPGA上运行PCI总线配置空间,确保FPGA正确响应PCI总线的配置读写请求。

验证PCI总线配置空间的读写命令是否正常执行,以及配置寄存器的值是否与预期相符。

9.时序和时钟设置:在FPGA设计中,确保时钟信号和数据信号的时序设置正确。

根据PCI总线协议的要求和硬件平台的时钟频率,调整时序约束并重新布局时钟和数据路径。

10.联机调试:在硬件调试过程中,保持与PCI总线接口连接的设备或主机处于联机状态。

使用调试和监视工具,观察数据传输的过程和结果,并及时记录和分析错误信息。

X86、ARM等主板调试步骤

2014-3-12

板卡调试步骤

8系列芯片组 的CLOCK架构图:

2014-3-12

板卡调试步骤

七、接口测试:

以上确认都没有问题的话,主板基本都是已经能正常开机了,当然是要保证BIOS 已经调试OK的前期下。接着就需要对板卡上对应的接口功能进行测试: 一)、USB接口: 是否能正常识别设备? 如果有问题,确认步骤如下: 1、BIOS是否禁用? 2、系统下是否禁用? 3、供电是否正常?(PCH PLL也需检查) 4、信号线路是否焊接不良、少料、短路、断路等? 5、USB3.0还要考虑驱动是否安装正确? 6、补偿信号是否有问题? ....

板卡调试步骤

八)、内存: 是否能正常识别设备? 如果有问题,确认步骤如下: 1、供电是否正常?(包括内存和CPU两端都要检查) 2、BIOS CORE是否正确? 3、内存CLOCK是否正确? 4、信号线路是否焊接不良、少料、短路、断路等? ....

2014-3-12

板卡调试步骤

九)、VGA: 是否能正常识别设备? 如果有问题,确认步骤如下: 1、BIOS CORE是否正确? 2、供电是否正常?(PCH PLL检查) 3、信号线路是否焊接不良、少料、短路、断路等? 4、补偿信号是否有问题? ....

2014-3-12

谢谢大家!

2014-3-12

2014-3-12

板卡调试步骤

四)、PCI接口: 是否能正常识别设备? 如果有问题,确认步骤如下: 1、BIOS是否禁用? 2、系统下是否禁用? 3、供电是否正常?(PCH PLL也需检查) 4、信号线路是否焊接不良、少料、短路、断路等? 5、PCI CLOCK是否正常? 6、PCIRST信号是否正常? 7、IRQ资源是否分配? 8、中断配置是否正确? 9、补偿信号是否有问题? ....

PCI接口时序测试方法

PCI接口时序测试方法1.参考文献:(1)Intel(R) I/O Controller Hub 4 (ICH4) External Design Specification(EDS).(No.589)(2)PCI SPECIFICATION V2.2.2.测试目的:在P4D项目(Springdale-G/PE)中, 主要看PCI接口的PCICLK,AD 和C/BE#[3,0]等控制信号的时序质量是否满足规范要求.3.测试内容和规范特别说明:时序测试中PCI接口的参考电平的值为Vtest=-1.5v(对5V环境的PCI卡):The following is refer to ICH4.The following is refer to PCI spec2.2.7.6.4.2 Timing ParametersNOTES:1.See the timing measurement conditions in Figure 7-3. It is important that all driven signaltransitions drive to their V oh of V ol level within one Tcyc.2.Minimum times are measured at the package pin with the load circuit shown in Figure 7-7.Maximum times are measured with the load circuit shown in Figures 7-5 and 7-6.3.REQ# and GNT# are point-to-point signal and have different input setup times than do busedsignals. GNT# and REQ# have a setup of 5 ns at 66 MHz. All other signals are bused.4.See the timing measurement conditions in Figure 7-4.5.If M66EN is asserted, CLK is stable when it meets the requirements in Section 7.6.4.1. RST#is asserted and deasserted asynchronously with respect to CLK. Refer to Section 4.3.2. for more information.6.All output drivers must be floated when RST# is active. Refer to Section 4.3.2. for moreinformation.7.These values are duplicated from Section 4.2.3.2 and are included here for conparison.8.When M66EN is asserted, the minimum specification for T val(min), Tval(ptp)(min), and Tonmay be reduced to 1ns if a mechanism is provided to guarantee a minimum value of 2 ns when M66EN is deasserted.9.For purposes of Active/float timing measurements, the Hi-Z or “off “ state is defined to bewhen the total current delivered through the component pin is less than or equal to the leakage current specification.setup time applies only when the device is not driving the pin. Devices cannot drive and receive signals at the same time.Refer to Section 3.10., item 9 for additional details.4.PCI接口信号说明1)数据,地址和控制信号的对应关系:REQ#,GNT# ----点对点信号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PCI接口时序测试方法1.参考文献:(1)Intel(R) I/O Controller Hub 4 (ICH4) External Design Specification(EDS).(No.589)(2)PCI SPECIFICATION V2.2.2.测试目的:在P4D项目(Springdale-G/PE)中, 主要看PCI接口的PCICLK,AD 和C/BE#[3,0]等控制信号的时序质量是否满足规范要求.3.测试内容和规范特别说明:时序测试中PCI接口的参考电平的值为Vtest=-1.5v(对5V环境的PCI卡):The following is refer to ICH4.The following is refer to PCI spec2.2.7.6.4.2 Timing ParametersNOTES:1.See the timing measurement conditions in Figure 7-3. It is important that all driven signaltransitions drive to their V oh of V ol level within one Tcyc.2.Minimum times are measured at the package pin with the load circuit shown in Figure 7-7.Maximum times are measured with the load circuit shown in Figures 7-5 and 7-6.3.REQ# and GNT# are point-to-point signal and have different input setup times than do busedsignals. GNT# and REQ# have a setup of 5 ns at 66 MHz. All other signals are bused.4.See the timing measurement conditions in Figure 7-4.5.If M66EN is asserted, CLK is stable when it meets the requirements in Section 7.6.4.1. RST#is asserted and deasserted asynchronously with respect to CLK. Refer to Section 4.3.2. for more information.6.All output drivers must be floated when RST# is active. Refer to Section 4.3.2. for moreinformation.7.These values are duplicated from Section 4.2.3.2 and are included here for conparison.8.When M66EN is asserted, the minimum specification for T val(min), Tval(ptp)(min), and Tonmay be reduced to 1ns if a mechanism is provided to guarantee a minimum value of 2 ns when M66EN is deasserted.9.For purposes of Active/float timing measurements, the Hi-Z or “off “ state is defined to bewhen the total current delivered through the component pin is less than or equal to the leakage current specification.setup time applies only when the device is not driving the pin. Devices cannot drive and receive signals at the same time.Refer to Section 3.10., item 9 for additional details.4.PCI接口信号说明1)数据,地址和控制信号的对应关系:REQ#,GNT# ----点对点信号。

AD【31,0】,CBE#【3,0】等其他信号――总线信号。

3)对应每个具体项目,规范中的信号名和项目中的信号名有所区别,需要注意。

5.测试配置1)硬件设置:a)示波器:TEK7104或带宽更高的示波器如7404b)探头:带宽为1.5G的探头P6245共3个,c)测试前各通道探头必须deskew,保证测试结果的正确性,参考deskew方法d)测试时调用配置文件PCI.set(自建,包括触发模式,触发电平,偏移电平,垂直与水平刻度等)e)注意:所需示波器带宽按照被测CLOCK和选通信号的上升和下降时间确定.f)为减小读数误差,测试时尽量让显示图形充满屏幕.2)软件设置:运行3Dmark2000。

6.测试方法1)tvaltval和tval(ptp)分别表示在驱动端数据信号和点对点的延迟时间。

点对点信号指REQ#和GNT#;其他所有信号都是总线信号。

REQ#和GNT#和其他总线信号相比,在输出延迟时间和建立时间上的要求是不同的,GNT#要求建立时间小于10ns,REQ#要求建立时间小于12ns。

1.1)参数意义:tval表示在驱动端,数据信号的延迟时间, 数据信号包括ad[31,0]; 相对于pciclk。

从Pciclk信号的上升沿到总线信号输出有效的时间。

Pciclk信号的上升沿上参考电平为vtest=1.5V,总线信号的参考电平为Vtest(5V信号),Vtrise和Vtfall(3.3v信号)。

目前主板上使用的PCI卡都工作在5v环境(5VIO信号接在Vcc=5V上),所以总线信号的参考电平也采用1.5v。

1.2)测试方法(说明:测试前各通道探头必须deskew,保证测试结果的正确性,参考deskew方法)a)driver端测试:示波器使用三个通道CH1,CH2,CH3. 测试时选用一条数据信号的两端用以判断是Driver还是Receiver. CH1接在AD0靠近ICH一端, CH2接在AD0靠近PCI设备(PCI槽)一端,CH3接在PCICLK靠近PCI槽一端(CH1和CH2用来判定ICH处于读状态还是写状态), 选用数据通道(CH1)作为示波器的触发, 当捕捉到的波形显示CH1超前CH2时,表明ICH处于写操作状态,此时用光标进行测量.b)说明:这里driver端指ICH.1.3)图例(图中通道对应情况与所述内容有所区别,故图中结果仅供参考)2)tval(ptp)tval(ptp)表示在驱动端点对点信号的延迟时间。

2.1)参数意义:tval(ptp)表示在驱动端,点对点信号的延迟时间, 数据信号包括REQ#和GNT#; 相对于pciclk。

从Pciclk信号的上升沿到点对点信号输出有效的时间。

Pciclk信号的上升沿上参考电平为vtest=1.5V,点对点信号的参考电平为Vtest(5V信号),Vtrise和Vtfall(3.3v 信号)。

2.2)测试方法(说明:测试前各通道探头必须deskew,保证测试结果的正确性,参考deskew方法)c)driver端测试:示波器使用三个通道CH1,CH2,CH3. 测试时选用REQ#的两端用以判断是Driver还是Receiver. CH1接在REQ#靠近ICH一端, CH2接在REQ#靠近PCI设备(PCI槽)一端,CH3接在PCICLK靠近PCI槽一端(CH1和CH2用来判定ICH处于读状态还是写状态), 选用数据通道(CH1)作为示波器的触发, 当捕捉到的波形显示CH1超前CH2时,表明ICH处于写操作状态,此时用光标进行测量.d)说明:这里driver端指ICH.e)测量GNT#信号方法同REQ#信号。

2.3)图例(图中通道对应情况与所述内容有所区别,故图中结果仅供参考)3)tsutsu和tsu(ptp)分别表示在接收端数据信号和点对点信号的建立时间。

3.1)参数意义:tsu表示在接收端,数据信号的建立时间, 数据信号包括ad[31,0]; 相对于pciclk。

从总线信号输出有效到Pciclk信号的上升沿的时间。

Pciclk信号的上升沿上参考电平为vtest=1.5V,总线信号的参考电平为Vtest(5V信号),Vtrise和Vtfall(3.3v信号)。

3.2)测试方法(说明:测试前各通道探头必须deskew,保证测试结果的正确性,参考deskew方法)f)driver端测试:示波器使用三个通道CH1,CH2,CH3. 测试时选用一条数据信号的两端用以判断是Driver还是Receiver. CH1接在AD0靠近ICH一端, CH2接在AD0靠近PCI设备(PCI槽)一端,CH3接在PCICLK靠近PCI槽一端(CH1和CH2用来判定ICH处于读状态还是写状态), 选用数据通道(CH1)作为示波器的触发, 当捕捉到的波形显示CH1读CH2时,表明ICH处于读操作状态,此时用光标进行测量.g)说明:这里driver端指ICH.3.3)图例(图中通道对应情况与所述内容有所区别,故图中结果仅供参考)4)tsu(ptp)tsu(ptp)表示在接收端点对点信号的建立时间。

点对点信号指REQ#和GNT#;其他所有信号都是总线信号。

REQ#和GNT#和其他总线信号相比,在输出延迟时间和建立时间上的要求是不同的,GNT#要求建立时间小于10ns,REQ#要求建立时间小于12ns。

4.1)参数意义:tsu(ptp)表示在驱动端,点对点信号的延迟时间, 数据信号包括REQ#和GNT#; 相对于pciclk。

从点对点信号输出有效到Pciclk信号的上升沿的时间。

Pciclk信号的上升沿上参考电平为vtest=1.5V,点对点信号的参考电平为Vtest(5V信号),Vtrise和Vtfall(3.3v 信号)。

4.2)测试方法(说明:测试前各通道探头必须deskew,保证测试结果的正确性,参考deskew方法)h)driver端测试:示波器使用三个通道CH1,CH2,CH3. 测试时选用REQ#的两端用以判断是Driver还是Receiver. CH1接在REQ#靠近ICH一端, CH2接在REQ#靠近PCI设备(PCI槽)一端,CH3接在PCICLK靠近PCI槽一端(CH1和CH2用来判定ICH处于读状态还是写状态), 选用数据通道(CH1)作为示波器的触发, 当捕捉到的波形显示CH1落后CH2时,表明ICH处于读操作状态,此时用光标进行测量.i)说明:这里driver端指ICH.j)测量GNT#信号方法同REQ#信号。