cic滤波器fpga实现

改进的高性能CIC抗混叠滤波器

2012年第07期,第45卷 通 信 技 术 Vol.45,No.07,2012 总第247期 Communications Technology No.247,Totally改进的高性能CIC抗混叠滤波器皇甫文斌, 朱 江, 王世练(国防科学技术大学 电子科学与工程学院,湖南 长沙410073)【摘 要】这里对一种旋转锐化级联积分梳状滤波器(RSCIC,Rotated Sharpening Cascaded Integrator Comb Filter)进行了研究,RSCIC由锐化级联积分梳状滤波器(SCIC,Sharpening Cascaded Integrator Comb Filter)和旋转内插滤波器(Rotated Sinc Filter)两部分构成。

RSCIC可有效地提高传统积分梳状滤波器(CIC, Cascaded Integrator Comb Filter)的通带和阻带传输性能,特别适合采样率转化。

仿真表明,在同等条件下,RSCIC滤波器的阻带衰减性能比传统的CIC滤波器提高了22 dB,通带抗衰减性能比传统的CIC滤波器提高了0.5 dB。

【关键词】采样率转换;积分梳状滤波器;锐化级联积分梳状滤波器;旋转内插滤波器【中图分类号】TN911.72 【文献标识码】A 【文章编号】1002-0802(2012)07-0119-03 Improved High Performance CIC FilterHUANGFu Wen-bin, ZHU Jiang, WANG Shi-lian(School of Electronic Science and Engineering, National University of Defense Technology,Changsha Hunan 410073, China)【Abstract】CIC(Cascaded Integrator Comb) filter, for its simple hardware, is a most commonly-used multistate filter. However, the large distortion of the pass-band and the attenuation of the stop-band limit its applications, a new cascade structure is studied and proposed. Simulation shows that the proposed structure could improves the stop-band attenuation by 30dB as compared with the traditional CIC Filter. The new structure is quite good in the sampling rate conversion.【Key words】sample rate conversion;CIC;sharpening CIC;rotating sharpening CIC0 引言积分梳状滤波器CIC [1]结构简单,不使用乘法器,且不需要预先存储滤波器系数,是目前用于采样率转换常用的滤波器,但是,单一积分梳状滤波器通带和阻带性能相对较差,无法满足实际应用要求[2]。

cic滤波器阶数和级数

CIC滤波器阶数和级数什么是CIC滤波器?CIC(Cascaded Integrator-Comb)滤波器是一种数字滤波器结构,常用于高速数据采样系统中的抽取滤波。

CIC滤波器具有简单的结构和低成本的优点,且能够实现高度的抽取比率。

CIC滤波器是一种结构紧凑的滤波器,由级联的积分器和组合器构成。

积分器将输入信号进行积分,而组合器则通过取差来减小输出的冗余部分。

这种结构使CIC滤波器能够实现高阶滤波器,同时保持较低的计算复杂度。

滤波器阶数CIC滤波器的阶数是指滤波器内部级联的积分器和组合器的数量。

阶数越高,滤波器的频率响应越陡峭,对高频噪声的抑制能力也越强。

然而,阶数的增加会使滤波器的延迟增加,因此在选择CIC滤波器的阶数时需要考虑频率响应和延迟之间的权衡。

滤波器级数CIC滤波器的级数是指滤波器多个CIC结构级联的数量。

级数越多,滤波器的整体增益越大,抽取比率也越高。

通过级联多个CIC结构,可以实现更高的滤波器抽取比率,而不需要增加单个CIC结构的阶数。

CIC滤波器的设计步骤设计CIC滤波器的步骤主要包括选择滤波器的阶数和级数、计算滤波器的延迟和频率响应,以及优化滤波器的性能。

1. 选择滤波器的阶数和级数首先,需要确定CIC滤波器的阶数和级数。

阶数和级数的选择取决于应用的需求,包括滤波器的抽取比率、频率响应和延迟等方面的要求。

2. 计算滤波器的延迟根据滤波器的抽取比率和级数,可以计算出滤波器的延迟。

延迟是指从输入信号进入滤波器到输出信号出现的时间延迟。

3. 计算滤波器的频率响应根据滤波器的抽取比率、阶数和级数,可以计算得到滤波器的频率响应。

频率响应描述了滤波器对不同频率信号的强度衰减或增益。

4. 优化滤波器的性能根据实际需求,可以对滤波器进行性能优化。

优化可以包括调整滤波器的参数,如阶数和级数,以及对滤波器的设计进行仿真和验证。

CIC滤波器的应用领域CIC滤波器广泛应用于高速数据采样系统中,特别是在射频接收器和数字信号处理系统中。

CIC滤波器学习笔记

学习笔记: CIC filter及其matlab实现References:[1] Understanding cascaded integrator-comb filters – By Richard Lyons, Courtesy of Embedded Systems ProgrammingURL: .com/articles/article10028.html[2] Example of Cascaded Integrator Comb filter in Matlab[3] Digital Signal Processing – Principles, Algorithms and Applications , John G. Proakis, Dimitris G. ManolakisCIC数字滤波器是窄带低通滤波器的高计算效率的实现形式,常常被嵌入到现代通信系统的抽取和插值模块的硬件实现中。

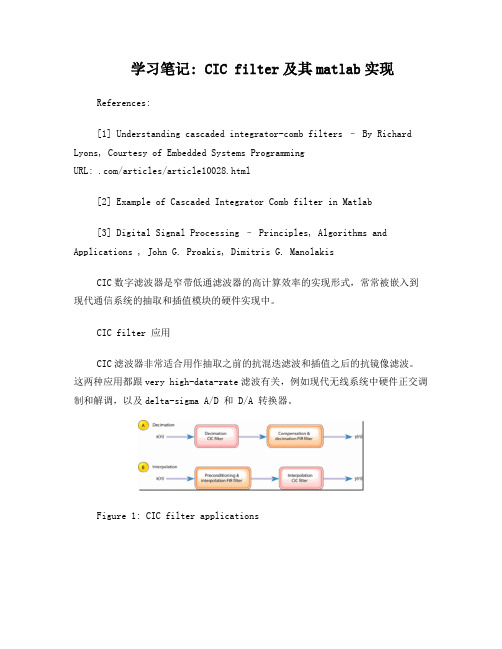

CIC filter 应用CIC滤波器非常适合用作抽取之前的抗混迭滤波和插值之后的抗镜像滤波。

这两种应用都跟very high-data-rate滤波有关,例如现代无线系统中硬件正交调制和解调,以及delta-sigma A/D 和 D/A 转换器。

Figure 1: CIC filter applications因为CIC滤波器的幅频响应包络象sin(x)/x,通常在CIC滤波器之前或者之后都有一个high-performance linear-phase lowpass tapped-delay-line FIR filters, 用于补偿CIC滤波器不够平坦的通带。

CIC滤波器不需要乘法运算,易于硬件实现。

抽取CIC滤波器只不过是滑动平均滤波器的一个非常高效的迭代实现,有NR taps, 其输出再进行 R 抽取 . 同样,插值CIC滤波器在每两个输入采样之间插入R -1个0,然后通过一个NR -tap的工作在输出采样率?s ,out 的滑动平均滤波器。

(完整版)CIC滤波器的原理与设计

CIC 的冲击响应{1,010,()n D h n ≤≤-=其他,D 为CIC 滤波器的阶数(即抽取因子),Z 变换后11()1Dz H z z ---=-,当积分梳状滤波器的阶数不等于抽取器的抽取倍数时,令N=DM(N 为滤波器的 阶数,D 为抽取倍数)则积分梳状滤波器的传递函数为:)1(11)(1DM z zz H ----=M 是梳状滤波器中的延时因子,故称M 为差分延时因子;其频率总响应为12()()()jw jw jwH e H e H e ==sin(/2)sin(/2)wDM w =1()()22wDM wDM Sa Sa -⋅⋅x x x Sa /)sin()(=为抽样函数,且1)0(=Sa ,所以CIC 滤波器在0=ω处的幅度值为N ,即:DM e H j =)(0; 一般数字滤波器的指标:()20lg()()20lg ()a pa p a s a s H j H j H j H j ααΩ=ΩΩ=Ω通带最大衰减阻带最小衰减即:CIC 幅频特性响应曲线图由其频率响应函数可以看出其主瓣电平最大为D ,旁瓣电平为21.51()sin(3/2)/sin(3/2)sin(3/2)j DMH e DM DM ωπωπππ=⋅==,旁瓣与主瓣的差值 (用dB 数表示)为: dB A DM s 46.1323lg 20lg201===πα 可计算出旁瓣与主瓣的差值约为13.46,意味着阻带衰减很差,单级级联时旁瓣电平很大,为降低旁瓣电平,增加阻带衰减采用级联的方式,N 级频率响应为:)2()2()()2/sin()2/sin()(ωωωωωQ Q Q Qj Q Sa DM Sa DM DM e H -⋅⋅=⎥⎦⎤⎢⎣⎡=, 可得到N 级CIC 的旁瓣抑制 dB Q Q A DM Q Qs )46.13(23lg 20)lg(201⨯=⋅==πα 分析一下发现在Q 级联时多出了Q DM 这个处理增益,因此分析一下尽量减少带内容差(通带衰减),即,在通带内,幅度应尽量平缓;下面就它的幅平响应曲线来分析:00()20lg ()()20lg()ps j a p jw a j a s jw a H e H eH e H e αα==1、设在红线w1处抽取的信号带宽很窄,为无混叠信号的带宽,能很好的对窄带信号进行滤波,去除掉高频信号噪声;且在绿线w2=2pi/DM-w1处衰减值足够大,则在其信号带宽内,红线到绿线,信号给CIC 滤波器带来的混叠就可以忽略,计算此时阻带衰减:)2/sin()2/sin(lg 20()(lg 2022012w DM w DM e H e H A jw j ==·引入带宽比例因子b=B/(fs/DM ), B 为抽取信号的带宽,D 为抽取因子,M 为延时因子;fs 为输入端采样率,则w1=b*2pi/DM ;带入可化简得:b A lg 201-≈; (假设b=0.01;即fs=100MHz ,D=20,信号带宽为50khz,此时衰减为40dB);可见单级的CIC 滤波器的无混叠信号带宽内的阻带衰减能达到40dB;;并不怎么大,适用于较粗略的滤波,适合放在第一级抽取;如果采用级联的方式可以加大无混叠信号带宽;但是满足的通带不够窄;2、在红线w1处幅度不能下降太多,通带内幅值容差不能太大,否则会引起高频失真;设该带内容差为s δ,则,)()(lg 2010jw j s e H e H =δ将w1带入可简化得)sin(lg 20b bs ππδ≈,当N 级时,其带内容差也会增大;由上面分析可知,阻带衰减和带内容差,只与带宽比例因子b 有关,Df Bb s /=,分析可知,在信号带宽一定的前提下,应尽可能采用小的抽取因子,或增大输入采样率;故一般把它放在抽取系统的第一级,所以在配置CIC 时,信号带宽,采样率,抽取因子,综合考虑,下面是阻带衰减和通带衰减的一个表:表1:大抽取因子下的通带衰减由CIC频幅响应图可以发现,幅频特性的零点位于1/M处(M取值为整数),这说明差分因子M决定了零点的位置;抽取因子D狭定了抽取后信号的采样频率,它同差分延时因子M一起还决定了主瓣和旁瓣的宽度;级数Q可以用来控制阻带衰减,Q越大阻带衰减越大,通带内的混叠就越小,但Q越大,通带内主瓣衰减也越大,所以Q不可太大,不宜超过5级。

高速CIC插值滤波器的位宽与优化

1432012年第09期,第45卷 通 信 技 术 Vol.45,No.09,2012总第249期 Communications Technology No.249,Totally高速CIC 插值滤波器的位宽分析与优化﹡聂 阳, 戈 华, 赵鹏宇(集宁师范学院 物理系,内蒙古 集宁 012000 )【摘 要】分析了级联积分-梳状(CIC,Cascaded Integrator Comb)插值滤波器的位宽增长原因,重点研究了CIC 插值滤波器非等值位宽的数据通路设计。

在此基础上利用Matlab 和Xilinx System Generator 开发工具搭建了电路的系统模型,最后通过现场可编程门阵列(FPGA,Field Programmable Gate Array)完成电路的寄存器传输级(RTL,Register Transfer Level)验证,仿真结果表明电路设计具有很高的有效性和可行性。

【关键词】CIC 插值滤波器;位宽;FPGA 【中图分类号】TN911.7 【文献标识码】A 【文章编号】1002-0802(2012)09-0143-03Analysis and Optimization of High-Speed CIC Interpolation Filter WidthNIE Yang, GE Hua, ZHAO Peng-yu(Dept of Physics, Jining Teachers College, Jining Inner Mongolia 012000, China )【Abstract】This paper analyzes the increase of CIC (Cascaded Integrator Comb) interpolation filter width, and focuses on the data path design of non equivalent width. Based on this and with Matlab and Xilinx System Generator development tools, the system model of the circuit is built up, and finally through FPGA (Field Programmable Gate Array) RTL (Register Transfer Level), the verification of the circuit is completed. And simulation indicates the effectiveness and feasibility of circuit design.【Key words】CIC interpolation filter; width; FPGA0 引言随着现代无线通信中数据传输率的增加,在一个信号处理系统中常常需要不同的采样率处理信号以及不同采样率的信号之间相互转换。

一种载波同步的实现方法

一种载波同步的实现方法孙东;张刊;秦江【摘要】本文主要讲述了用FFT+ PLL+ CIC组合技术实现载波同步的方法,和传统的用PLL+ CIC实现载波同步相比,该方法具有载波同步动态大的优势.在实际应用中根据不同的侧重点,选取符合要求的载波同步方法.【期刊名称】《火控雷达技术》【年(卷),期】2013(042)001【总页数】5页(P74-78)【关键词】FFT;PLL;CIC;载波同步【作者】孙东;张刊;秦江【作者单位】西安电子工程研究所西安710100【正文语种】中文【中图分类】TN911.71 引言同步是通信系统中一个重要的实际问题。

当采用同步解调或相干检测时,接收端需要提供一个与发射端调制载波同频同相的相干载波。

这个相干载波的获取就称为载波提取,或称为载波同步。

在接收机中,有两种基本的方法处理载波同步。

第一种方法是插入导频法。

通常在频域插入一个导频信号,接收机通过提取导频,使本地振荡器与接收信号的载波频率和相位同步。

接收机通过一个锁相环(PLL)获取并跟踪导频分量,由于PLL具有窄带宽,因此不会明显受到携带信息信号频率成分的影响。

第二种方法是直接法,不需要传输导频,直接从已调信号中恢复载波同步信号。

在实践中,这两种方法都有所应用。

但第二种方法具有一个明显的优点,即全部发送功率分配给携带信息的信号传输[2]。

本文采用直接法实现载波同步,介绍了用FFT+PLL+CIC基于FPGA实现载波同步。

通过比较用PLL+CIC技术和FFT+PLL+CIC组合技术的实现情况,来说明FFT+PLL+CIC实现载波同步的优缺点。

2 系统结构与原理图1为系统总体结构图,信号通过FFT来减小本振与输入信号载波之间的频差,然后通过PLL实现高精度的载波同步,其主要模块原理介绍如下。

图1 系统结构图2.1 锁相环——同相正交环法利用锁相环(PLL)提取载波的一种常用方法——同相正交环法如图2所示。

加于两个相乘器的本地信号分别为压控振荡器的输出信号cos(wct+θ)和它的正交信号sin(wct+θ)。

c语言实现cic梳状滤波__理论说明

c语言实现cic梳状滤波理论说明1. 引言1.1 概述CIC(Cascade Integrator-Combinator)梳状滤波器是一种常见的数字滤波器,广泛应用于信号处理领域。

它具有简单的结构和高效的运行特性,在数字信号处理中发挥着重要作用。

本文将介绍CIC梳状滤波器的原理和C语言实现原理,并讨论其在不同领域中的应用。

1.2 文章结构本文分为五个部分。

引言部分介绍了文章的背景和结构安排。

第二部分讲解了CIC梳状滤波器的原理以及C语言实现原理,并对相关算法进行了介绍。

第三部分探讨了CIC梳状滤波器在不同领域中的应用场景,包括数字信号处理、实时数据处理和音频信号处理等方面。

第四部分详细解释了如何使用C语言来实现CIC梳状滤波器,包括硬件平台准备、基本组件搭建与初始化配置以及数据输入与处理流程设计等方面内容。

最后,第五部分将对实验结果进行分析并展示其效果,并对整篇文章进行总结与展望。

1.3 目的本文的目的是介绍CIC梳状滤波器的原理和C语言实现原理,并探讨其在不同领域中的应用场景。

通过详细解释C语言实现CIC梳状滤波器的步骤,读者可以加深对该滤波器的理解,并了解如何将其应用于具体项目中。

最后,通过对实验结果进行分析与总结,读者可以评估CIC梳状滤波器在不同场景下的性能表现,并对其未来发展进行展望。

2. 理论基础:2.1 CIC梳状滤波器原理CIC(Cascade Integrator-Comb)梳状滤波器是一种常用的数字信号处理滤波器,用于对离散时间序列进行低通滤波。

它由级联部分积分器和组合部分组成。

CIC梳状滤波器的输入信号首先经过M个阶数为R的积分级,在每一级中累加了M个输入样本,然后被一个差分延时线延时M/R个采样周期。

延时后的信号经过一个减法运算,乘以一个增益因子D,并通过R级组合部分,其中每一级包含一个差分延时线和一个减法运算单元。

最终输出结果是经过R级积分之后的信号。

2.2 C语言实现原理在C语言中实现CIC梳状滤波器需要定义相应的数据结构和函数来实现不同模块之间的连接和数据处理。

cic滤波器中间位宽截断

cic滤波器中间位宽截断

cic滤波器中间位宽截断是数字信号处理中常用的一种技术,用于减小滤波器的计算复杂度和存储需求。

通过对数字信号进行采样和滤波,可以实现对信号的处理和分析。

在cic滤波器中,中间位宽截断是一种常见的优化方法,可以进一步减小滤波器的计算量。

中间位宽截断的主要思想是在滤波过程中,对中间结果进行位宽的截断。

由于滤波器的计算通常涉及到大量的乘法操作,而乘法操作的计算量较大,中间位宽截断可以通过减小乘法操作的位宽,从而减小计算量,提高滤波器的运行效率。

具体而言,中间位宽截断可以通过两种方式实现。

一种是对输入信号进行位宽截断,即在滤波器的输入端将信号的位宽减小。

这样可以减小乘法操作的位宽,从而降低计算复杂度。

另一种方式是对滤波器的中间结果进行位宽截断,即在滤波器的计算过程中,对乘法操作的结果进行位宽截断。

这样可以减小中间结果的位宽,进一步降低计算量。

中间位宽截断虽然可以减小计算复杂度,但也会引入一定的误差。

位宽的减小会导致精度的降低,从而影响滤波器的性能。

因此,在使用中间位宽截断时,需要权衡计算复杂度和滤波器性能之间的关系,选择合适的位宽截断策略。

cic滤波器中间位宽截断是一种常用的优化技术,可以降低滤波器的

计算复杂度。

在实际应用中,需要根据具体情况选择合适的位宽截断策略,以实现滤波器的高效运行。

通过合理的位宽截断策略,可以在保证计算效率的同时,满足滤波器对精度的要求。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

cic滤波器的FPGA实现发布时间:2016-01-26 15:07:21技术类别:CPLD/FPGA一、关于多采样率数字滤波器很明显从字面意思上可以理解,多采样率嘛,就是有多个采样率呗。

前面所说的FIR,IIR滤波器都是只有一个采样频率,是固定不变的采样率,然而有些情况下需要不同采样频率下的信号,具体例子我也不解释了,我们大学课本上多速率数字信号处理这一章也都举了不少的例子。

按照传统的速率转换理论,我们要实现采样速率的转换,可以这样做,假如有一个有用的正弦波模拟信号,AD采样速率是f1,现在我需要用到的是采样频率是f2的信号,传统做法是将这个经过f1采样后的信号进行DA转换,再将转换后的模拟信号进行以f2采样频率的抽样,得到采样率为f2的数字信号,至此完成采样频率的转换但是这样的做法不仅麻烦,而且处理不好的话会使信号受到损伤,所以这种思想就被淘汰了,现在我们用到的采样率转换的方法就是抽取与内插的思想。

二、抽取先来总体来解释一下抽取的含义:前面不是说,一个有用的正弦波模拟信号经采样频率为f1的抽样信号抽样后得到了数字信号,很明显这个数字信号序列是在f1频率下得到的,现在,假如我隔几个点抽取一个信号,比如就是5吧,我隔5个点抽取一个信号,是不是就是相当于我采用了1/5倍f1的采样频率对模拟信号进行采样了?所以,抽取的过程就是降低抽样率的过程,但是我们知道,这是在时域的抽样,时域的抽样等于信号在频域波形的周期延拓,周期就是采样频率,所以,为了避免在频域发生频谱混叠,抽样定理也是我们要考虑的因素下面来具体来介绍如上图所示,假如上面就是某一有用信号经采样频率f1抽样得到的频谱,假设这时候的采样频率为8 Khz ,可以通过数格子得到,从0到F1处有8个空格,每个空格代表1Khz,有些朋友可能会问,这不是在数字频域吗,单位不是π吗,哪来的hz?是的,这里是数字频域,采样频率F1处对应的是2π,这里只是为了好解释,我们用模拟频率来对应数字频率。

上面是采样频率为8K的数字信号频域图,现在我要对这个数字信号进行时域抽取,从而来降低信号的采样率,我们知道,一旦我们对数字信号进行时域抽取,那么采样率下降,而采样率就是数字信号频域的波形周期,那么也就是周期下降,所以,我们对信号进行抽取要有个度,要在满足抽样定理的条件下对信号进行抽取,否则就会发生频谱混叠。

上图就是对信号进行了1/5倍的F1采样频率抽取,可见,由于发生了频谱混叠现象,因为1/5倍的F1是1600hz,而信号的频带是1000hz,不满足抽样定理,导致发生了频谱混叠,所以,为了避免发生这种情况,除了要满足抽样定理之外,即抽样倍数不能太高,我们还需要把信号的频带设置在F1/2以下,才能确保信号不发生频谱混叠,因此,我们需要在抽取之前加一个低通滤波器,书上叫做抗混叠低通滤波器,用来限制信号的频带,然后再进行抽取,这样的话我们来算一下低通滤波器的截止频率就是1/2倍的经抽取后的采样速率,即fc = 1/2 * (F1/M),M是抽取倍数。

而1/2 *F1对应的数域频率是π,因此我们得出,抗混叠低通滤波器的截止频率是π/M三、内插抽取的过程是降低采样率的过程,那么插值的过程当然就是提高采样率的过程。

大体的思路可以这么理解,我们将经f1抽样下得到的数字信号的每两个点之间进行插值,插入的值是0,插值之后,信号在单位时间内的采样点数增多,当然也就是采样速率的提升,采样速率提升后我们知道,那么信号的频谱的周期就会增加需要注意的一点就是,插值前后,我们只是在时域信号中间插入了D-1个零值,仅仅是改变了采样率,并没有改变信号的信息,因此,在频域,信号频谱的形状是不会改变的,改变的仅仅是周期,如上图,F1是插值之前信号的周期,插值之后,信号频谱的形状不变,周期成了F1 *D,D是插值倍数。

如果我们直接用F1 *D倍的采样率采信号,得到的频谱会发现,就不会有中间两个波形,因此,这两个波形是多余的,书上叫做是镜像频谱。

既然是多余的,我们就可以将它用一个低通滤波器滤掉,这样的低通滤波器,就叫做镜像低通滤波器。

这样我们来计算一下镜像低通滤波器的截止频率根据上面这张图我们可以求出镜像低通滤波器的截止频率,可以看到,fc = 1/2 *F1,这里我们假设,内插之后的采样频率为F2 = F1*D,那么,fc =1/2 *(F2/D),而1/2*F2对应的是π,注意,这里是1/2*F2对应π,不是1/2*F1了,因为这已经是插值之后采样率增加之后的频谱了,所以我们得出:镜像低通滤波器的截止频率为:π/D四、分数倍抽取与内插根据前面抽取与内插的介绍我们知道了,内插的过程是先进行内插处理,再通过镜像低通滤波器,抽取的过程就是先进行抗混叠低通滤波,再进行抽取,我们可以看出来,假如我们想进行分数倍抽取,比如我要进行3/5倍抽取,就可以先进行3倍内插,再进行5倍抽取,这样就可以实现分数倍抽取。

再来看一下,当进行分数倍抽取与内插的时候,镜像低通滤波器和抗混叠低通滤波器是连在一起的,因此,我们可以将这两个滤波器合二为一,截止频率取两个滤波器截止频率的最小值就可以了五、多速率滤波器的Matlab实现这里我们假设,要对一个频率为100hz的正弦波模拟信号进行抽样,抽样频率为900hz,现在我要对采样信号进行5/3倍提升根据我们前面分析的,进行分数倍的抽样率转换,先要进行内插处理,内插的过程就是在原有的时域信号之间,插入I - 1个零值点,采用matlab实现很简单,首先我们可以计算插值完成之后信号的长度,然后将原来信号进行填充即可插值完成之后,需要进行低通滤波,由前面的讨论可以知道,根据低通滤波器的截止频率计算公式,来计算滤波器截止频率为π/I,然后调用函数生成FIR滤波器系数即可。

紧接着,需要进行的是抽取处理,抽取过程的算法跟内插类似,可以先计算抽取之后的信号的长度,然后每个D个采样点进行一次抽取下面看一张图,是我绘制了这个过程的整个流程根据上面这张图我们可以看到,最上面的是原始信号经900hz频率采样后得到的信号时域波形,然后我对其进行了5倍内插,也就是在每两个采样点之间插入了4个零值,之后通过了低通滤波器,去掉镜像波形后的时域波形,可以看到,此时的采样率已经是原来的5倍,接着对其进行3倍抽取,即每隔两个点抽取一个点作为新的采样点,得到最下面的时域波形,整个过程原始信号没有发生变化,变化的仅仅是采样率。

六、关于CIC滤波器说了这么多,终于进入正题了。

前面的都是些基础知识,只有先掌握了前面的内容,才能理解下面的知识,包括下两篇文章要讲的FIR半带滤波器和多相结构的FIR半带滤波器。

CIC滤波器呢,是积分梳状滤波器的英文简称,先来看CIC滤波器的单位冲击响应很明显的一个特征就是,CIC滤波器的单位脉冲响应只有0和1,再来想一下,既然单位脉冲响应只有0和1,那么也就是意味着,我们在进行卷积运算的时候,就不需要乘法器,为什么呢?因为滤波器系数为1的话,相当于将输入信号乘了个1,所以就不需要乘法器,只需要加法器就可以完成卷积运算,正因为如此,CIC滤波器结构简单,非常适合工作在高采样率条件下但是这并不是我们常用的滤波器结构,既然是积分梳状滤波器,总得体现一下积分、和梳状这两个特点吧,这名字不是白叫的,因此有如下变形可以看到,上面的式子是CIC滤波器的系统函数,对其进行变换之后可以得到两个部分的乘积形式,即分子部分为一个梳状FIR滤波器,剩余部分为一个积分器,至此,我们CIC滤波器的结构才已经成型。

根据变形后的CIC滤波器的系统函数可以知道,滤波器的极点为1,因此看上去滤波器是一个不稳定的系统,但是从整体角度来看,这个结构是由一个FIR滤波器变形而来的,本身是一个因果稳定的,因此,变形后的系统应该也是一个因果稳定的,因此我们考虑到零极点抵消的原因,致使变形后的系统仍是一个因果稳定的系统。

从单级CIC滤波器的幅频响应考虑,由于其特殊的结构,导致单级CIC滤波器的衰减不足,可以见下图可见,单级CIC滤波器滤波器的衰减并不是很足,在阶数比较大的情况下,CIC滤波器的衰减一般稳定在13.6dB,要想加大衰减,就必须采用多级CIC滤波器级联的形式,每增加一级滤波器,阻带衰减增加13.6dB,但是为了增加阻带衰减而采用级联方式,也会导致一些弊端,为此,这方面的知识总结如下,具体理论不再解释了,书上的推导过程比较复杂,大家还是自己看书为好。

总结:1、要同时满足通带容限跟阻带容限的误差的CIC滤波器实现起来比较困难,因为要想阻带衰减大,就要增大滤波器级数,但是会导致通带容限增大。

2、如果要实现这样的滤波器,只有当有用信号的频带相对于采样信号的速率很小时才能设计出符合要求的滤波器,这样的话通带衰减较大的情况下也对有用信号影响较小。

3、有用信号的频带相对于采样信号的速率很小也就是意味着信号的采样率很高,所以,CIC滤波器适合应用在多速率信号处理的前端,作为抗混叠滤波器来用,或者是作为后端的抗混叠插值滤波器。

七、多级 Hogenauer CIC抽取滤波器的FPGA实现Hogenauer CIC抽取滤波器是一种特殊的结构,可以用来提高滤波器的运行速度,节省硬件资源等前面已经说过了,CIC滤波器的系统函数经过变形之后,可以得到一个M阶的梳状滤波器和一个积分器相乘的形式,二者共同组成了抗混叠低通滤波器,在抽取的过程中,一般是信号先经过抗混叠低通滤波器进行滤波,来避免频谱混叠现象的发生,然后再进行抽取处理,但是我们可以利用Noble恒等式,先对信号进行抽取,再对其进行滤波,即也就是说,在滤波器阶数跟抽取倍数相同的情况下,如果先滤波后抽取,那么滤波器的长度是M,但是如果先抽取后滤波,那么滤波器的长度就会降低为1阶,因此,采用Noble恒等式,先抽取后滤波,可以降低滤波器长度,从而达到节省硬件资源的目的。

前面说了,单级的CIC滤波器很难满足需求,要达到一定的阻带衰减,就必须通过级联的方式我们可以看到,如果是三级的CICI滤波器级联的话,也就是有3个积分器和三个梳状滤波器,这时候我们可以利用Noble恒等式进行移位变换,让积分器放在一起,梳状滤波器放在一起,这时候的梳状滤波器是M阶的,因为此时还没有经过抽取,所以我们可以再利用Noble恒等式,将抽取器放到梳状滤波器之前,这样的话,梳状滤波器就会降为1阶,长度为2,从而大大节省了硬件资源现在我们假设抽取倍数是5,根据要求,这时我们的滤波器长度也应该是5,采用3级CIC滤波器级联的方式,用Hogenauer CIC抽取滤波器结构在FPGA上设计1、三级积分器模块altera 的CIC滤波器的IP核手册中给出了CIC滤波器中间运算数据字长的计算公式,这里我们假设我们的输入数据是经过10bit量化过的正弦波数字信号,那么CIC滤波器的中间运算字长为:Wi = Win +N*log2(MD)Win 是输入字长为10,N为滤波器长度5,M为抽取倍数5,D位级联数3因此算得CIC滤波器的中间字长为 Wi = 10 +5*log2(5*3) =30知道了我们中间运算的字长就可以来设计我们的模块了,首先是积分器积分器的设计比较简单,就是一个反馈回路,输出结果跟输入相加后延时一个时钟单元后再与输入相加剩下两级积分器也是一样,第一级积分器的输出要送到第二级积分器的输入,代码这里不再列出,都是跟第一级积分器类似2、五倍抽取器抽取器的实现很简单,从积分器输出的数据,我们每隔5个数据抽取一个数据就好了3、三级梳状滤波器我们知道,经过抽取之后的梳状滤波器阶数降为1,长度为2的这样一个FIR滤波器,由于他的频谱很像一把梳子,因此得名为梳状滤波器。