许多基本CMOS电路的版图

CMOS门电路

CMOS门电

CMOS组合逻辑门的实现

• 每个输入端必接到一对NMOS和 PMOS管栅极上 • 构成组合逻辑的NMOS和PMOS必 须互补 • NMOS串联实现“与” • NMOS并联实现“或”

CMOS门电

CMOS组合逻辑门的实现

• NMOS支路并联实现各支路函数的 “或” • 各部分逻辑函数串联时实现“与” 以上构成CMOS电路的NMOS部分 • 输出为NMOS部分的“反” • PMOS部分为NMOS部分的对偶电路

CMOS门电

即:

0 0 0 1 1 0 1 1

1 0 0 0

可以看出,输出F与输入A,B 之间是“或非”逻辑

F = A+ B

CMOS门电

怎 么 样 实 现 “与 ” “或 ” 逻 辑 ? 只要在上述的CMOS“与 非门”或者“或非门” 电路后再加一级倒相器 就可以得到相应的 CMOS“与门”或者“或 门”电路了

CMOS门电路 CMOS门电路

回 顾

基本逻辑关系

“与” F=AB “或” F=A+B

“与非” F = AB “或非” F = A+ B “异或”

F = A ⊕ B = AB + AB

CMOS门电

CMOS基本逻辑门电路 CMOS基本逻辑门电路 S与非门及或非门

VDD

COMS与非门电路

T3 T4

F = A• B

P并N串

A

T2

T1

B

CMOS门电

工作原理

① 当输入端输入的均为“1”,T1,T2管都 导通,T3,T4都截止,输出“O” ② 若输入端中有一个输入“0”,则由于两 个串联的N管中有一个截止,使得输出对 地不能构成通路,同时,由于并联的P管 中有一个导通,因而输出和电源之间可以 形成通路,输出“1” ③ 若输入端输入的都为“0”,T1,T2管都 截止,T3,T4管都导通,输出“1”

CMOS模拟集成电路设计-ch18版图

减小衬底耦合效应的措施

地反射(续) 衬底应与那个“地”相连?

与瞬态电流以及LA、LD的大小决定。

减小衬底耦合效应的措施

地反射(续)

由于地反射,单端输入的参考电位 会受到严重影响。可采用差动的工 作方式。

S: 间距

Spacing should be as small as possible.

S – L ↓ as mutual inductance decreases.

Use minimum metal spacing in the technology

N: 圈数

Use a value that gives a layout convenient to work other parts of circuits

Poly-poly (option)

Metalmetal

Metalsubstrate

Metalpoly

Polysubstrate

Junction capacitors

Capa. [aF/mm2]

5300 1000

50 30~40 50~60

120 ~1000

VC [ppm/V]

huge 10 20

big

A good design usually has D < 200 mm

W: 线宽

Medal width should be as wide as possible. W – Q as Rs However, W > Wopt, skin effects appear in metal traces, increasing Rs. A good design uses 10 mm < W < 20 mm

CMOS工艺流程和MOS电路版图举例.ppt

1) 简化N阱CMOS 工艺演示

2

氧化层生长

氧化层 P-SUB

光刻1,刻N阱掩膜版

3

掩膜版

曝光

光刻胶 光刻1,刻N阱掩膜版

4

氧化层的刻蚀

光刻1,刻N阱掩膜版

5

N阱注入

光刻1,刻N阱掩膜版

6

形成N阱

N阱 P-SUB

7

氮化硅的刻蚀

二氧化硅

掩膜版

N阱

光刻2,刻有源区掩膜版

场氧的生长

二氧化硅

甘油

甘油

55

然后在表面氧化二氧化硅膜以减小后 一步氮化硅对晶圆的表面应力。

涂覆光阻(完整过程包括,甩胶→预 烘→曝光→显影→后烘→腐蚀→去除光 刻胶)。其中二氧化硅以氧化形成,氮化 硅LPCVD沉积形成(以氨、硅烷、乙硅烷 反应生成)。

56

光刻技术去除不想要的部分,此步骤为定 出P型阱区域。 (所谓光刻胶就是对光或电子束 敏感且耐腐蚀能力强的材料,常用的光阻液有 S1813,AZ5214等)。光刻胶的去除可以用臭氧烧 除也可用专用剥离液。氮化硅用180℃的磷酸去 除或含CF4气体的等离子刻蚀(RIE)。

31

多晶硅淀积

栅氧化层

多晶硅 N阱

32

光刻4,刻NMOS管硅栅, 磷离子注入形成NMOS管

NMOS管硅栅

用光刻胶做掩蔽 N阱

33

光刻5,刻PMOS管硅栅, 硼离子注入及推进,形成PMOS管

用光刻胶做掩蔽

PMOS管硅栅

N阱

34

磷硅玻璃淀积

磷硅玻璃 N阱

35

光刻6,刻孔、磷硅玻璃淀积回流 (图中有误,没刻出孔)

阈值电压调整注入 光刻3,VTP调整注入 光刻4,VTN调整注入

MOS管及简单CMOS逻辑门电路原理图

MOS管及简单CMOS逻辑门电路原理图现代单片机主要是采用CMOS工艺制成的。

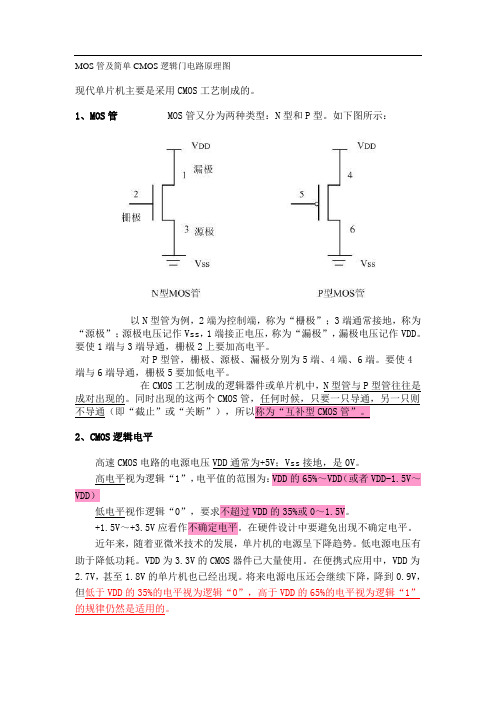

1、MOS管 MOS管又分为两种类型:N型和P型。

如下图所示:以N型管为例,2端为控制端,称为“栅极”;3端通常接地,称为“源极”;源极电压记作Vss,1端接正电压,称为“漏极”,漏极电压记作VDD。

要使1端与3端导通,栅极2上要加高电平。

对P型管,栅极、源极、漏极分别为5端、4端、6端。

要使4端与6端导通,栅极5要加低电平。

在CMOS工艺制成的逻辑器件或单片机中,N型管与P型管往往是成对出现的。

同时出现的这两个CMOS管,任何时候,只要一只导通,另一只则不导通(即“截止”或“关断”),所以称为“互补型CMOS管”。

2、CMOS逻辑电平高速CMOS电路的电源电压VDD通常为+5V;Vss接地,是0V。

高电平视为逻辑“1”,电平值的范围为:VDD的65%~VDD(或者VDD-1.5V~VDD)低电平视作逻辑“0”,要求不超过VDD的35%或0~1.5V。

+1.5V~+3.5V应看作不确定电平。

在硬件设计中要避免出现不确定电平。

近年来,随着亚微米技术的发展,单片机的电源呈下降趋势。

低电源电压有助于降低功耗。

VDD为3.3V的CMOS器件已大量使用。

在便携式应用中,VDD为2.7V,甚至1.8V的单片机也已经出现。

将来电源电压还会继续下降,降到0.9V,但低于VDD的35%的电平视为逻辑“0”,高于VDD的65%的电平视为逻辑“1”的规律仍然是适用的。

3、非门非门(反向器)是最简单的门电路,由一对CMOS管组成。

其工作原理如下:A端为高电平时,P型管截止,N型管导通,输出端C的电平与Vss保持一致,输出低电平;A端为低电平时,P型管导通,N型管截止,输出端C的电平与V DD一致,输出高电平。

4、与非门与非门工作原理:①、A、B输入均为低电平时,1、2管导通,3、4管截止,C端电压与V DD 一致,输出高电平。

②、A输入高电平,B输入低电平时,1、3管导通,2、4管截止,C端电位与1管的漏极保持一致,输出高电平。

CMOS数字电路基本单元PPT课件

第16页/共38页

2)、单元配置恰当 (1)芯片面积降低10%,管芯成品率/圆片 可提高1520%。 (2)多用并联形式,如或非门,少用串联形式,如与非门。 (3)大跨导管采用梳状或马蹄形,小跨导管采用条状图形, 使图形排列尽可能规整。

17

第17页/共38页

3)、布线合理

•布线面积往往为其电路元器件总面积的几倍,在多层布线中尤为突出。

CMOS反相器版图流程(4)

N+ implant

4. 有源区注入——P+,N+区(select)。

27

第27页/共38页

CMOS反相器版图流程(4)

P+ implant

4. 有源区注入——P+、N+区(select)。

28

第28页/共38页

CMOS反相器版图流程(5)

contact

5. 接触孔——多晶硅,注入区和金属线1接触端子。

(5)负载能力强。

CMOS电路可以带50个同类门以上。

(6)逻辑摆幅大。(第8低页/电共3平8页0V,高电平VDD )

8

2.CMOS门电路

1 A、B有高电平, 则驱动管导通、 负载管截止,输 出为低电平。

截止

负载管串联 (串联开关)

0

驱动管并联 (并联开关)

导通

第9页/共C3M8页OS或非门

9

当输入全为低电平,

第18页/共38页

4)、CMOS电路版图设计对布线和接触孔的特殊要求

(1)为抑制Latch up,要特别注意合理布置电源接触孔和VDD引线,减 小横向电流密度和横向电阻RS、RW。 • 采用接衬底的环行VDD布线。 • 增多VDD、VSS接触孔,加大接触面积,增加连线牢固性。 • 对每一个VDD孔,在相邻阱中配以对应的VSS接触孔,以增加并行电流通 路。

CMOS管

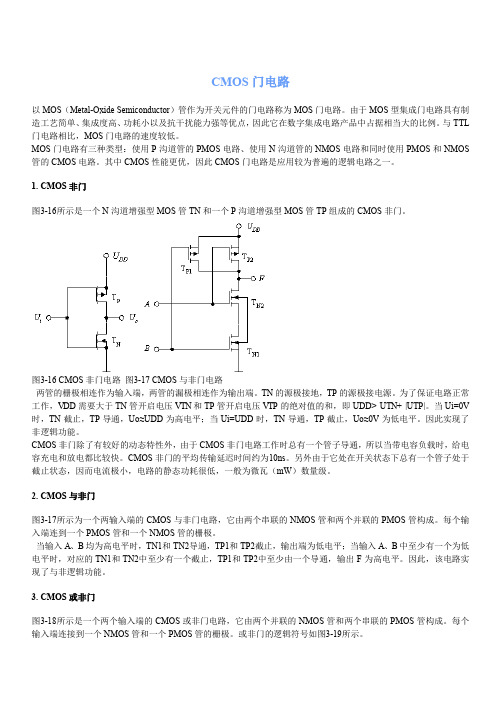

CMOS门电路以MOS(Metal-Oxide Semiconductor)管作为开关元件的门电路称为MOS门电路。

由于MOS型集成门电路具有制造工艺简单、集成度高、功耗小以及抗干扰能力强等优点,因此它在数字集成电路产品中占据相当大的比例。

与TTL 门电路相比,MOS门电路的速度较低。

MOS门电路有三种类型:使用P沟道管的PMOS电路、使用N沟道管的NMOS电路和同时使用PMOS和NMOS 管的CMOS电路。

其中CMOS性能更优,因此CMOS门电路是应用较为普遍的逻辑电路之一。

1. CMOS非门图3-16所示是一个N沟道增强型MOS管TN和一个P沟道增强型MOS管TP组成的CMOS非门。

图3-16 CMOS非门电路图3-17 CMOS与非门电路两管的栅极相连作为输入端,两管的漏极相连作为输出端。

TN的源极接地,TP的源极接电源。

为了保证电路正常工作,VDD需要大于TN管开启电压VTN和TP管开启电压VTP的绝对值的和,即UDD> UTN+ |UTP|。

当Ui=0V 时,TN截止,TP导通,Uo≈UDD为高电平;当Ui=UDD时,TN导通,TP截止,Uo≈0V为低电平。

因此实现了非逻辑功能。

CMOS非门除了有较好的动态特性外,由于CMOS非门电路工作时总有一个管子导通,所以当带电容负载时,给电容充电和放电都比较快。

CMOS非门的平均传输延迟时间约为10ns。

另外由于它处在开关状态下总有一个管子处于截止状态,因而电流极小,电路的静态功耗很低,一般为微瓦(mW)数量级。

2. CMOS与非门图3-17所示为一个两输入端的CMOS与非门电路,它由两个串联的NMOS管和两个并联的PMOS管构成。

每个输入端连到一个PMOS管和一个NMOS管的栅极。

当输入A、B均为高电平时,TN1和TN2导通,TP1和TP2截止,输出端为低电平;当输入A、B中至少有一个为低电平时,对应的TN1和TN2中至少有一个截止,TP1和TP2中至少由一个导通,输出F为高电平。

CMOS工艺流程与MOS电路版图举例

N-diffusion Polysilicon

p-sub

Metal

contact

74

Layout and Cross-Section View of Inverter

Inverter

VDD

In

In

Out

Out

GND 图例

Legend of each layer

N-well P-diffusion N-diffusion Polysilicon

– 反应离子刻蚀,形成第二层金属互连图形

52

合金 形成钝化层

– 在低温条件下(小于300℃)淀积氮化硅 – 光刻11,钝化版 – 刻蚀氮化硅,形成钝化图形

测试、封装,完成集成电路的制造工艺

CMOS集成电路采用(100)晶向的硅材料

53

4) 图解双阱硅栅 CMOS制作流程

54

首先进行表面清洗,去除wafer 表面的保护层和 杂质,三氧化二铝 必须以高速粒子撞击,并 用化学溶 液进行清洗。

61

在表面重新氧化生成二氧化硅层, LPCVD沉积 氮化硅层,以光阻定出下一 步的field oxide区域。

62

在上述多晶硅层外围,氧化二氧化 硅层以作为保护。涂布光阻,以便利用 光刻技术进行下一步的工序。

63

形成NMOS,以砷离子进行植入形成源漏 极。 此工序在约1000℃中完成,不能采用铝栅 极工艺,因铝不能耐高温,此工艺也称为自对 准工艺。砷离子的植入也降低了多晶硅的电阻 率(块约为30欧姆)。还采用在多晶硅上沉积高 熔点金属材料的硅化物(MoSi2、WSi2、TiSi2等), 形成多层结构

Cross-Section

79

N+ and P+ Regions

CMOS-两级运算放大器

3.2 仿真结果与分析图3基本电路图3.2.1直流仿真:DC仿真、静态工作点、输出电压摆幅、失调电压图 4 DC仿真电路图图5 DC仿真结果分析:如图所示输入级放大电路由M1~M5 组成。

M1 和M2 组成PMOS 差分输入对,差分输入与单端输入相比可以有效抑制共模信号干扰;M3、M4 电流镜为有源负载;M5 为第一级提供恒定偏置电流。

输出级放大电路由M6、M7 组成。

M6 为共源放大器,M7 为其提供恒定偏置电流同时作为第二级输出负载。

相位补偿电路由M14 和Cc 构成。

M14 工作在线性区,可等效为一个电阻,与电容Cc 一起跨接在第二级输入输出之间,构成RC 密勒补偿。

M3 和M4 为第一级负载,将差模电流恢复为差模电压。

M6 为第二级跨导级,将差分电压信号转换为电流,而M7 再将此电流信号转换为电压输出。

由图知各个器件在静态工作点均工作在饱和区,M14工作于线性区。

图6输出电压摆幅电路图图7输出电压摆幅仿真结果图分析:输出动态范围即输出摆幅,是所有晶体管都工作在饱和区时的输出电压的范围。

如果输出电压过低,M6工作在线性区,如果输出电压过高,M7 工作在线性区。

所以输出摆幅范围是V GST6≤V OUT≤V DD-V GST7。

一旦输出电压超过输出摆幅,某一个MOS 管就会进入线性区,输出阻抗降低,增益也就会下降。

降低过驱动电压可以拓展输出摆幅。

注意,如果仅仅是容性负载,输出电压可以达到电源电压和地,但此时增益严重下降,失真已经出现。

如果有阻性负载(接地),输出电压是无论如何都到达不了电源电压的。

由图可知输出电压摆幅为0.27V≤V OUT≤2.97V。

图8失调电压电路图图9失调电压仿真结果图分析: 对于差分输入、单端输出的运放,为最大化输出摆幅,输出电压共模点取在输出摆幅的一半处,即(V DD-V GST7+V GST6)/2,如果M6和M7过驱动电压相同,那么输出电压共模点取在V DD/2 处。

MOS电路版图举例

掩膜版 氮化硅

光刻2,刻有源区掩膜版

N阱

9

去除氮化硅

光刻3,刻多晶硅掩膜版

FOX N阱

10

重新生长二氧化硅(栅氧)

场氧

光刻3,刻多晶硅掩膜版

栅氧

N阱

11

生长多晶硅

多晶硅 N阱

光刻3,刻多晶硅掩膜版

12

刻蚀多晶硅

掩膜版

光刻3,刻多晶硅掩膜版

N阱

13

刻蚀多晶硅

多晶硅 N阱

光刻3,刻多晶硅掩膜版

CMOS工艺流程与MOS电路版图举例

1. CMOS工艺流程 1) 简化N阱CMOS工艺演示flash 2) 清华工艺录像:N阱硅栅CMOS工艺流程 3) 双阱CMOS集成电路的工艺设计 4) 图解双阱硅栅CMOS制作流程 2. 典型N阱CMOS工艺的剖面图 3. Simplified CMOS Process Flow 4. MOS电路版图举例

1

1) 简化N阱CMOS 工艺演示

2

氧化层生长

氧化层 P-SUB

光刻1,刻N阱掩膜版

3

掩膜版

曝光

光刻胶 光刻1,刻N阱掩膜版

4

氧化层的刻蚀

光刻1,刻N阱掩膜版

5

N阱注入

光刻1,刻N阱掩膜版

6

形成N阱

N阱 P-SUB

7

氮化硅的刻蚀

二氧化硅

掩膜版

N阱

光刻2,刻有源区掩膜版

8

场氧的生长

二氧化硅

14

P+离子注入

P+

掩膜版

光刻4,刻P+离子注入掩膜版

N阱

15

N+离子注入

N+ 光刻5,刻N+离子注入掩膜版

CMOS工艺器件结构

Nmos 版图

Nmos 剖面图

一、MOSFET

NMOS_NA 版图和结构

Nmos _na版图

Nmos_na 剖面图

一、MOSFET

NMOS_dnw 版图和结构

Nmos_dnw 版图

Nmos_dnw 剖面图

一、MOSFET

PMOSFET 版图和结构

Pmos 版图

Pmos 剖面图

二、RESISTOR

Poly resistor 版图和结 构

Poly resistor 版图

Poly resistor 剖面图

二、RESISTOR

nwell resistor 版图和 结构

nwell resistor 版图

nwell resistor 剖面图

二、RESISTOR

Others resistor版图和结构

普通poly resistor 版图

扩散电阻版图

三、CAPACITANCE

MIM版图和结构

MIM cap 版图

三、CAPACITANCE

MOM版图和结构

MOM cap 版图

三、CAPACITANCE

VARACTOR版图和结构

VAR cap 版图

VAR cap 剖面图

三、CAPACITANCE

INDUCTOR版图和结构 目前基本能用到的都是metal做的inductor, 务必选用PDK中cell,切勿修改。

INDUCTOR版图

谢谢!

mosfethvmosfethvpmospmosnmosnmosnmosdnwnmosdnwnmosnativenmosnativeresistorresistorcapacitancecapacitancediodediodebipolarbipolarinductorinductornmos版图nmos剖面图nmosfet版图和结构nmosna版图nmosna剖面图nmosna版图和结构nmosdnw版图nmosdnwnmosdnw版图和结构pmos版图pmos剖面图pmosfet版图和结构polyresistor版图polyresistorpolyresistor版图和结构nwellresistor版图nwellresistornwellresistor版图和结构普通polyresistorothersresistor版图和结构mimcap版图mim版图和结构momcap版图mom版图和结构varcap版图varactor版图和结构varcap剖面mos管做电容示意图moscap版图和结构diode版图psdnwell版图和结diode剖面图diode版图psdnwell版图和结diode剖面图横向bjtpnp版图和结构diode版图及对应剖面图inductor版图和结inductor版图目前基本能用到的都是metal做的inductor务必选用pdk中cell切勿修改

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

112 BIT ACCUMULATOR FOR DDS ECE547 Final Report Aravind Reghu Spring, 2006 2

CONTENTS 1 Introduction 6 1.1 Project Overview 6 1.1.1 How it Works 6 1.2 Objective 8 2 Circuit Design 9 2.1 Design Objective 9 2.2.1 Problem Statement 9 2.2.2 Design Specification 9 2.2.3 Pipelining 10 2.2.4 Basic CMOS Gate Sizing 10 2.2.5 Basic Logic Circuit 11 2.2.5.1 Inverter 11 2.2.5.2 2-Input NOR gate 12 2.2.5.3 2-Input NAND gate 13 2.2.5.4 2-Input AND gate 14 2.2.5.5 2-Input OR gate 14 2.2.5.6 2-Input XOR gate 15 2.2.5.7 D Flip Flop 15 2.2.5.8 Full Adder 16 2.2.6 4 Bit Accumulator 17 2.2.7 12 Bit Accumulator 18 3 Simulation Result 21 3.1 Simulation Result for 4 Bit Accumulator 21 3.2 Simulation result for 12 bit Accumulator 22 4 Layout and Extracted view 24 4.1 Inverter 24 4.2 2-Input NOR Gate 25 4.3 2-Input NAND Gate 27 4.4 2-Input AND Gate 29 4.5 2-Input OR Gate 32 4.6 2-Input XOR Gate 34 4.7 D Flip Flop 35 4.8 Full Adder 37 4.9 Accumulator 38 4.9.a 4 Bit Accumulator 38 4.9.b 12 Bit Accumulator 40 5 Power Dissipation 42 6 DDS Chip 44 6.1 Design Limitations 44 6.1.1 Chip Size 44 6.1.2 IO Pins 44 7 Verification 46 7.1 Output Waveform 46 8 Conclusion 47 9 Bibliography 48 3

Appendix A 49 Appendix B 50 4 List of Figures

Fig 1. Block Diagram of a Basic Direct Digital Synthesizer (DDS)7 Fig 2. Operation of the phase accumulator in a direct digital synthesizer8

Fig 3. Device sizing for CMOS NAND gate

11

Fig 4. Schematic of a CMOS INVERTER12 Fig 5. Schematic of a 2-input NOR gate12 Fig 6. Schematic of a 2-input NAND gate13 Fig 7. Schematic of a 2-input AND gate14 Fig 8. Schematic of a 2-input OR gate14 Fig 9. Schematic of a 2-input XOR gate15 Fig 10. D flip flop operation16 Fig 11. Schematic of a rising edge D flip flop16 Fig 12. Schematic of a Full Adder17 Fig 13. Schematic of 4 Bit Accumulator18 Fig 14. Schematic of 12 Bit Accumulator19 Fig 15. Accumulation Cycle20 Fig 16. Testing of 4 Bit Accumulator21 Fig 17. Output waveform of 4 Bit Accumulator22 Fig 18. Testing of 12 Bit Accumulator23 Fig 19. Output Waveform of 12 Bit Accumulator23 Fig 20. Layout of Inverter 24 Fig 21. Extracted View Of Inverter 25 Fig 22. Layout of 2 input NOR gate 26 Fig 23.Extracted view of 2 input NOR gate 28 Fig 24.Layout of 2 Input NAND Gate 29 Fig 25.Extracted view of 2 input NAND gate 29 Fig 26. Layout of 2 input AND gate 30 Fig 27. Extracted view of 2 input AND gate 31 Fig 28. Layout of 2 input OR gate 32 Fig 29. Extracted view of 2 input OR gate 33 Fig 30. Layout of 2 input XOR gate 34 Fig 31. Extracted view of 2 input XOR gate 35 Fig 32. Layout of D flip flop 36 Fig 33. Extracted view of D flip flop 36 Fig 34. Layout of Full Adder 37 Fig 35. Extracted view of Full Adder 37 Fig 36. Layout of 4 Bit Accumulator 38 Fig 37.Extracted view of 4 Bit Accumulator 39 Fig 38. Layout of 12 Bit Accumulator 40 Fig 39. Extracted view of 12 Bit Accumulator 41 5

Fig 40. Schematic of the DDS Chip 44 Fig 41. Layout of the DDS Chip 45 Fig 42. Output Waveform of the DDS Chip 46 6Chapter 1

Introduction

1.1 Project Overview Direct digital synthesis (DDS) is a powerful technique used in the generation of radio frequency signals for use in a variety of applications from radio receivers to signals generators and many more. The technique has become far more widespread in recent years with the advances being made in integrated circuit technology that allow much faster speeds to be handled which in turn enable higher frequency DDS chips to be made.

Direct digital synthesis (DDS) is a powerful technique used in the generation of radio frequency signals for use in a variety of applications from radio receivers to signals generators and many more. The technique has become far more widespread in recent years with the advances being made in integrated circuit technology that allow much faster speeds to be handled which in turn enable higher frequency DDS chips to be made.

1.1.1 How It Works As the name suggests this form of synthesis generates the waveform directly using digital techniques. This is different to the way in which the more familiar indirect synthesizers that use a phase locked loop as the basis of their operation.

A direct digital synthesizer operates by storing the points of a waveform in digital format, and then recalling them to generate the waveform. The rate at which the synthesizer completes one waveform then governs the frequency. The overall block diagram is shown below, but before looking at the details operation of the synthesizer it is necessary to look at the basic concept behind the system.