第2章集成电路中的晶体管及其寄生效应(半导体集成电路共14章)

半导体集成电路课后答案

半导体集成电路课后答案《现代半导体集成电路》全面介绍了现代半导体集成电路的根底知识、分析与设计方法。

以下是由关于半导体集成电路的课后答案,希望大家喜欢!一,集成电路的根本制造工艺二,集成电路中的晶体管及其寄生效应三,集成电路中的无源元件四,晶体管-晶体管逻辑电路五,发射极耦合逻辑电路六,集成注入逻辑电路七,MOS反相器八,MOS根本逻辑单元九,MOS逻辑功能部件十,存储器十一,接口电路十二,模拟集成电路中的根本单元电路十三,集成运算放大器十四,MOS开关电容电路十五,集成稳压器十六,D/A,A/D变换器十七,集成电路设计概述十八,集成电路的正向设计十九,集成电路的芯片解剖二十,集成电路设计方法二十一,集成电路的可靠性和可测性设计简介二十二,集成电路的计算机辅助设计简介1 电路的关态-指电路的输出管处于截止工作状态时的电路状态,此时在输出端可得到 VO=VOH,电路输出高电平。

2 电路的开态-指电路的输出管处于饱和工作状态时的电路状态,此时在输出端可得到 VO=VOL,电路输出低电平。

3 电路的电压传输特性-指电路的输出电压VO随输入电压Vi变化而变化的性质或关系(可用曲线表示,与晶体管电压传输特性相似)。

4 输出高电平VOH-与非门电路输入端中至少一个接低电平时的输出电平。

5 输出低电平VOL-与非门电路输入端全部接高电平时的输出电平。

6 开门电平VIHmin-为保证输出为额定低电平时的最小输入高电平(VON)。

7 关门电平VILmax-为保证输出为额定高电平时的最大输入低电平(VOFF)。

8 逻辑摆幅VL-输出电平的最大变化区间,VL=VOH-VOL。

9 过渡区宽度VW-输出不确定区域(非静态区域)宽度,VW=VIHmin-VILmax。

10 低电平噪声容限VNML-输入低电平时,所容许的最大噪声电压。

其表达式为 VNML=VILmax-VILmin=VILmax- VOL(实用电路)。

11高电平噪声容限VNMH-输入高电平时,所容许的最大噪声电压。

第2章晶体管答案

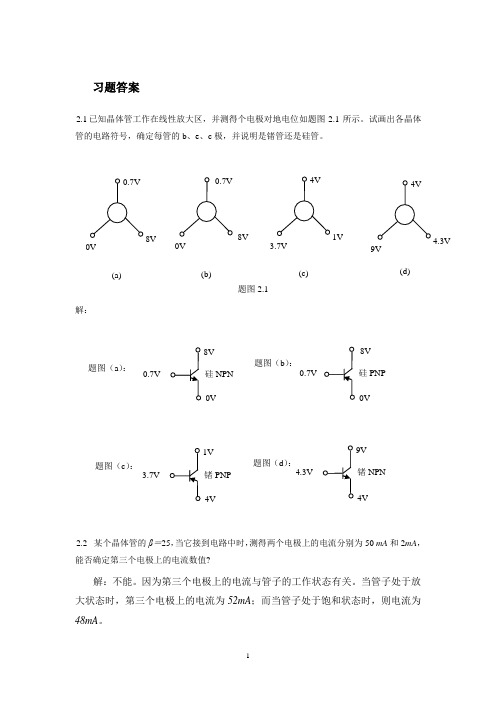

习题答案2.1 已知晶体管工作在线性放大区,并测得个电极对地电位如题图2.1所示。

试画出各晶体管的电路符号,确定每管的b 、e 、c 极,并说明是锗管还是硅管。

解:2.2 某个晶体管的β=25,当它接到电路中时,测得两个电极上的电流分别为50 mA 和2mA ,能否确定第三个电极上的电流数值?解:不能。

因为第三个电极上的电流与管子的工作状态有关。

当管子处于放大状态时,第三个电极上的电流为52mA ;而当管子处于饱和状态时,则电流为48mA 。

8V0V0.7V硅NPN -8V 0V-0.7V硅PNP 1V4V3.7V锗PNP 9V 4.3V锗NPN 4V题图(a ):题图(b ):题图(c ):题图(d ):8V0V(a)-8V0V(b)1V3.7V(c)4.3V9V(d)题图2.12.3 已测得晶体管电极管各电极对地电位如题图2.3所示,试判别各晶体管的工作状态(放大、饱和、截止或损坏)。

解:题图(a )3AX 为PNP 锗管,30.U BE -=V (正偏),74.U CE -=V (反偏),放大状态题图(b ):e 结反偏,c 结反偏,截止状态 题图(c ):e 结正偏,c 结正偏,饱和状态 题图(d ):e 结开路,晶体管损坏2.4 PN N +型晶体管基区的少数载流子的浓度分布曲线如题图2.4所示,其中n b 0表示平衡时自由电子的浓度。

(1)说明每种浓度分布曲线所对应的发射结和集电结的偏置状态。

(2)说明每种浓度分布曲线所对应的晶体管的工作状态。

-0.3V0V (a)12V0V(d)3DG8 6.3V7V (c)8V3V(b) 3BX1 题图2.3解:(1)对于PN N +晶体管,当发射结(集电结)正偏时,由于从发射区(集电区)向基区注入了非平衡少子电子,所以)(01x x x ==处P 区边界上少子电子的浓度大于平衡的电子浓度0b n ,当发射结(集电结)反偏时,在阻挡层两侧边界上的少子浓度趋向于零。

《半导体集成电路》期末考试试题库..

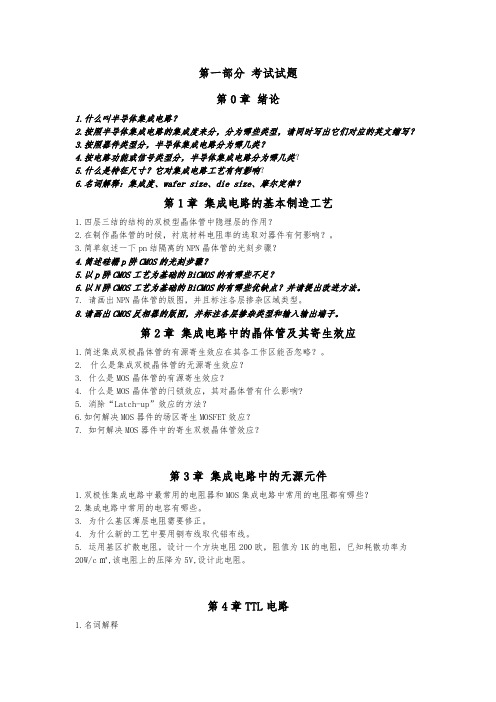

第一部分考试试题第0章绪论1.什么叫半导体集成电路?2.按照半导体集成电路的集成度来分,分为哪些类型,请同时写出它们对应的英文缩写?3.按照器件类型分,半导体集成电路分为哪几类?4.按电路功能或信号类型分,半导体集成电路分为哪几类?5.什么是特征尺寸?它对集成电路工艺有何影响?6.名词解释:集成度、wafer size、die size、摩尔定律?第1章集成电路的基本制造工艺1.四层三结的结构的双极型晶体管中隐埋层的作用?2.在制作晶体管的时候,衬底材料电阻率的选取对器件有何影响?。

3.简单叙述一下pn结隔离的NPN晶体管的光刻步骤?4.简述硅栅p阱CMOS的光刻步骤?5.以p阱CMOS工艺为基础的BiCMOS的有哪些不足?6.以N阱CMOS工艺为基础的BiCMOS的有哪些优缺点?并请提出改进方法。

7. 请画出NPN晶体管的版图,并且标注各层掺杂区域类型。

8.请画出CMOS反相器的版图,并标注各层掺杂类型和输入输出端子。

第2章集成电路中的晶体管及其寄生效应1.简述集成双极晶体管的有源寄生效应在其各工作区能否忽略?。

2.什么是集成双极晶体管的无源寄生效应?3. 什么是MOS晶体管的有源寄生效应?4. 什么是MOS晶体管的闩锁效应,其对晶体管有什么影响?5. 消除“Latch-up”效应的方法?6.如何解决MOS器件的场区寄生MOSFET效应?7. 如何解决MOS器件中的寄生双极晶体管效应?第3章集成电路中的无源元件1.双极性集成电路中最常用的电阻器和MOS集成电路中常用的电阻都有哪些?2.集成电路中常用的电容有哪些。

3. 为什么基区薄层电阻需要修正。

4. 为什么新的工艺中要用铜布线取代铝布线。

5. 运用基区扩散电阻,设计一个方块电阻200欧,阻值为1K的电阻,已知耗散功率为20W/c㎡,该电阻上的压降为5V,设计此电阻。

第4章TTL电路1.名词解释电压传输特性开门/关门电平逻辑摆幅过渡区宽度输入短路电流输入漏电流静态功耗瞬态延迟时间瞬态存储时间瞬态上升时间瞬态下降时间瞬时导通时间2. 分析四管标准TTL与非门(稳态时)各管的工作状态?3. 在四管标准与非门中,那个管子会对瞬态特性影响最大,并分析原因以及带来那些困难。

第二章-晶体管

(1)共基直流放大系数 IC

IE

(2)共基交流放大系数

IC

I E

由于ICBO、ICEO 很小,因此 在以后的计算中,不必区分。

二、极间反向电流

1 ICBO

发射极开路时,集电极—基极间的反向电流,称为集 电极反向饱和电流。

2 ICEO

基极开路时,集电极—发射极间的反向电流,称为集 电极穿透电流。

T

( 0.5 ~ 1) / C

2.3.2 晶体管的主要参数 一、电流放大系数

1.共射电流放大系数

(1) 共射直流放大系数 反映静态时集电极电流与基极电流之比。

(2) 共射交流放大系数 反映动态时的电流放大特性。

由于ICBO、ICEO 很小,因此 在以后的计算中,不必区分。

2. 共基电流放大系数

a. 受控特性:iC 受iB的控制

uCE=uBE 4

放

IB=40μ A

iC iB

饱 和3

30μ A

区

大 20μ A

iC iB

2

区

10μ A

1

b. 恒流特性:当 iB 恒定时,

0

uCE 变化对 iC 的影响很小

0μ A iB=-ICBO

5

10

15

uCE/V

截止区

即iC主要由iB决定,与输出环路的外电路无关。

iC主要由uCE决定 uCE ↑→ iC ↑

iC /mA

=80μA =60μA =40μA

=20μA

25℃

uCE /V

(3)当uCE增加到使集电结反偏电压较大时,运动 到集电结的电子基本上都可以被集电区收集,

此后uCE再增加,电流也没有明显得增加,特 性曲线几乎平行于与uCE轴

第二章MOS晶体管

集成电路的测试与可测性设计 集成电路设计软件介绍 总计

2学时 6学时 36学时

参考文献

[1] 王志功,景为平,孙玲.集成电路设计技术与工具. 南京: 东南大学出版社,2007年7月(国家级规划教材).

[2](美)R.Jacob Baker, Harry W. Li, David E. Boyce. CMOS Circuit Design, Layout and Simulation. 北京: 机械工业出版社,2006.

社,2004年5月(21世纪高等学校电子信息类教材).

第二章 MOS晶体管

一、MOSFET的结构 MOS 晶 体 管 是 一 种 场 效 应 管 ( 英 文 全 称 为 Metal-

Oxide-Silicon Field Effect Transistor),它是电压控制 电流器件,既可以用于模拟电路,也可以用于数字电路。 在模拟电路中,由于MOS晶体管具有很高的输入阻抗,从 而可提高它作为电压放大器的性能。而在数字电路中, MOS 晶 体 管 广 泛 用 作 基 本 存 储 器 件 或 逻 辑 器 件 。 可 以 说 MOS晶体管是MOS管集成电路的主要器件。

集成电路设计导论

梁竹关

云南大学信息学院电子工程系

第一部分 理论课

第一章 绪言

1.1 集成电路的发展 1.2 集成电路分类 1.3 集成电路设计 第二章 MOS晶体管 2.1 MOS晶体管结构 2.2 MOS晶体管工作原理 2.3 MOS晶体管的电流电压关系 2.4 MOS晶体管主要特性参数 2.5 MOS晶体管的SPICE模型 第三章 MOS管反相器 3.1 引言 3.2 NMOS管反相器 3.3 CMOS反相器 3.4 动态反相器 3.5 延迟 3.6 功耗

半导体集成电路考试题目与参考答案

第一部分考试试题第0章绪论1.什么叫半导体集成电路?2.按照半导体集成电路的集成度来分,分为哪些类型,请同时写出它们对应的英文缩写?3.按照器件类型分,半导体集成电路分为哪几类?4.按电路功能或信号类型分,半导体集成电路分为哪几类?5.什么是特征尺寸?它对集成电路工艺有何影响?6.名词解释:集成度、wafer size、die size、摩尔定律?第1章集成电路的基本制造工艺1.四层三结的结构的双极型晶体管中隐埋层的作用?2.在制作晶体管的时候,衬底材料电阻率的选取对器件有何影响?。

3.简单叙述一下pn结隔离的NPN晶体管的光刻步骤?4.简述硅栅p阱CMOS的光刻步骤?5.以p阱CMOS工艺为基础的BiCMOS的有哪些不足?6.以N阱CMOS工艺为基础的BiCMOS的有哪些优缺点?并请提出改进方法。

7. 请画出NPN晶体管的版图,并且标注各层掺杂区域类型。

8.请画出CMOS反相器的版图,并标注各层掺杂类型和输入输出端子。

第2章集成电路中的晶体管及其寄生效应1.简述集成双极晶体管的有源寄生效应在其各工作区能否忽略?。

2.什么是集成双极晶体管的无源寄生效应?3. 什么是MOS晶体管的有源寄生效应?4. 什么是MOS晶体管的闩锁效应,其对晶体管有什么影响?5. 消除“Latch-up”效应的方法?6.如何解决MOS器件的场区寄生MOSFET效应?7. 如何解决MOS器件中的寄生双极晶体管效应?第3章集成电路中的无源元件1.双极性集成电路中最常用的电阻器和MOS集成电路中常用的电阻都有哪些?2.集成电路中常用的电容有哪些。

3. 为什么基区薄层电阻需要修正。

4. 为什么新的工艺中要用铜布线取代铝布线。

5. 运用基区扩散电阻,设计一个方块电阻200欧,阻值为1K的电阻,已知耗散功率为20W/c㎡,该电阻上的压降为5V,设计此电阻。

第4章TTL电路1.名词解释电压传输特性 开门/关门电平 逻辑摆幅 过渡区宽度 输入短路电流 输入漏电流静态功耗 瞬态延迟时间 瞬态存储时间 瞬态上升时间 瞬态下降时间瞬时导通时间2. 分析四管标准TTL 与非门(稳态时)各管的工作状态?3. 在四管标准与非门中,那个管子会对瞬态特性影响最大,并分析原因以及带来那些困难。

集成电路试题库

集成电路试题库(总49页) -本页仅作为预览文档封面,使用时请删除本页-半导体集成电路典型试题绪论1、什么叫半导体集成电路?【答案:】通过一系列的加工工艺,将晶体管,二极管等有源器件和电阻,电容等无源元件,按一定电路互连。

集成在一块半导体基片上。

封装在一个外壳内,执行特定的电路或系统功能。

2、按照半导体集成电路的集成度来分,分为哪些类型,请同时写出它们对应的英文缩写【答案:】小规模集成电路(SSI),中规模集成电路(MSI),大规模集成电路(VSI),超大规模集成电路(VLSI),特大规模集成电路(ULSI),巨大规模集成电路(GSI)3、按照器件类型分,半导体集成电路分为哪几类?【答案:】双极型(BJT)集成电路,单极型(MOS)集成电路,Bi-CMOS型集成电路。

4、按电路功能或信号类型分,半导体集成电路分为哪几类?【答案:】数字集成电路,模拟集成电路,数模混合集成电路。

5、什么是特征尺寸它对集成电路工艺有何影响【答案:】集成电路中半导体器件的最小尺寸如MOSFET的最小沟道长度。

是衡量集成电路加工和设计水平的重要标志。

它的减小使得芯片集成度的直接提高。

6、名词解释:集成度、wafer size、die size、摩尔定律?【答案:】7、分析下面的电路,指出它完成的逻辑功能,说明它和一般动态组合逻辑电路的不同,分析它的工作原理。

【答案:】该电路可以完成NAND逻辑。

与一般动态组合逻辑电路相比,它增加了一个MOS管M kp,它可以解决一般动态组合逻辑电路存在的电荷分配的问题。

对于一般的动态组合逻辑电路,在评估阶段,A=“H” B=“L”, 电荷被OUT处和A处的电荷分配,整体的阈值下降,可能导致OUT的输出错误。

该电路增加了一个MOS管M kp,在预充电阶段,M kp导通,对C点充电到V dd。

在评估阶段,M kp截至,不影响电路的正常输出。

8、延迟时间【答案:】时钟沿与输出端之间的延迟第1章集成电路的基本制造工艺1、四层三结的结构的双极型晶体管中隐埋层的作用【答案:】减小集电极串联电阻,减小寄生PNP管的影响2、在制作晶体管的时候,衬底材料电阻率的选取对器件有何影响【答案:】电阻率过大将增大集电极串联电阻,扩大饱和压降,若过小耐压低,结电容增大,且外延时下推大3、简单叙述一下pn结隔离的NPN晶体管的光刻步骤【答案:】第一次光刻:N+隐埋层扩散孔光刻第二次光刻:P隔离扩散孔光刻第三次光刻:P型基区扩散孔光刻第四次光刻:N+发射区扩散孔光刻第五次光刻:引线孔光刻第六次光刻:反刻铝4、简述硅栅p阱CMOS的光刻步骤【答案:】P阱光刻,光刻有源区,光刻多晶硅,P+区光刻,N+区光刻,光刻接触孔,光刻铝线5、以p阱CMOS工艺为基础的BiCMOS的有哪些不足【答案:】NPN晶体管电流增益小,集电极串联电阻大,NPN管的C极只能接固定电位6、以N阱CMOS工艺为基础的BiCMOS的有哪些优缺点?并请提出改进方法【答案:】首先NPN具有较薄的基区,提高了其性能:N阱使得NPN管C极与衬底断开,可根据电路需要接任意电位。

第二章 双极型逻辑集成电路解读

当VCE增加时,由于基区宽度减小,注入到基区中的少 数载流子的复合减少,故IB减少

共基极

在同样的VBE下,VCE越大,IE越大

三极管伏安特性

反向工作特性

IB=0 Cut-off

正向工作特性

三极管工作状态总结

工作状态 正向活跃状态 反向活跃状态

关闭状态 饱和状态

三极管放大电路

发射结 正偏 反偏 反偏 正偏

0

R 1R

1SF

SF

0

SR 1 RS

1

I ES ICE I SS

eVBE Vt eVBC Vt eVSC Vt

1 1 1

NPN正向工作区和截止区的情况

( VBC

反向工作区

减小集电极电阻

形成基区减速场

(2)集成双极晶体管的无源寄生效应

实际的集成晶体管中还存在着电荷储存效应和从晶 体管有效基区到晶体管个引出端之间的欧姆体电阻。 它们对晶体管的工作产生影响,称为无源寄生效应。

寄生电阻:res、rcs、rb和寄生电容CJ、CD:

集成双极晶体管电路中的寄生电阻大于分立器件 集成双极晶体管电路中的寄生电容大于MOS器件

集成晶体管逻辑电路发展状况

从直接耦合晶体管逻辑(DCTL)、RTL、DTL 广泛应用饱和型逻辑集成电路:TTL STTL和LSTTL以及ASTTL和ALSTTL 继承注入逻辑(I2L) 发射极耦合(ECL)电路—非饱和逻辑集成电路

以TI公司60~70年代末推出54/74系列TTL电路为例子 54 —— 军用 74 —— 民用

rCS=rC1+rC2+rC3 rCS是一个被隔离区势垒电容旁路的分布电阻 在大信号工作情况下发生发射极电流的集边效应,使

[工学]半导体集成电路第1章_OK

9

• 3、典型的TTL工艺过程

10

§1-2:IC中的晶体管及其有源 寄生效应

• 从前面的分析可知,IC中的晶体管是 一个四层三结结构。存在有源寄生效应。 准确地分析其特性需处理大量的非线性问 题,非常困难,因此我们假定器件为一维 结构,并引入大量的近似讨论其直流特性。 为此我们从简单的PN结入手。引出埃伯斯摩尔模型(Ebers-Moll)

此时:

P型基区内电子寿命 n ~ 8.51010 S • N型基区内空穴寿命 p ~ 51010 S

n p

2

• 因此掺金后,尽量Au可能扩散至整个 芯片内,但NPN管的β值仍可控制在数字电 路晶体的合理范围内 β=15 ~30

34

§1-3:IC中晶体管的无源寄生效应

•

四层三结结构晶体管E-M模型描述了有源寄

此时:VBE>0 ,VBC <0, VSC <0寄生晶体管截 止,对NPN管基本无影响。

IE 1

I

B

1

F

IC IS

F

0

R 1R 1 SF SF

0

SR 1 SR

1

VBE

I ES e VT I CS I SS

• 与普通NPN管比较,仅增加了IB、IC的反向漏电流, 同时增加了一项衬底电流,电路功耗增加。

• 首先:加大了寄生PNP管的基区宽度,从这一 点考虑埋层必须有足够大的区域(超过npn管基区)

• 其次:增加了NPN管基区浓度,减小了注入效 率

• 第三:埋层杂质上推,杂质电离后,成为具有 一定分布的电离中心,这一电离中心的分布形成

一个向上的电场,阻碍PNP管基区内少子的运动。

第二章晶体管-PPT课件

例题

1、由电极电位判断三极管的工作状态。

在电路中,测得下述6组三极管三个极的电位: c 1)NPN管:(1) 1V (2) 0.3V (3) 2V (2) e~0.3V (3) e~2V c~0.7V c~5V 0.3V 0.7V 5V 3V 1V 1V

b e

解: (1) b~1V;e~ 0.3V ;c~ 3V (硅管,放大)

特点

6

9

iC(mA )

4

3 2 1 3 6 9

此区域中 : 100A IB=0, IC=ICEO, 80A UBE< 死区 60A 电压,称为 截止区。 40A

20A iB=0 12 vCE(V)

特点

输出特性三个工作区域的特点:

(1)放大区:发射结正偏,集电结反偏。

iC i B , 且 IC = IB 即:

(2) 饱和区:发射结正偏,集电结正偏。 即:VCEVBE , IB>IC,VCE0.3V (3) 截止区: VBE< 死区电压, IB=0 , IC=ICEO 0

输出特性

V V V A C E Q A r c e IC IC Q Q

2.1.3 温度对晶体管特性曲线的影响

T (C )

RC VC

VB

输出特性

vCE =0.5V

vCE=0V

iB(A)

80

60 40 死区电 20 压,硅管 0.5V,锗 管0.2V。

vCE 1V 工作压降: 硅管 UBE0.6~0.7V,锗管 UBE0.2~0.3V。

0.4

0.8

vBE(V)

输入特性

二、共射输出特性曲线

i (mA ) iC f (v )| C i = 常数 C E