USB3.0芯片CYUSB3014硬件设计指南

CYUSB3014开发板-用户手册(硬件)

目录

1.

介绍 ................................................................................................... 3

1.1 适用范围 .................................................................................3 1.2 开发板特征参数 .....................................................................3 1.3 开发板实物图 .........................................................................3

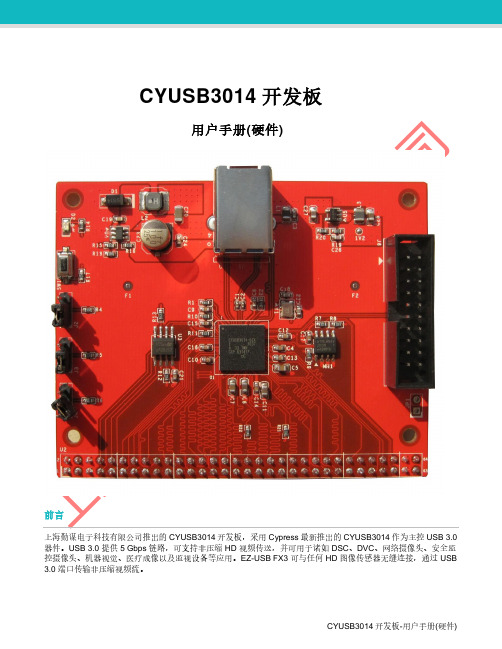

Figure 2-1. CYUSB3014 开发板实物图 下图是 CYUSB3014 开发板尺寸图:

Figure 2-2. CYUSB3014 开发板尺寸图

上海勤谋电子科技有限公司

CYUSB3014 开发板

硬件用户手册-V01

2.2 CYUSB3014 开发板原理图描述

2.2.1

CYUSB3014 开发板电源供电 默认情况下,开发板的供电 5V 由 USB 座提供,CYUSB3014 芯片工作需要的 3.3V 和 1.2V 由高效率 DC/DC 电 源供电,使用户设计扩展板时更方便,电源部分设计的原理图如下所示。板上有 3.3V 电源指示灯 D2,当板子正 确供电时,此 LED 会显示高亮。默认情况下,板子所有 BANK 的 IO 都是 3.3V 电平。

B1 VIO4

USB3.0设计资源 cypress芯片程序解读

CYPEESS USB3.0程序解读解读同步FIFO的一个例子。

生产者,消费者首先看DMA的回调函数:typedef void (*CyU3PDmaCallback_t) (CyU3PDmaChannel *handle, /* Handle to the DMA channel. */CyU3PDmaCbType_t type, /* The type of callback notification being generated. */ CyU3PDmaCBInput_t*input /* Union that contains data related to the notification. The input parameter will be a pointer to a CyU3PDmaBuffer_t variable in the cases where the callback type isCY_U3P_DMA_CB_RECV_CPLT or CY_U3P_DMA_CB_PROD_EVENT. */);根据其说明,解读如下:1.对每一个DMA通道,回调函数必须被注册。

如果没有注册或者相应的通知事件没有被注册,则回调函数不会被执行。

2.回调函数不能被阻塞。

即不能用SLEEP()之类的函数。

如果数据需要处理,必须在回调函数之外。

3.在生产者事件中,应用希望尽可能快地处理输入的数据。

如果缓冲的处理不能在规定的时间内完成,则输入的可能是陈旧的数据。

在自动信号通道中,输入参量指向最新的数据。

如果处理延时,生产者socket可能复盖部分数据。

4.在手动或手动IN通道模式时,输入参量指向第一个缓冲(用于去消费者socket).如果在第二次调用时,这个缓冲仍没有被处理,输入参量中将是被陈旧的数据。

如果数据处理必须在通道中做,CyU3PDmaChannelGetBuffer函数必须被应用,而回调函数必须作为一个通知。

基于CYUSB3014 USB3.0总线开发技术

基于CYUSB3014 USB3.0总线开发技术[导读]本文介绍了以FPGA为控制核心,以cypress的FX3系列CYUSB3014芯片为总线接口芯片,实现了对USB3.0总线技术的开发应用,实际测试的传输速度能够达到1.43Gbps。

1.引言USB(Universal Serial Bus,通用串行总线)以其无需配置、即插即用等特性获得了广泛的应用。

2004年提出的USB2.0标准,传输速度最大能够达到480Mbps。

但在 USB3.0标准中,它的最大传输速度几乎是传统USB2.0传输速度的10倍,达到了5.0Gbps,被定义为“超高速U S B接口”。

本文基于CYPRESS的FX3系列USB3.0芯片,对USB3.0总线进行研究开发。

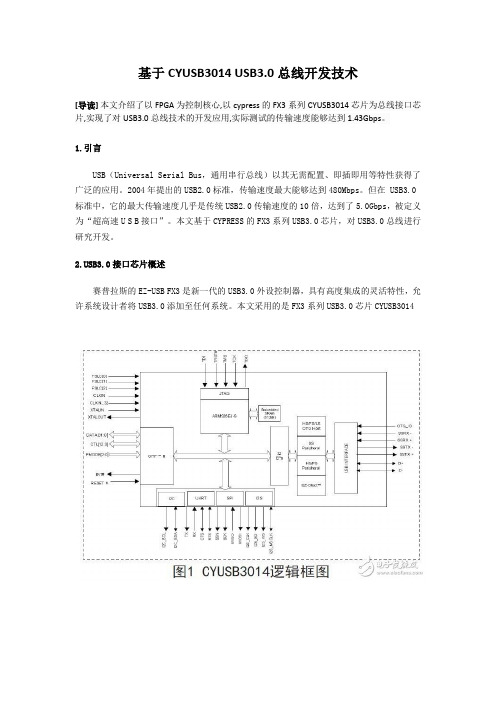

B3.0接口芯片概述赛普拉斯的EZ-USB FX3是新一代的USB3.0外设控制器,具有高度集成的灵活特性,允许系统设计者将USB3.0添加至任何系统。

本文采用的是FX3系列USB3.0芯片CYUSB3014FX3是完全兼容USB3.0 V1.0和USB2.0规范的,集成的USB2.0 OTG控制器允许芯片作为主从设备使用。

另外,它还支持一些常用的外设接口,如SPI,I2C,UART和I2S可以与外部设备进行通信。

FX3具有一个可进行完全配置的并行通用可编程接口GPIF II,它可以与任何处理器、ASIC或是FPGA连接。

它可以轻松无缝地连接至多种常用接口,比如异步SRAM、异步和同步地址数据复用式接口、并行 ATA等等。

EZ-USB FX3集成了USB3.0和USB2.0物理层(PHY)以及32位ARM926EJ-S微处理器,具有强大的数据处理能力,并可用于构建定制应用。

3.系统整体设计本系统设计主要由软件部分和硬件部分组成。

软件部分主要包括三大部分:PC机应用程序、FX3固件程序FPGA程序。

硬件部分主要由FPGA、USB3.0芯片和DDR2组成,硬件的系统框图如图2所示。

CYUSB3014

CYPRESS CYUSB3014 从EEPROM中启动:1.硬件配置PMODE[2:0]需要设置为1FF(注F表示引脚悬空;硬件EEPROM与I²C引脚相连)2.软件设置①配置芯片从USB启动(F11),烧写带有UsbI2cRegMode的.img程序文件;②按照下图烧写8个字节的启动数据;以上操作是向EEPROM中写入8字节数据43 59 0B B2 F8 00 B4 04,其中前两个字节是CYPRESS公司的签名CY,第三个字节是是EEPROM相关的设置,第四个字节是从EEPROM启动的标志,最后4个字节是PID和VID的值。

其中PID的值是00F8,这里故意设置成非00F1,以便和之前的驱动分别开来。

图中第6点说明烧写成功;③验证一下上面烧写是否真正成功,按照下图操作:上图中第3,说明从EEPROM中读出的8个字节,正是前一个过程烧写进去的8个字节,烧写成功;④拔掉USB线,将硬件启动模式设置为从EEPROM启动(1FF或F1F);⑤出现下图画面,说明USB芯片已经从EEPROM启动了,由于PID=0081,是新设备,因此需要安装驱动程序。

3.软件编写①Initialize the I2C interface for the EEPROM of page size 64 bytes.→status = CyFxI2cInit (CY_FX_USBI2C_I2C_PAGE_SIZE);②Start the USB functionality.打开USB的功能→status = CyU3PUsbStart();③④⑤→4.I2C 接口采用VIO5 供电,该电压独立于其他串行外设。

这样,I2C接口可以灵活地在不相同的电压下工作,这个不同于其他串行接口。

I2C控制器所支持的总线频率为100 kHz、400kHz和1MHz。

当VIO5为1.2V时,支持的最大工作频率为100kHz。

当VIO5 为1.8 V、2.5 V或3.3 V时,支持的工作频率为400 kHz和1MHz。

cyusb3014硬件设计方案

cyusb3014硬件设计方案CYUSB3014是一款高性能USB 3.1 Gen 1外围设备控制器,广泛应用于各种USB接口设备中。

本文将详细介绍CYUSB3014的硬件设计方案,包括电路原理图、PCB布局、供电系统等关键设计要点。

一、总体设计方案CYUSB3014的硬件设计方案主要包括如下几个方面:电源管理、时钟系统、传输接口、外设接口以及调试接口等。

1. 电源管理CYUSB3014采用3.3V供电,需要提供一个稳定可靠的电源系统。

一般建议使用线性稳压器或者开关稳压器来提供3.3V电源,同时要遵循电源滤波、去耦、综合保护等设计原则。

2. 时钟系统CYUSB3014需要外部提供参考时钟,常用的方案是使用晶体振荡器与时钟输入引脚相连,振荡器的频率一般为19.2MHz。

此外,还需要为CYUSB3014提供一个时钟源,用于USB通信的时钟同步。

3. 传输接口CYUSB3014支持USB 3.1 Gen 1传输接口,可通过SuperSpeed USB 连接到主机。

在设计传输接口时,需要合理布局USB差分信号对,保证信号传输的稳定性和可靠性。

此外,还需要为数据线提供合适的阻抗匹配电路,以减少信号损耗。

4. 外设接口CYUSB3014支持多种外设接口,如UART、SPI、I2C等。

在设计外设接口时,需要根据实际需求选择合适的接口类型,并遵循相应的电气规范和信号传输原则。

5. 调试接口为了方便调试和测试,CYUSB3014提供了JTAG调试接口。

在设计时,需要保留JTAG接口的引脚,并为其提供合适的连接器,以便于联机调试和故障排除。

二、电路原理图设计电路原理图是CYUSB3014硬件设计的基础,它展示了CYUSB3014与其他电路元件之间的连接关系。

在绘制电路原理图时,需要清晰标注各个元器件的型号、数值和引脚信息,并按照信号流的方向进行布局。

三、PCB布局设计PCB布局设计是CYUSB3014硬件设计中至关重要的一环,它直接关系到电路的稳定性和性能。

USB3.0调试手册

USB3.0调试⼿册宁波舜宇车载光学技术有限公司USB3.0数据采集系统FPGA+USB3.0韩斌2017/6/9USB3.0数据采集系统⽤户⼿册批准:审核:作成:⽇期⼀、USB协议概述关于USB的协议在《IFLabs USB3.0核⼼板开发⼿册V1.4》介绍的很详细,接下来主要介绍我在此间所学的⼀些总结和概括。

每个USB设备都可以包含⼀个或多个配置,不同的配置使设备表现出不同的功能组合,配置由多个接⼝组成。

在USB 协议中,接⼝代表⼀个基本的功能,⼀个功能复杂的USB设备可以具有多个接⼝, ⽽接⼝是端点的汇集。

端点的作⽤类似于寄存器。

每个端点在设备内部有唯⼀的端点号。

主机和设备通讯需要通过端点作为媒介。

端点的特点是单向性(即在某⼀时间只读或只写)。

设备的逻辑结构和组织结构见下图所⽰:PC机识别USB设备通过设备枚举来实现,⽽设备枚举⾸要步骤就是获取设备描述符。

在每⼀个USB设备内部,包含了固定格式的数据,通过这些数据,USB主机就可以获取USB 设备的类型、⽣产⼚商等信息。

这些固定格式的数据,我们称之为USB 设备描述符。

标准的USB设备有5种USB描述符:设备描述符、配置描述符、接⼝描述符、端点描述符合字符串描述符。

USB数据通讯模型的传输有四种传输⽅式,分为中断传输、批量传输、同步传输、控制传输。

如下就是控制传输的模型图:USB四个传输⽅式⼀般⼜分为三个事务:IN事务、OUT事务和SETUP事务,见下图所⽰:事务⼜分为令牌包(setup)、数据包(data)、握⼿包(ACK)、特殊包,如下图所⽰:⼀个包分为同步域(SYNC),标识域(PID),地址域(ADDR),端点域(ENDP),帧号域(FRAM),数据域(DATA)和校验域(CRC),见下图所⽰:USB正常⼯作之前,第⼀件事就是设备枚举,⽬的就是让主机认得这个USB设备,并且为这个设备配置资源,建⽴好主机与设备之间的数据传输通道。

设备枚举分为如下8个步骤:1,获取设备描述符2,复位3,设置地址4,再次获取设备描述符5,获取配置描述符6,获取端点、配置描述符7,获取字符串描述符8,选择设备配置⼆、CYUSB3014的SDK概述2.1介绍CYUSB3014的开发⽀持包由Cypress⽀持和提供,取名为FX3 SDK。

USB3.0硬件设计指南

Cap Value 0.1 uF, 0.01 uF 0.1 uF, 2.2 uF 0.1 uF, 2.2 uF 0.1 uF, 2.2 uF 0.1 uF, 0.01 uF 0.1 uF, 0.01 uF Number of caps 4 of each 1 of each 1 of each 1 of each 1 of each 1 of each per supply Pin Name VDD AVDD U3TXVDDQ U3RXVDDQ CVDDQ VIO1-5

This protection ensures the device will continue to function after ESD events up to the levels stated. The SSRX+, SSRX-, SSTX+, SSTX- pins have only up to +/- 2.2KV Human Body Model (HBM) internal ESD protection. Additional protection can be added to these pins by using high performance, low capacitance external ESD devices. To prevent an effect on the performance of this bus, the added capacitance should not exceed 0.4 pF. In terms of EMI, all signal and clock traces emit electromagnetic (EM) radiation when they switch from one level to another. To meet the various standards in different countries, these emissions must be minimized. You can use several techniques to lower EM emissions:

FX3 CYUSB3014

• San Jose, CA 95134-1709 • 408-943-2600

Revised December 6, 2011

CYUSB3014

Contents

Functional Overview .......................................................... 3 Application Examples .................................................... 3

■ Independent power domains for core and I/O ❐ Core operation at 1.2 V ❐ I2S, UART, and SPI operation at 1.8 to 3.3 V ❐ I2C operation at 1.2 V

■ 10 × 10 mm, 0.8 mm pitch Pb-free ball grid array (BGA) package ■ EZ-USB® software and DVK for easy code development

■ General programmable interface (GPIF™ II) ❐ Programmable 100-MHz GPIF II interface enables connectivity to wide range of external devices ❐ 8-/16-/32-bit data bus ❐ Up to 16 configurable control signals

TX RX CTS RTS SS N SCK MIS O MOS I I2S _CLK I2 S_S D I2S_WS I2 S_ MS CL K

CYUSB3014型USB3.0+FPGA电路设计详解说明书

CYUSB3014型USB3.0+FPGA 电路设计详解小梅哥2016年12月29日星期四芯航线AC6102开发板上,使用了一片Cypress 的USB3.0全协议芯片CYUSB3014作为FPGA 与PC 机的高速通信桥梁。

关于CYUSB3014的各项性能和参数介绍,请参考AC6102 USB3.0开发教程中相关介绍。

本节主要介绍AC6102开发板上USB3.0电路的设计细节,方便大家在使用的时候快速核对理解。

以下为AC6102开发板上的USB3.0电路整体框图说明为了充分发挥USB3.0芯片的特性,特将CYUSB3014芯片的所有数字IO 与FPGA 连接,包括32根数据线,13根控制线、4根I2S 信号线以及UART 线等。

复位CYUSB3014有一个复位输入接口,当复位输入为低电平时,芯片处于复位状态。

只有当该引脚为高电平时,芯片才能正常工作,AC6102开发板在设计时,充分考虑了实际应用和系统调试时的情况,给CYUSB3014设计了两种复位方式,分别为FPGA控制复位和上电自动复位。

默认使用上电自动复位方式,该方式非常适合我们调试系统原型时使用,这样不必担心因为重新下载FPGA 的sof固件而导致USB芯片复位,影响USB3.0芯片的正常运行。

增加调试时候的工作量。

(如果使用fpga控制复位,那么每次下载完fpga的sof后,都会对USB芯片执行一次复位操作,从而使芯片内烧写的固件丢失,那么用户只能再烧写一次usb 芯片固件,从而增加了调试时候的工作量)。

如下图,R64默认没有焊接,即断开了CYUSB 芯片与FPGA芯片的连接,从而避免受到FPGA固件的影响,如果产品最终定型需要测试使用FPGA直接控制USB芯片复位,给R64安装100R左右的电阻即可。

时钟晶振CYUSB3014支持外部晶振提供时钟信号,支持19.2、26、38.4和52MHz的时钟频率,AC6102开发板上使用19.2MHz的晶振为CYUSB3014提供时钟源。

CYUSB3014各文档功能说明

3、AN68914.pdf

这是一篇专门说明如何从I2C启动的文章。主要有启动引脚的配置,I2C存储器的选择,启动文件映像的格 式等方面。

4、AN65974.pdf

最新博客

这是一篇说明实现SLAVE FIFO模式的文章。

open in browser PRO version Are you a developer? Try out the HTML to PDF API

良子USB 发消息 写留言 加好友 RSS订阅

博文分类

1、AN70707.pdf

这是一篇关于CYUSB3014画电路板时需要注意的事项的文章。从电源引脚的退耦,BGA封装 焊 盘 的 大 小 , 板 层 的 选 择 , USB3.0连 接 器 的 选 择 , 到 布 局 布 线 需 要 遵 守 的 很 多 准 则 等 方 面 , 都 提 供了详细的说明。

以下网友评论只代表其个人观点,不代表本网站的观点或立场

open in browser PRO version Are you a developer? Try out the HTML to PDF API

New hot app: Facebook Albums | 注册 元器件数据手册一数网据搜手尽册

搜索

liangziusb的 博 客

个人档案

博客

相册

个人档案

USB3.0芯片终于出来了_LZ3014 USB3.0开发板17(现有开发资料汇总) 2011-11-24 10:47

加入收藏

转发分享

USB3.0的芯片CYUSB3014面世已经有半年多了,但现在相应的开发资料还很少,只有区区四个文档,其 中一个文档官方发布了几天,随后又突然删除了。这里对这四个文档作一简单的说明,希望对广大网友有所帮 助。当然,官方的正式文档还没有发布,这其中肯定还会有一些错误。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

VDD 22uF 0.1uF VDD VBAT 0.01uF 0.1uF VBATT

AVDD 2.2uF 0.1uF

AVDD

VIO1 0.01uF 0.1uF

VIO1

U3TXVDF 0.1uF

VIO2

U3RXVDDQ 22uF 0.1uF

U3RXVDDQ

VIO3 0.01uF 0.1uF

VIO3

CVDDQ 0.1uF VBUS 0.1uF 0.01uF

CVDDQ

VIO4

VIO4 0.01uF 0.1uF

AVSS U3VSS U2AFE U2PLL

VBUS

VIO5

VIO5 0.01uF 0.1uF

Table 1. EZ-USB FX3 Power Domains Description

Max 1.25 1.25 3.6 3.6 3.6 3.6 3.6 6 6 3.6 1.25 1.25

Unit V V V V V V V V V V V V

Document No. 001-70707 Rev. *E

2

EZ-USB FX3™ Hardware Design Guidelines and Schematic Checklist

®

Power Modes

EZ-USB FX3 supports the following power modes:

Standby mode (L3): Power supply for the wakeup source and core power must be retained. All other power domains can be turned off/on individually. Core power down mode (L4): Core power is turned off. All other power domains can be turned off/on individually.

Contents

Introduction ....................................................................... 1 Power System ................................................................... 2 Overview ...................................................................... 2 Power Modes ............................................................... 3 Device Supply Decoupling............................................ 3 Inrush Current Consideration and Power Supply Design .............................................................. 4 Clocking ............................................................................ 5 Crystal .......................................................................... 5 Clock ............................................................................ 6 Watchdog Timer ........................................................... 6 GPIF II Interface ................................................................ 6 I2C Interface ...................................................................... 6 Low Performance Peripherals (LPP) ................................. 7 JTAG ............................................................................ 7 2 I S................................................................................. 7 SPI and UART .............................................................. 7 Booting .............................................................................. 7 EMI and ESD Considerations ............................................ 7 FX3 Device Package Dimensions ..................................... 8 Electrical Design Consideration ........................................ 8 USB 3.0 SuperSpeed Design Guidelines ..................... 8 Appendix A – PCB Layout Tips ....................................... 14

2

Min 1.15 1.15 1.7 1.7 1.7 1.7 1.15 3.2 4.0 1.7 1.15 1.15

VSS

Typical 1.2 V typical 1.2 V typical 1.8, 2.5 and 3.3 V typical 1.8, 2.5 and 3.3 V typical 1.8, 2.5 and 3.3 V typical 1.8, 2.5 and 3.3 V typical 1.2, 1.8, 2.5 and 3.3 V typical 3.7 V typical 5 V typical 1.8, 3.3 V typical 1.2 V typical 1.2 V typical

Normal mode: This is the full-functional operating mode. In this mode the internal CPU clock and the internal PLLs are enabled.

Introduction

The Cypress EZ-USB FX3 has an integrated USB 3.0 and USB 2.0 physical layer (PHY), and a fully configurable, parallel, general programmable interface called GPIF II, which can connect to an external processor, ASIC, or FPGA. EZ-USB FX3 enables data transfers up to 320 MBps from GPIF II to the USB interface. To successfully add this high throughput pipe to a system, a developer has to consider a number of critical items when designing the system. Because of the packaging and high-performance characteristics of the EZ-USB FX3 device, you should follow the guidelines for trace width, stack up, and other layout considerations to make sure the system will perform as expected. A reference schematic for the EZ-USB FX3 DVK is available at CYUSB3KIT-001 EZ-USB® FX3™.

AN70707 EZ-USB® FX3™ Hardware Design Guidelines and Schematic Checklist