载板制程封装介绍

芯片封装工艺过程简介

SMT SMT

Company Logo

IC Package (IC的封装形式)

• 按封装外型可分为:

SOT 、QFN 、SOIC、TSSOP、QFP、BGA、CSP等;

封装形式和工艺逐步高级和复杂

• 决定封装形式的两个关键因素:

封装效率。芯片面积/封装面积,尽量接近1:1; 引脚数。引脚数越多,越高级,但是工艺难度也相应增加;

Key Words:

Capillary:陶瓷劈刀。W/B工艺中最核心的一个Bonding Tool,内部为 空心,中间穿上金线,并分别在芯片的Pad和Lead Frame的Lead上形 成第一和第二焊点;

EFO:打火杆。用于在形成第一焊点时的烧球。打火杆打火形成高温, 将外露于Capillary前端的金线高温熔化成球形,以便在Pad上形成第一 焊点(Bond Ball);

IC Package种类很多,可以按以下标准分类:

• 按封装材料划分为: 金属封装、陶瓷封装、塑料封装

• 按照和PCB板连接方式分为: PTH封装和SMT封装

• 按照封装外型可分为: SOT、SOIC、TSSOP、QFN、QFP、BGA、CSP等;

IC Package (IC的封装形式)

• 按封装材料划分为:

FOL– Wire Bonding 引线焊接

※利用高纯度的金线(Au) 、铜线(Cu)或铝线(Al)把 Pad 和 Lead通过焊接的方法连接起来。Pad是芯片上电路的外接 点,Lead是 Lead Frame上的 连接点。 W/B是封装工艺中最为关键的一部工艺。

FOL– Wire Bonding 引线焊接

Wafer Mount 晶圆安装

Wafer Saw 晶圆切割

浅谈集成电路封装环节的IC载板

封装基板作为芯片封装的核心材料,一方面能够保护、固定、支撑芯片,增强芯片导热散热性能,保证芯片不受物理损坏,另一方面封装基板的上层与芯片配,以及沟通芯片内部与外部电路等功能。

IC 载板性能优良,应用占比持续提升。

与常规 PCB 板相比,封装基板线宽、线距更小,板子尺寸更小,能达到主流芯片的严苛要求。

线宽/线距50μm/50μm 属于PCB 高端产品,而封装基板制造领域,线宽/线距在30μm/30μm 以内属于常规产品。

随着技术朝高密度、高精度发展,高端产品封装基板在PCB板中占比也逐步提升。

根据prismark,2000 年封装基板在PCB板中占比8.43%,2020年封装基板占比为15.68%,预测至2026 年,封装基板占比将达到21.11%,占比稳步提升。

IC 载板主要用于集成电路封装环节,是封装环节价值量最大的耗材。

根据中研网,IC 载板在中低端封装中占材料成本的40~50%,在高端封装中占70~80%。

原材料可分为结构材料(树脂、铜箔、绝缘材等)、化学品(干膜、油墨、金盐、光阻、蚀刻剂、显影剂)以及耗材(钻头)。

其中,树脂、铜箔、铜球为占IC 载板成本比重最大的原材料,比分别为35%,8%,6%。

根据华经产业研究院数据,IC 载板下游主要应用于移动终端(26%)、个人电脑(21%)、通讯设备(19%)、存储(13%)、工控医疗(8%)、航空航天(7%)、汽车电子(6%)。

从产业链上来看,IC 载板运用于集成电路封装阶段。

电子封装是器件到系统的桥梁,这一环节极大影响力微电子产品的质量和竞争力。

随着半导体技术的发展,IC 载板的特征尺寸不断缩小、集成度不断提高,相应的IC 封装向着超多引脚、窄节距、超小型化方向发展。

根据《中国半导体封装业的发展》,迄今为止全球集成电路封装技术一共经历了五个发展阶段。

当前,全球封装行业的主流技术处于以CSP、BGA 为主的第三阶段,并向以系统级封装(SiP)、倒装焊封装(FC)、芯片上制作凸点(Bumping)为代表的第四阶段和第五阶段封装技术迈进。

IC载板~1

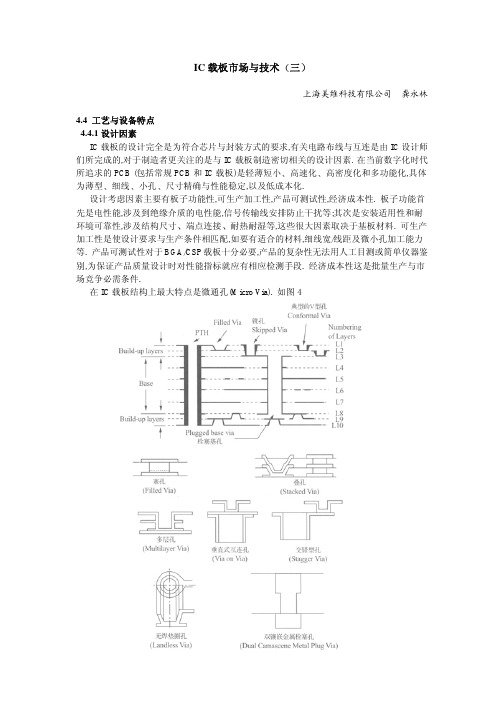

IC 载板市场与技术三4.4 工艺与设备特点4.4.1设计因素IC载板的设计完全是为符合芯片与封装方式的要求,有关电路布线与互连是由IC设计师们所完成的,对于制造者更关注的是与IC载板制造密切相关的设计因素. 在当前数字化时代所追求的PCB (包括常规PCB和IC载板)是轻薄短小高速化高密度化和多功能化,具体为薄型细线小孔尺寸精确与性能稳定,以及低成本化.设计考虑因素主要有板子功能性,可生产加工性,产品可测试性,经济成本性. 板子功能首先是电性能,涉及到绝缘介质的电性能,信号传输线安排防止干扰等;其次是安装适用性和耐环境可靠性,涉及结构尺寸端点连接耐热耐湿等,这些很大因素取决于基板材料. 可生产加工性是使设计要求与生产条件相匹配,如要有适合的材料,细线宽/线距及微小孔加工能力等. 产品可测试性对于BGA/CSP载板十分必要,产品的复杂性无法用人工目测或简单仪器鉴别,为保证产品质量设计时对性能指标就应有相应检测手段. 经济成本性这是批量生产与市场竞争必需条件.在IC载板结构上最大特点是微通孔(Micro Via). 如图4下表9 列出了芯片尺寸端子节距有关输出入端子数. 芯片边上端子数是按相应的芯片尺寸与端子节距计算的,端子间可布设引线数也可作相应计算.表9 IC载板的设计参数[引自电子技术 2001/6 ]参数项目 2001 2002 2003 2004 2005 2008 2011倒芯片端点节距(m) 175 175 150 150 130 115 100连接盘大小(m) 88 88 75 75 65 58 50芯片尺寸 (mm/边)经济性能型13 14 15 15 15 15 16高性能型18 18 18 19 19 21 22阵列规模=沿芯片边沿端点数经济性能型(最多) 75 79 98 100 118 133 164经济性能型(常规要求) 35 37 39 41 43 50 59高性能型(最多) 101 103 123 126 148 180 221高性能型(常规要求) 52 55 58 61 65 77 91外部行列通路数(取决于输出层数要求)经济性能型 5 5 4 5 5 5 6高性能型8 8 8 8 8 9 10输出要求有效的总布线密度 (cm/cm2 )经济性能型 286 286 267 333 385 435 600高性能型 457 457 533 533 615 783 1000基板上布线(节距通路间3条线)线路宽度(m) 29.2 29.2 32.1 25.0 21.7 19.2 13.6 线路间距(m) 29.2 29.2 32.1 25.0 21.7 19.2 13.6基板上布线(节距通路间6条线)线路宽度(m) 17.5 17.5 15.0 15.0 13.0 10.1 7.9线路间距(m) 17.5 17.5 15.0 15.0 13.0 10.1 7.94.4.2 图形制作印制板线路形成的基本方法有三大类,即全加成法半加成法减去法. 在常规印制板生产中主要采用减去法,而IC载板生产这三类工艺都有采用,目前采用半加成法的较多些. 然而这三类工艺中都涉及到图形转移成像技术.IC载板的线路图形都是精细线条, 采用光致成像技术. 光致成像技术涉及到光致抗蚀剂材料,有干膜型和液态型正性和负性水(弱碱性)显影型和有机溶剂显影型等区分;涉及到曝光设备和光源,有平行光和非平行光紫外光和激光等区分. 而以图像转移方式区别主要技术如下.(1) 接触印制成像(Contact Printing) 这是目前印制板生产通用的技术,采用照相底版覆盖在已有光致抗蚀层基板表面,照射紫外光曝光, 照相底版与有光致抗蚀层基板表面之间是通过抽真空而紧密接触的. 这种方式由于照相底版厚度和光源散射等因素,形成图形线条到2 mil 可说是极限了.(2) 激光投影成像(LPI: Laser Projection Imaging) 这是应用准分子激光源照射照相底版,透射的光再投影到已有光致抗蚀层基板表面,感光出线路图形. 该装置的强力激光经过折射系统后投影到基板的是平行光,因此照相底版与基板是不接触的,又能保持图形精度. 如用30m 厚的光致干膜能产生线宽/线距为35/35m的图形,若用13m厚的液态光致抗蚀刻能产生线宽/线距为10/10m的图形,(3) 激光直接成像(LDI: Laser Direct Imaging) 这是应用聚焦的激光束按程序扫描,使已有光致抗蚀层基板表面曝光产生线路图形. 这过程不需要照相底版,类似于激光绘图机由计算机程序扫描出线路图形. 由于不用照相底版,也就不存在照相底版引起的收缩变形定位偏差和疵点等问题.另外,有激光直接刻板工艺(Laser Direct Structuring Process),其原理与LDI相似, 但是采用锡为图形转移的抗蚀层,而非光致抗蚀剂. 其工艺是在基板面铜层上化学浸锡,经激光束扫描使锡层和极少铜层气化,形成线路图形,留下锡层是以后化学蚀刻铜时的抗蚀层.(4) 步进重复成像(Step and Repeat Imaging) 这是将整块在制板分成若干单元,使成像面积大小(最大5 ~6 in 2 )与单块或多块IC载板面积相一致. 再利用紫外光通过反射到照相底版,透过照相底版和透射镜,把图形投影在基板上一个单元部位,分步重复进行就形成全板面光致抗蚀层曝光. 此方法照相底版与基板也不接触,在小面积内投射光也近似平行光,确保图形精度. 只是分步曝光速度慢产能低.表10 几种光致成像方法的比较成像方法接触印制成像激光投影成像激光直接成像步进重复成像光源汞弧灯准分子激光氩离子激光汞弧灯散射光 , 平行光UV激光照相底版类型聚酯或玻璃(接触) 聚酯或玻璃(投影) (不用) 聚酯或玻璃(投影) 线条分辨力75m, 38m 2.5m 50m 7.5m定位精确度约25m ,约8m 优(约1m) 尚好(约12m) 好(约2.5m) 生产效率大板面,大批量大板面,大批量快速,小批量小面积,中批量设备成本(单价) $20 ~80万元 $50 ~120万元 $50 ~150万元 $40 ~100万元细线条线路图形成像后,半加成法与减去法都有化学蚀刻完成图形. 蚀刻过程与常规印制板加工相同,但为实现细线条需要考虑以下几点: a.应是厚度均匀的薄铜层,被蚀刻铜层厚度应小于线路间距的1/2; 蚀刻剂稳定性好,有护岸效应使侧蚀极小,并与抗蚀剂相匹配; 蚀刻设备状态佳,有较高喷淋压力和均匀摆动,并用汇流排液方式减少水池效应.在图形转移中光致抗蚀剂材料无疑是个重要因素. 无论是干膜型和液态型除了感光性外,要与基板有好的粘附力,并能薄型化. 抗蚀膜层薄可提高解像力实现细线条.另外, 在图形转移中环境条件也极其重要. 需要有恒定温湿度环境外,更需要有洁净环境.在半导体制造中以最小线宽的1/5 ~1/10尘埃为净化对策,那么若印制板L/S=25/25m,不允许有5m以上尘埃,达到ISO 4级(相当100级).4.4.3微通孔形成IC载板的高密度化,除了细线条外就是微通孔. 微通孔加工方法有多种多样,在IPC/JPCA –2315 HDI板和微通孔设计指南标准中介绍了10种微通孔加工方法. 而常用的是机械钻孔光致成孔激光穿孔和等离子蚀孔. 其中又以激光穿孔应用最多,几乎将近占80 %;其次光致成孔约占15 %.微通孔(Micro Via)是指孔径小于0.15mm的互连金属化孔,孔的结构有埋孔盲孔和贯穿孔.埋孔又有两层导通埋孔或多层导通埋孔,盲孔也有两层导通盲孔或多层导通盲孔.激光穿孔是用一种准直光(激光)直射物体形成小孔.激光成孔原理是按激光波长能量不同分为光热烧蚀与光化学烧蚀. 光热烧蚀是指材料在吸收激光能量后,即被加热至熔化并蒸发掉形成小孔,在成孔孔壁留有炭化残渣. CO2 激光是属这种光热烧蚀, CO2 激光器激发出的是红外光和可见光热能. 光化学烧蚀是属紫外光区域的高光子能量破坏材料的分子链,使材料变成更小微粒逸出形成小孔,此孔壁没有产生炭化. UV-YAG激光器发出的是紫外线光,属这种光化学烧蚀成孔.CO 2 激光波长较长(约9m),树脂和玻璃都可吸收CO2 激光,可被加工出小孔. 而铜几乎不吸收CO2 激光,就不能在铜箔上直接加工出小孔. 据此CO2 激光成孔技术面对的工艺: a.树脂层直接成孔,面对的表面为涂布或层压的绝缘层,激光形成盲孔; b.铜面开窗孔后成孔,表面铜箔经掩膜和蚀刻露出树脂层孔点,再激光穿透树脂层形成盲孔; c.超薄铜箔直接成孔,表面铜箔很薄(5m以下)并经黑氧化处理提高对CO 2 激光能量吸收,这样CO2 激光就能穿透薄铜层及绝缘层形成小孔. CO2 激光的穿孔速度较快,效率高,相对成本低,所以应用较多. 不能直接穿透铜,既是缺点,也是容易实现盲孔的优点. 不足的是成孔中会有树脂残渣,在孔金属化前要去除玷污.UV-YAG激光波长短(约355nm),铜纤维布与树脂都能吸收此光能,因此可一次直接形成小孔,而且形成小孔较光洁干净无玷污. UV-YAG激光穿孔相对速度慢些,成本高些. 目前UV-YAG激光的应用量在增大.另外还有准分子(Excimer)激光具有宽的高强度光束,对铜纤维布与树脂都能穿透,成孔质量很好. 但因速度较慢,成本高,所以使用很少.光致成孔工艺在激光成孔前就应用,其关键是绝缘层为感光性树脂. 感光性绝缘树脂(液态或干膜状)涂覆于基板(芯板)后,用有孔点照相底版曝光,经显影就形成小孔.表11 几种激光法与光致成孔法加工性的比较成孔方法CO2 激光UV-YAG激光准分子激光光致成孔等离子体蚀孔加工孔径(m) 70 ~250 25 ~100 10 ~150 50以上70以上铜箔加工不可可可不可不可树脂加工可可可可可纤维布加工可可可不可可成孔品质后处理良优良良生产效率批量中低批量中加工成本中较高高低中4.4.4电镀微通孔要起到层间互连作用,孔内必须金属化导通. 还有积层表面若是没有铜箔的绝缘层,这就需要沉积导体层. 为达到这些要求是采用化学镀铜和电镀铜,基本工艺与常规PCB生产相同. IC载板的特殊性是: 基板薄,搬运操作易损坏; 有微通孔和盲孔,孔内电镀均一难达到; 实现细线条与细间距,必须板面镀层均匀和结合力好; 表面安装芯片,镀层必须平滑均匀.目前较多的是采用水平式直接电镀技术. 水平式直接电镀是把化学镀铜与电镀铜过程联合在一起,已达到薄板自动化传送,减少过程搬运中损坏. 水平传送对板子处理均匀性好,受化学溶液流动清洗阴阳极间距离及电流密度都能相同. 水平传送生产线从去毛刺去玷污化学镀铜与电镀铜成连续自动线,生产效率高.为保证盲孔电镀可靠及板面镀层均匀,在水平传送化学镀铜过程中改变以往浸渍式处理板子为溢水喷射式,各工序流体被强制循环或有超声波装置,确保小孔内清洁无气泡和湿润. 水平电镀铜过程中同样从流体力学角度强制溶液循环,与小孔内充分接触.要达到高厚径比的孔和微孔的孔内镀层厚度均匀及与板面厚度一致,从电镀理论来说是要提高电镀分散能力(Throwing Power),目前是在从三个方面努力改进. 一是电镀槽装置改进,无论时水平式或垂直式电镀,均从流体力学角度使新鲜溶液不断进入孔内,保持溶液离子分布均匀性,同时采用不溶性阳极; 二是电镀电源改进,将直流电源改为正反向周期性变换的脉冲电源,以改变板面与孔内的沉积速率; 三是调整溶液成份,特别是添加剂(光亮剂整平剂),通过添加剂抑制板面镀层沉积而相应提高了孔内镀层沉积速率.目前水平传送周期转向脉冲电镀(PPRP)是较成功的,既有水平传送是溶液喷流长处,又用大电流反向脉冲控制, Throwing Power达到90 %以上. 现还有应用不溶性阳极与无添加剂脉冲电镀,也有好的效果. 也有仍应用直流电源而通过电镀装置改进,采取电镀液喷流实现高厚径比的孔和微孔电镀的. 也有改进添加剂而取得好的微孔好效果,甚至做到硫酸铜电镀盲孔同时实现镀铜塞孔.4.4.5表面处理在IC载板生产过程中需要有二种表面处理过程,一是内层间叠合时为提高层间结合力而需要的内层表面处理; 另一种是表面导体端点和连接盘的表面处理.内层表面处理对象一是绝缘树脂层,要表面层平整,又有微观粗糙度. 这是使与后道沉积的铜层结合牢固,或者与再复合的绝缘层粘合可靠. 内层表面处理对象另一是铜线路层,使铜表面有微观粗糙度,与再复合的绝缘层结合可靠. 处理方法有化学清洗微蚀法机械研磨法化学机械结合法. 对仅铜线路层表面处理主要是化学方法,采取微蚀和黑氧化或棕氧化处理,鉴于这线路细铜层薄,处理过程也是细微的,都采用水平传送设备. 绝缘树脂层或含有铜线路的表面处理主要是化学机械结合法.为IC载板平整化提出化学机械平整(CMP)技术,这是在化学去氧化后再精细地机械研磨,再是化学清洗水洗和纯净水洗干燥. 机械研磨工具不可能是通常的砂轮或尼龙针刷,而是不织布纤维粘合细粒无机氧化硅与氧化铝的抛轮,研磨粒度在1000目以上,并向更细发展. IC载板在最后表面涂覆阻焊剂前,也是采取这种CMP处理.表面导体端点和连接盘的表面处理是在铜端点和连接盘表面涂/镀可焊的保护层,为了与芯片互连及在以后印制板上安装可靠. IC载板上安装连接采取的是焊锡熔焊(Solder Fusing或打线搭接(Wire Bonding)方法,要求连接盘平整可焊. 表面常用镍-金镀层,或无铅的锡银镀层,个别的用贵金属钯铑镀层等.连接盘镍-金镀层现主要应用化学镀镍浸金(ENIG)技术. 在铜面上化学镀镍溶液主盐是氯化镍或硫酸镍,以次磷酸钠为还原剂使已催化铜面产生镍,新生的镍有自身催化性可使镍层不断加厚,一般控制镍层厚度3 ~5m. 化学浸金是置换反应,由镍置换金,当镍层表面全部覆盖金后反应停止. 因此浸金层很薄,约0.05 ~0.1m. 化学镀镍浸金过程是在一条生产线上进行,经过酸洗微蚀催化(活化)和化学镀镍浸金. 对于BGA/CSP细间距载板,采用钯催化会发生间距内微量镍析出,影响板子电性能,因此在改用二甲胺甲硼烷(DMAB)为还原剂介决这问题. 镍层是可焊性关键,不应有黑镍现象.焊锡熔焊的安装连接盘上除镍-金镀层外,还常用无铅的锡或银镀层,并采用化学镀工艺.化学镀无需连接盘连通电,获得的镀层平整均匀性好. 纯锡层较软而易产生锡须,熔点较高,为与原有锡铅熔点相近,采用也是锡合金. 也有锡合金镀层有锡银锡铜锡铋锡锌锡钴等二元合金,以及锡银铜锡铋铜和锡锌铜等三元合金. 按美国JEDEC定义,焊料中铅含量重量比少于0.2 %是无铅,美国NEMI推荐的是锡银铜合金焊料,适合于235再流焊. 因此,化学镀锡银铜合金为佳. 同样有水平式化学镀锡设备,获得好的效果.4.4.6检测IC载板的检测如常规PCB那样包括外观电性能耐环境性等各方面,只是板子的高密度化势必有更高检测技术.外观检查BGA/CSP封装板是不可能单靠人工肉眼观察了,是采用自动观察检查(A VI: Automatic Visual Inspection)系统. 该系统是有光学系统,进行图像扫描摄取; 有计算机处理系统,分析图形正确性,找出各种缺陷; 有自动化系统,达到自动上料检测识别和下料等. 另外有为BGA/CSP封装板提供的新一代光学式自动外观检查(AOI)设备,比一般AOI分辨力高约10倍,解像度2m,适合于L/S=20/20m的细线条板检查.这种设备是输入CAD数据作为检查基准,采用CAD数据比较法(非照相版图形比较法)精确度高.电性能首先是通断路检测,测试原理与常规印制板相同,只是被测试密度高得多了. 用于BGA/CSP封装板通断路检测高效率的是自动接触式电路通断检测机,被测板子节距可小到30m,线宽/线距15/15m,检测时定位误差小于10m,所用夹具寿命可接触100万次. 还有简易些的是多针头的飞针测试机,在A B两面各有2根探针, 检测时定位精度5m以内,可测导线电阻范围0.001 ~399.9,读数精确度0.1m.有全自动裸板综合检查系统,将电气检测与外观检查相结合同步进行,以提高效率. 电气检查可选择测量时电压与电流,采用专用夹具,所测量电阻值从m到M分别设定. 外观检查是采用光学系统,检查内容包括缺损划痕针孔残余物异物分层剥落和偏位等缺陷.根据IC载板性能要求,还有许多检测项目. 如用精密读数测量仪,测量板子尺寸和孔径线宽等; 用X射线镀层测厚仪,检测表面镀层厚度; X射线分析计测仪测定无铅镀层(Sn-Ag Sn-Bi等)的成分与厚度; 时域反射仪(TDR)测量互连导线阻抗,自动阻抗测量机(TDR法)适合批量生产. 另外有环境试验,如热冲击耐焊性吸湿性和耐燃性等.。

BGA基板全制程简介

BT 树脂 (Bismaleimide Triazine Resin )

BT 树脂的全名为 bismaleimide - triazine resin(双顺丁烯酸酰亚 胺/三氮),是一种热固性树脂 (thermosetting resin),为以 上两种(B及T)成分之结合体,由 日本三菱瓦斯公司于1982年经由 Bayer公司技术指导后,使用连 续合成法进行商业化之量产,目 前全球仅其一家生产,产能为 250吨/年,因有鉴BGA之快速成 长,故1997年即投资24.5~32.7 百万美元增加生产线,使产能扩 充至600~700吨/年。

网印

Pre cure

网印

Pre cure

黄光室

UV cure

Post cure

显影

opening

曝光

UV

底 片

22

镀Ni/Au

电镀Ni/Au

清洁槽(除表

面油脂及异物)

酸洗

水洗

水洗

微蚀槽

(清洁铜面)

水洗

酸洗(清洁铜

面及预浸酸)

水洗

镀Ni 槽(电

镀Ni至所需厚 度)

水洗

预镀金槽(镀

上一层薄金作为 后镀金之介层)

4

BGA基板制造流程

发料烘烤

2 layer

蚀薄铜

4 layer

线路形成(内层)

钻孔

AOI自动光学检测 Deburr

绿漆

AOI自动光学检测

线路形成

镀Ni/Au

成型

O/S电测 出货

压合

镀铜

塞孔 (option) 终检

包装

5

发料烘烤

功能: ❖消除基板应力,防止板弯﹑ 板翘

❖安定尺寸,减少板材涨缩

allegro制作PCB封装详细讲解

目录目录 (1)第一章制作Pad (2)1.1概述 (2)1.2制作规则单面pad略 (6)1.3制作规则过孔pad略 (6)1.4制作异形单面pad (6)第二章制作封装 (7)2.1普通封装制作 (7)2.2制作机械(定位孔/安装孔)封装 (8)2.3导出封装 (9)第一章制作Pad1.1概述一、Allegro中的Padstack主要包括1、元件的物理焊盘1)规则焊盘(Regular Pad)。

有圆形、方形、椭圆形、矩形、八边形、任意形状(Shape)2)热风焊盘(Thermal Relief)。

有圆形、方形、椭圆形、矩形、八边形、任意形状(Shape)3)抗电边距(Anti Pad)。

用于防止管脚和其他网络相连。

有圆形、方形、椭圆形、矩形、八边形、任意形状(Shape)。

2、阻焊层(soldermask):阻焊盘就是solder mask,是指板子上要上绿油的部分。

实际上这阻焊层使用的是负片输出,所以在阻焊层的形状映射到板子上以后,并不是上了绿油阻焊,反而是露出了铜皮。

通常为了增大铜皮的厚度,采用阻焊层上划线去绿油,然后加锡达到增加铜线厚度的效果。

3、助焊层(Pastemask):机器贴片的时候用的。

对应着所以贴片元件的焊盘、在SMT加工是,通常采用一块钢板,将PCB上对应着元器件焊盘的地方打孔,然后钢板上上锡膏,PCB在钢板下的时候,锡膏漏下去,也就刚好每个焊盘上都能沾上焊锡,所以通常阻焊层不能大于实际的焊盘的尺寸。

用“<=”最恰当不过。

4、预留层(Filmmask):用于添加用户自定义信息。

表贴元件的封装、焊盘,需要设置的层面以及尺寸5、Regular Pad:具体尺寸更具实际封装的大小进行设置。

推荐参照《IPC-SM-782A Surface Mount Design and Land Pattern Standard》。

6、Thermal Relief:通常要比规则焊盘尺寸大20mil,如果Regular Pad尺寸小于40mil,需要适当减小尺寸差异。

最全的芯片封装技术详细介绍(珍藏...

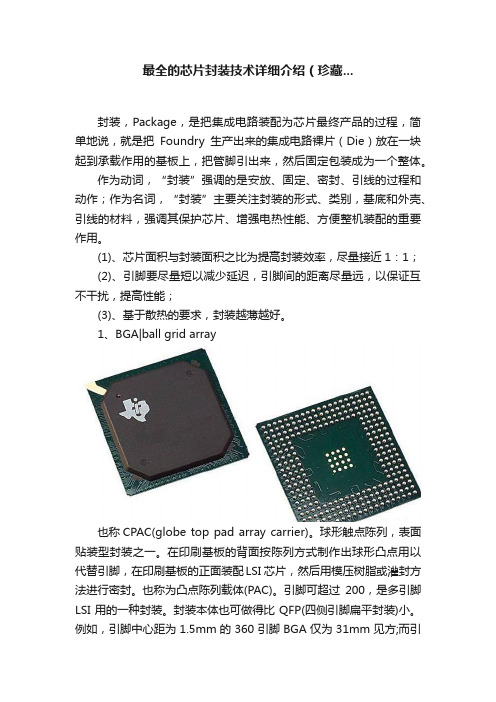

最全的芯片封装技术详细介绍(珍藏...封装,Package,是把集成电路装配为芯片最终产品的过程,简单地说,就是把Foundry生产出来的集成电路裸片(Die)放在一块起到承载作用的基板上,把管脚引出来,然后固定包装成为一个整体。

作为动词,“封装”强调的是安放、固定、密封、引线的过程和动作;作为名词,“封装”主要关注封装的形式、类别,基底和外壳、引线的材料,强调其保护芯片、增强电热性能、方便整机装配的重要作用。

(1)、芯片面积与封装面积之比为提高封装效率,尽量接近1:1;(2)、引脚要尽量短以减少延迟,引脚间的距离尽量远,以保证互不干扰,提高性能;(3)、基于散热的要求,封装越薄越好。

1、BGA|ball grid array也称CPAC(globe top pad array carrier)。

球形触点陈列,表面贴装型封装之一。

在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI 芯片,然后用模压树脂或灌封方法进行密封。

也称为凸点陈列载体(PAC)。

引脚可超过200,是多引脚LSI用的一种封装。

封装本体也可做得比QFP(四侧引脚扁平封装)小。

例如,引脚中心距为1.5mm的360引脚BGA仅为31mm见方;而引脚中心距为0.5mm的304 引脚QFP 为40mm 见方。

而且BGA不用担心QFP 那样的引脚变形问题。

该封装是美国Motorola 公司开发的,首先在便携式电话等设备中被采用,随后在个人计算机中普及。

最初,BGA 的引脚(凸点)中心距为1.5mm,引脚数为225。

现在也有一些LSI 厂家正在开发500 引脚的BGA。

BGA 的问题是回流焊后的外观检查。

美国Motorola公司把用模压树脂密封的封装称为MPAC,而把灌封方法密封的封装称为GPAC。

2、C-(ceramic)表示陶瓷封装的记号。

例如,CDIP 表示的是陶瓷DIP。

是在实际中经常使用的记号。

3、COB (chip on board)COB (chip on board)板上芯片封装,是裸芯片贴装技术之一,半导体芯片交接贴装在印刷线路板上,芯片与基板的电气连接用引线缝合方法实现,并用树脂覆盖以确保可靠性。

载板制程封装介绍

4. 無中介層, 壓模成型(Transfer Molding)

說明:先電鍍再上球, Sawing完後再封裝

5. 晶圓層級(Wafer-Level)

PI 聚亞矽氨

說明:所有封裝在Wafer完成後, 再Sawing

Unimicron Technology (SuZhou) Corp.

Do The Right Things. 13

Unimicron Technology (SuZhou) Corp.

Do The Right Things. 4

常見之封裝形式

二面出腳

DIP 挿件式 ( Dual In-Line Package )

四面出腳

PLCC ( Plastic Leaded Chip Carrier )

SOP SMD device ( Small Outline Package )

Chip

Single Chip Module

Unimicron Technology (SuZhou) Corp.

Chip

Chip

Chip

Chip

Multi Chip Module

Do The Right Things. 15

What is KGD?

* Known Good Die (KGD) is a which has been

1.0/1.27/1.5

Up / Down

Solder Column 10Sn / 90pb

1.0/1.27/1.5

Up / Down Metal Ball Solder / Gold

0.8/0.5

面積效率 7.2

5.3

4.5

(Chip=1)

Unimicron Technology (SuZhou) Corp.

刚挠印刷电路板及封装载板研发制造方案(二)

刚挠印刷电路板及封装载板研发制造方案一、实施背景随着科技的飞速发展,电子产品对高性能、小型化和轻量化的需求日益增强。

刚挠印刷电路板及封装载板作为电子产品中的关键部分,其性能直接影响到产品的整体质量和功能。

我国当前在这方面的技术研发与先进国家相比,还存在一定的差距。

因此,通过产业结构改革,提升刚挠印刷电路板及封装载板的研发和制造能力,对于我国电子产业的发展具有重要意义。

二、工作原理刚挠印刷电路板是一种将刚性电路板和挠性电路板结合在一起的复合板,具有高密度、高可靠性、优良的电性能和机械性能等特点。

而封装载板则主要用于封装芯片,提供电连接和保护功能。

1.刚性电路板部分:利用高分子树脂材料制备基板,通过光刻、刻蚀等手段制作出导电路径,利用电镀或化学镀的方式增加导电层,最后形成具有特定功能的刚性电路板。

2.挠性电路板部分:利用薄膜材料作为基板,同样通过光刻、刻蚀等手段制作出导电路径,利用电镀或化学镀的方式增加导电层,最后形成具有特定功能的挠性电路板。

3.封装载板部分:利用高分子材料制作出封装载体,将芯片封装在载体中,通过引脚或倒装焊等方式与外部电路连接,对芯片起到保护和电连接的作用。

三、实施计划步骤1.技术研究:开展刚挠印刷电路板及封装载板的相关技术研究,包括材料、制造工艺、设计方法等。

2.实验室建设:建立专门的实验室,购置必要的设备和仪器,为研发工作提供硬件保障。

3.方案设计:根据技术研究的结果,设计出具体的研发方案。

4.中试生产:在实验室条件下,进行小批量生产,验证方案的可行性和稳定性。

5.批量生产:经过中试生产的验证和改进后,进入批量生产阶段。

6.市场推广:将产品推向市场,接受用户的反馈和评价,持续改进和优化。

四、适用范围本方案适用于电子产品的制造领域,特别是对于需要高性能、小型化和轻量化的电子产品,如手机、笔记本电脑、平板电脑、数码相机等。

五、创新要点1.材料的创新:采用新的高分子树脂材料和其他薄膜材料,提高电路板的性能和可靠性。

一文看懂半导体制造工艺中的封装技术

一文看懂半导体制造工艺中的封装技术共读好书半导体制造工艺流程半导体制造的工艺过程由晶圆制造(Wafer Fabr ication)、晶圆测试(wafer Probe/Sorting)、芯片封装(Assemble)、测试(T est)以及后期的成品(Finish Goods)入库所组成。

半导体器件制作工艺分为前道和后道工序,晶圆制造和测试被称为前道(Front End)工序,而芯片的封装、测试及成品入库则被称为后道(Back End)工序,前道和后道一般在不同的工厂分开处理。

前道工序是从整块硅圆片入手经多次重复的制膜、氧化、扩散,包括照相制版和光刻等工序,制成三极管、集成电路等半导体元件及电极等,开发材料的电子功能,以实现所要求的元器件特性。

后道工序是从由硅圆片分切好的一个一个的芯片入手,进行装片、固定、键合联接、塑料灌封、引出接线端子、按印检查等工序,完成作为器件、部件的封装体,以确保元器件的可靠性,并便于与外电路联接。

半导体制造工艺和流程晶圆制造晶圆制造主要是在晶圆上制作电路与镶嵌电子元件(如电晶体、电容、逻辑闸等),是所需技术最复杂且资金投入最多的过程。

以微处理器为例,其所需处理步骤可达数百道,而且所需加工机器先进且昂贵。

虽然详细的处理程序是随着产品种类和使用技术的变化而不断变化,但其基本处理步骤通常是晶圆先经过适当的清洗之后,接着进行氧化及沉积处理,最后进行微影、蚀刻及离子植入等反复步骤,最终完成晶圆上电路的加工与制作。

晶圆测试晶圆经过划片工艺后,表面上会形成一道一道小格,每个小格就是一个晶片或晶粒(Die),即一个独立的集成电路。

在一般情况下,一个晶圆上制作的晶片具有相同的规格,但是也有可能在同一个晶圆上制作规格等级不同的晶片。

晶圆测试要完成两个工作:一是对每一个晶片进行验收测试,通过针测仪器(Probe)检测每个晶片是否合格,不合格的晶片会被标上记号,以便在切割晶圆的时候将不合格晶片筛选出来;二是对每个晶片进行电气特性(如功率等)检测和分组,并作相应的区分标记。

一文详解封装制程工艺

点就是制程能力。

SIP封装制程按照芯片与基板的连接方式可分为引线键合封装和倒装焊两种。

引线键合封装工艺工艺流程圆片→圆片减薄→圆片切割→芯片粘结→引线键合→等离子清洗→液态密封剂灌封→装配焊料球→回流焊→表面打标→分离→最终检查→测试→包装。

圆片减薄圆片减薄是指从圆片背面采用机械或化学机械(CMP)方式进行研磨,将圆片减薄到适合封装的程度。

随着系统朝轻薄短小的方向发展,芯片封装后模块的厚度变得越来越薄,因此在封装之前一定要将圆片的厚度减薄到可以接受的程度,以满足芯片装配的要求。

圆片切割圆片减薄后,可以进行划片。

较老式的划片机是手动操作的,现在一般的划片机都已实现全自动化。

无论是部分划线还是完全分割硅片,目前均采用锯刀,因为它划出的边缘整齐,很少有碎屑和裂口产生。

芯片粘结已切割下来的芯片要贴装到框架的中间焊盘上。

焊盘的尺寸要和芯片大小相匹配,若焊盘尺寸太大,则会导致引线跨度太大,在转移成型过程中会由于流动产生的应力而造成引线弯曲及芯片位移现象。

贴装的方式可以是用软焊料(指Pb-Sn 合金,尤其是含Sn 的合金)、Au-Si 低共熔合金等焊接到基板上,在塑料封装中最常用的方法是使用聚合物粘结剂粘贴到金属框架上。

引线键合在塑料封装中使用的引线主要是金线,其直径一般为0.025mm~0.032mm。

引线的长度常在1.5mm~3mm之间,而弧圈的高度可比芯片所在平面高 0.75mm。

键合技术有热压焊、热超声焊等。

这些技术优点是容易形成球形(即焊球技术),并防止金线氧化。

为了降低成本,也在研究用其他金属丝,如铝、铜、银、钯等来替代金丝键合。

热压焊的条件是两种金属表面紧紧接触,控制时间、温度、压力,使得两种金属发生连接。

表面粗糙(不平整)、有氧化层形成或是有化学沾污、吸潮等都会影响到键合效果,降低键合强度热压焊的温度在300℃~400℃,时间一为40ms(通常,加上寻找键合位置等程序,键合速度是每秒二线)。

超声焊的优点是可避免高温,因为它用20kHz~60kHz的超声振动提供焊接所需的能量,所以焊接温度可以降低一些。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3. 卷帶式接合(TAB—Tape Automatic Bonding)—使用金對金熱壓接合

Gold bond

註: TCP ( Tape Carrier Package ) 應用在LCD driver上。 Unimicron Technology (SuZhou) Corp. Do The Right Things.

5.

晶圓層級(Wafer-Level)

說明:所有封裝在Wafer完成後, 再Sawing

PI 聚亞矽氨

Unimicron Technology (SuZhou) Corp.

Do The Right Things.

13

3D Packages

Wireless Bonding ( FCB , others ) Wire Bonding

manufactured and delivered in a bare, or minimally packaged die format, which * has quality and reliability comparable to its functionally equivalent packaged component, * can be interconnected to its next level of packaging by wire bond, tape automated bonding, or flip-chip. 說明: 已知是好的Die封裝進度, Wafer sawing 無法100% 檢出IC是好是壞? 原因:

3. 協助排除耗熱 4. 保護電子零件 5. 建構人機介面

Unimicron Technology (SuZhou) Corp.

Do The Right Things.

4

常見之封裝形式

二面出腳

DIP 挿件式 ( Dual In-Line Package )

四面出腳

PLCC ( Plastic Leaded Chip Carrier )

5

單晶片構裝之基本結構

膠體 ( Epoxy Molding Compound )

晶片(Chip) 金線(Gold Wire) 引腳(Lead)

晶片座(Die Pad)

銀膠(Silver Epoxy)

優點:膠體對稱,不易產生翹曲

Unimicron Technology (SuZhou) Corp. Do The Right Things.

9

單晶片構裝之演變

PTH → SMT → Area Array → Fine Pitch Area Array

Direct Chip Attach on Board * 一定要使用較小的 IC (CTE過大易裂 )

Chip Scale Package

BGA

Wire Bond ↓ Flip Chip 的應用

Plastic Tape Ceramic

類別 基板 膠體結構

PBGA

BT樹脂 Over mold Glob Top Cap 7~50 mm Up / Down Solder Ball 63Sn / 37pb 1.0/1.27/1.5 7.2

TBGA

Polyimide Optional Cap

CBGA

21~40 mm Up Solder Ball 10Sn / 90pb 1.0/1.27/1.5 5.3

18~32 mm Up / Down Solder Ball 10Sn / 90pb 1.0/1.27/1.5 4.5

32~42.5mm Up / Down Solder Column 10Sn / 90pb 1.0/1.27/1.5 4.5

4. 無引腳 (Non Lead)

QFN(Quad Flat Non-lead)

5. 晶片座 (Die Pad)

優點:1. 散熱能力佳

2. 面積小(無須預留接腳空間)

3. 傳輸距離短 4. 無腳彎翹風險 缺點:Molding 困難度較高 (不對稱,易發生翹曲 ) Unimicron Technology (SuZhou) Corp.

多層陶瓷 Optional Cap

CCGA

多層陶瓷 Optional Cap

Micro BGA

Optional Over mold Glob Top Optional Cap Chip Scale Up / Down Metal Ball Solder / Gold 0.8/0.5 1~1.4

膠體尺寸 晶片方向 錫球 間距 面積效率 (Chip=1)

6

BGA(Ball Grid Array)構造

Second bonding Bonding pattern Solder resist Chip First bonding Mold compound Ag paste

Gold wire

Ground Solder balls

Solder pattern Thermal via hole

SOP SMD device ( Small Outline Package )

QFP ( Quad Flat Pack )

SOJ ( Small Outline J-Lead )

PGA ( Pin Grid Array )

PBGA (Plastic ball Grid Array)

Unimicron Technology (SuZhou) Corp. Do The Right Things.

模組板

Module board

主機板(母板)

Mother board

多晶片模組

( MCM : Multi-Chips

Module )

Unimicron Technology (SuZhou) Corp.

Do The Right Things.

3

電子構裝之主要功能

1. 有效供應電源

2. 提供信號傳輸

* CSP is derived from existing packages, that is, it can be any type of packages.

覆晶(Flip Chip) 技術

*

表面黏著技術 (Surface Mount) Chip Scale 構裝

*

Silicon

標準化 定義:

小尺寸

De-Taping

Singulation Wafer Sawing

Substrate pre-bake

Molding

Top Marking & Curing

(Punch or Routing)

Die Bonding

Curing

Ball Mount

Ball Scan

應用產品:電腦、通訊、電子消費性產品

所需技術

電子、機械、物理、化學、材料、光學、可靠性工程、人 因工程…等多重之工程技術。

Unimicron Technology (SuZhou) Corp. Do The Right Things.

2

電子構裝之分級

晶圓(Wafer) → 晶片(Chip) →第一階層封裝 → 第二階層封裝 → 第三階層封裝 單晶片構裝

Do The Right Things.

17

PBGA Assembly Process

Wafer Incoming

Taping

Wire Bonding

Interconnecting 完成 O/S Test or 3rd Vision Insp. Plasma Clean

Flux Clean

Wafer Grinding

PGA TO 1970 DIP QFP 1980

TCP

1.電訊上的考慮(速度、 傳輸路徑短 ) 2. IO數的考量(IO數 較Ball Pad受限) 1990 2000 2010

Unimicron Technology (SuZhou) Corp.

Do The Right Things.

10

BGA構裝之分類

Chip Chip Chip

Chip

Chipቤተ መጻሕፍቲ ባይዱ

Single Chip Module

Multi Chip Module

Unimicron Technology (SuZhou) Corp.

Do The Right Things.

15

What is KGD?

* Known Good Die (KGD) is a which has been

Unimicron Technology (SuZhou) Corp.

Do The Right Things.

11

CSP(Chip Scale Package)

* Definition: Chip scale package (CSP) is a package whose package-to-silicon area ratio less than 120 percent.

1.

2.

檢驗困難度高

成本貴

大部份的是IC封完後測出IC是好是壞?

Unimicron Technology (SuZhou) Corp. Do The Right Things.

16

封裝製程介紹

IC Assembly Process Introduction

Unimicron Technology (SuZhou) Corp.

12

CSP之分類

1. 硬板中介層(Rigid Substrate Interposer)

2.

導線架形式(Leadframe Type)

3.

軟板中介層(Flex circuit Interposer)

4.

無中介層, 壓模成型(Transfer Molding)